1 platform

分为hw platform 和 sw platform

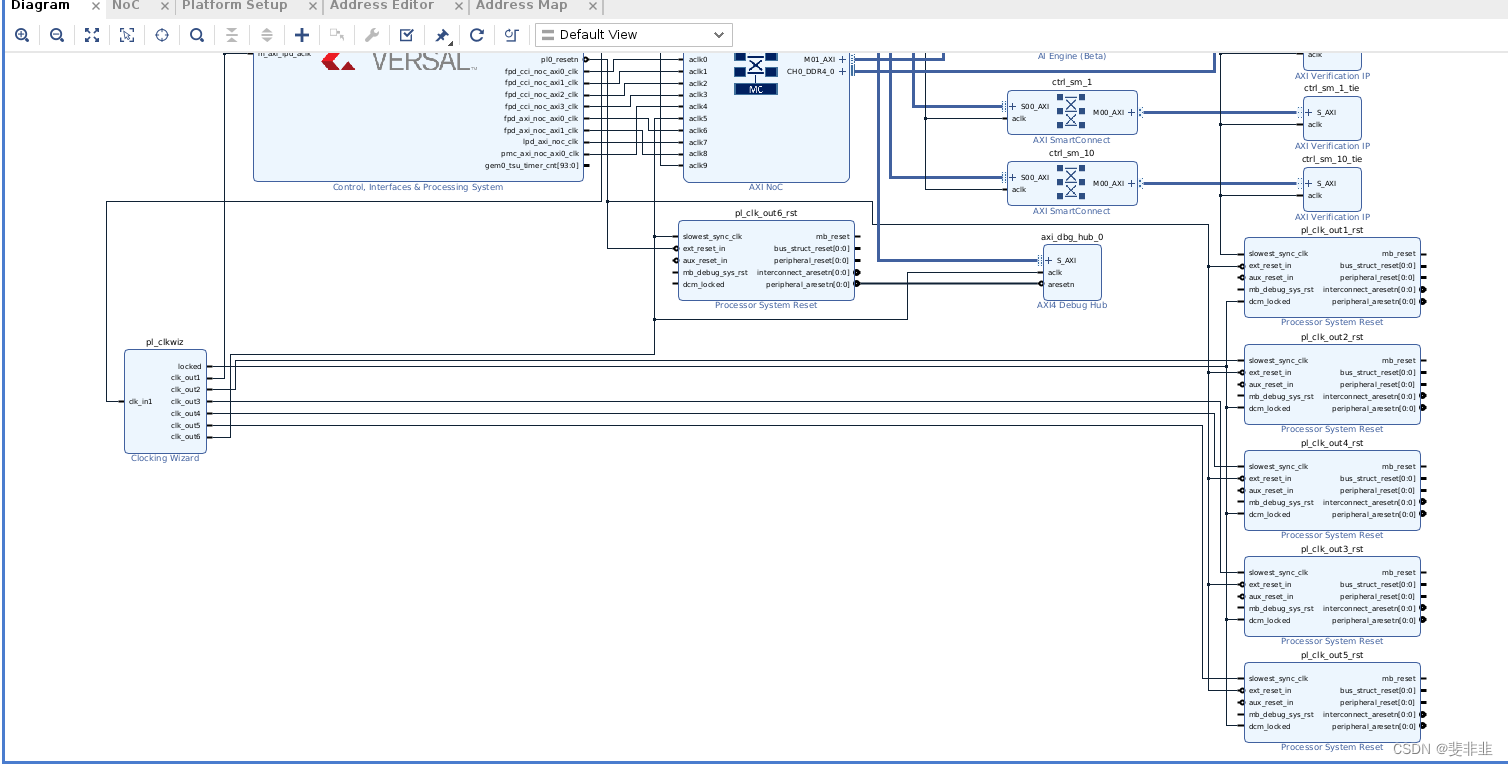

This is in most ways a traditional Vivado design. You are building the platform, that is, the part of the design that you do not want the Vitis tools to configure or modify. This can include completely unrelated logic, any hierarchy you want to have in the design, but there are some rules that you must follow:

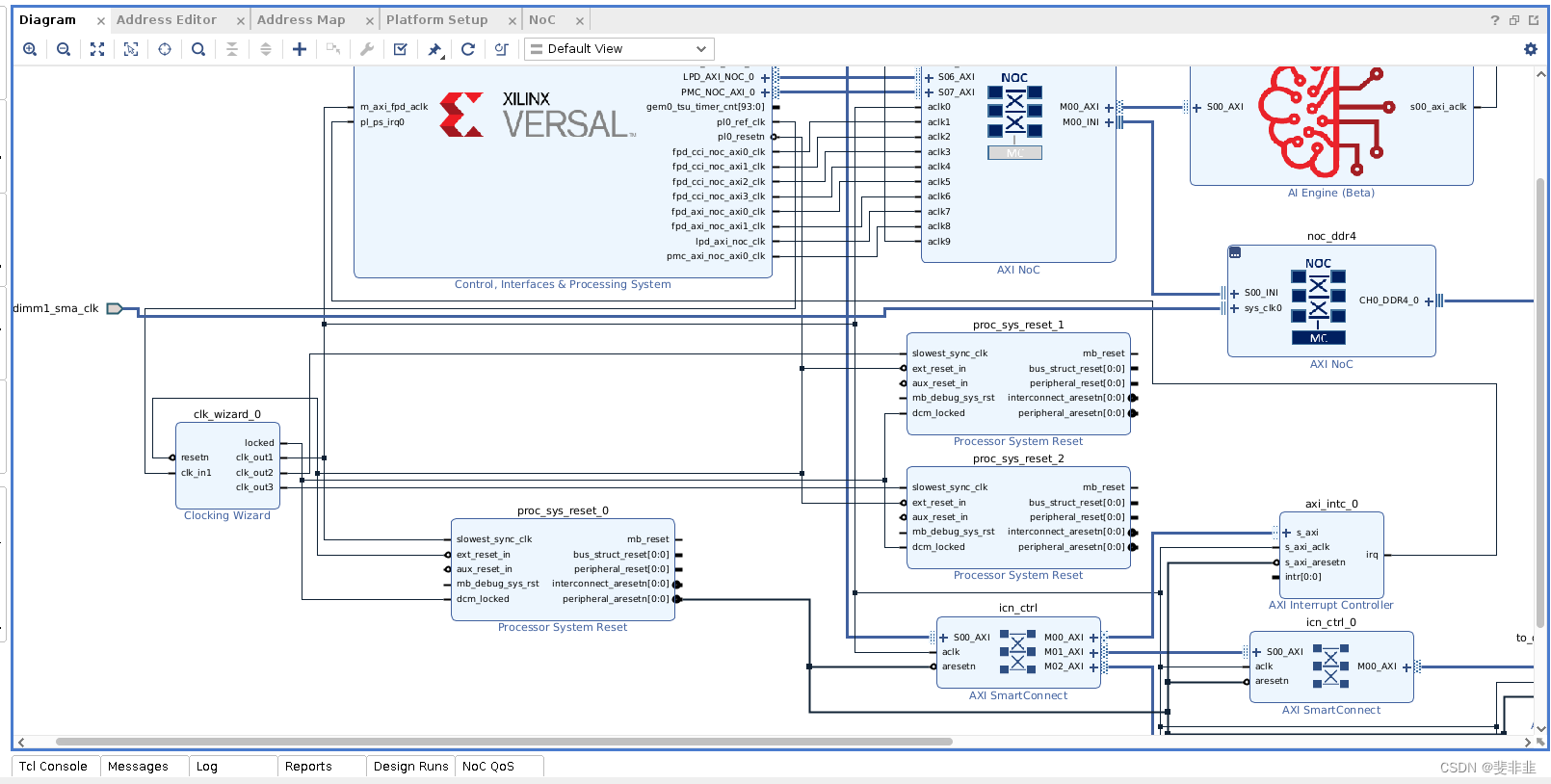

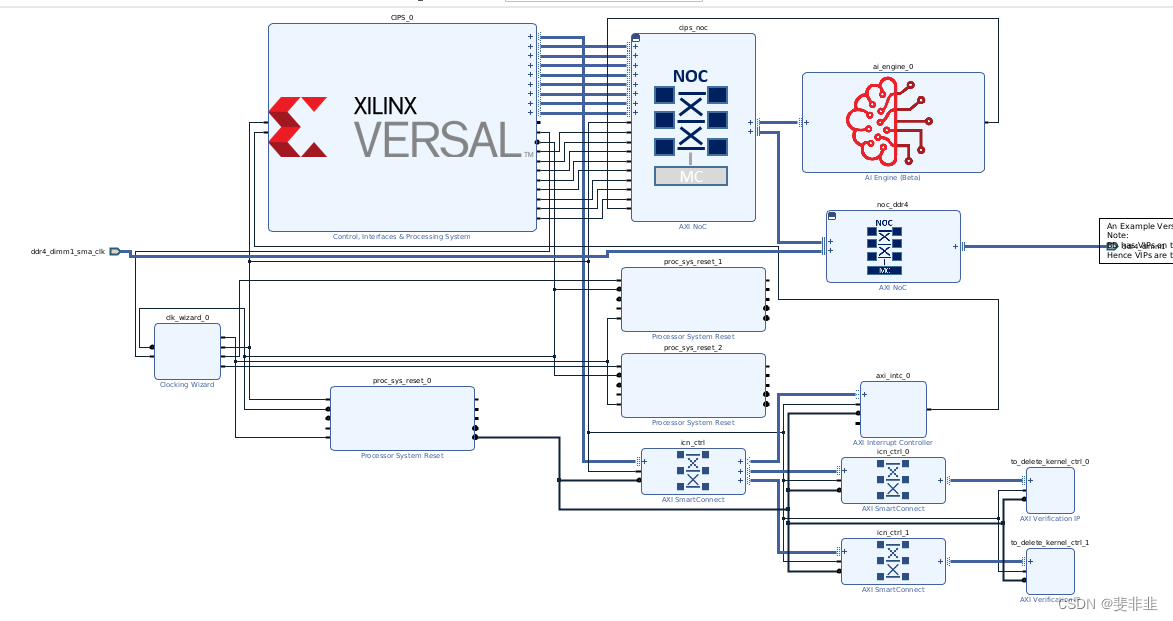

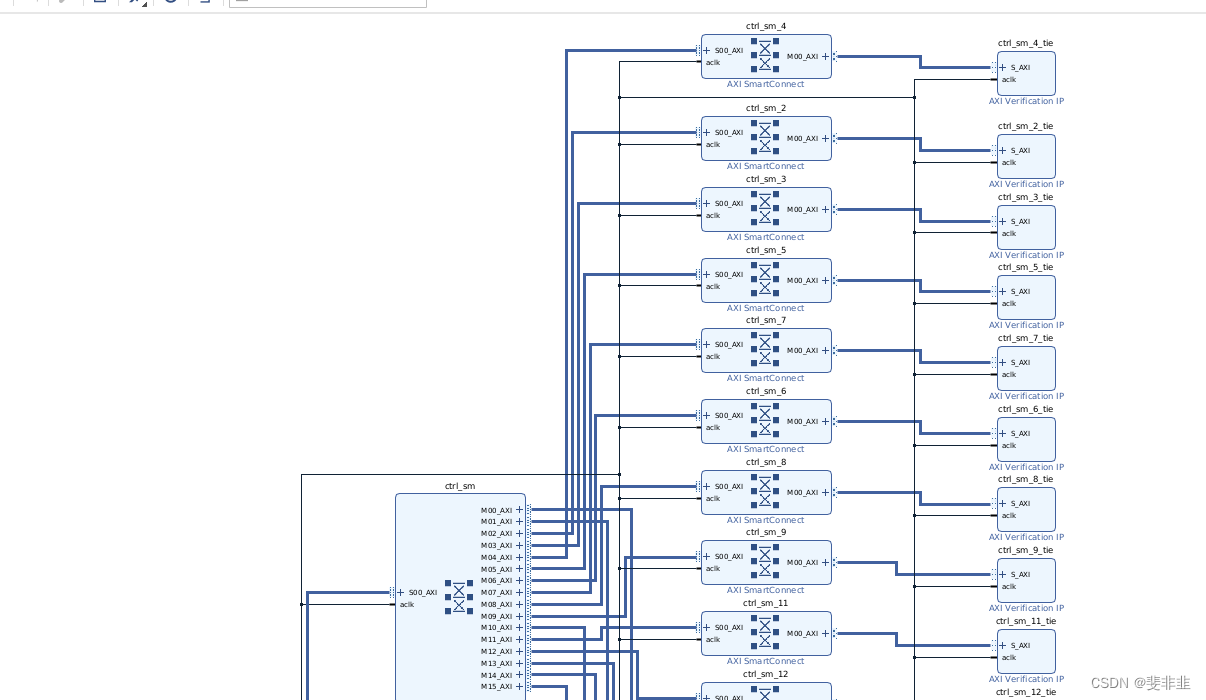

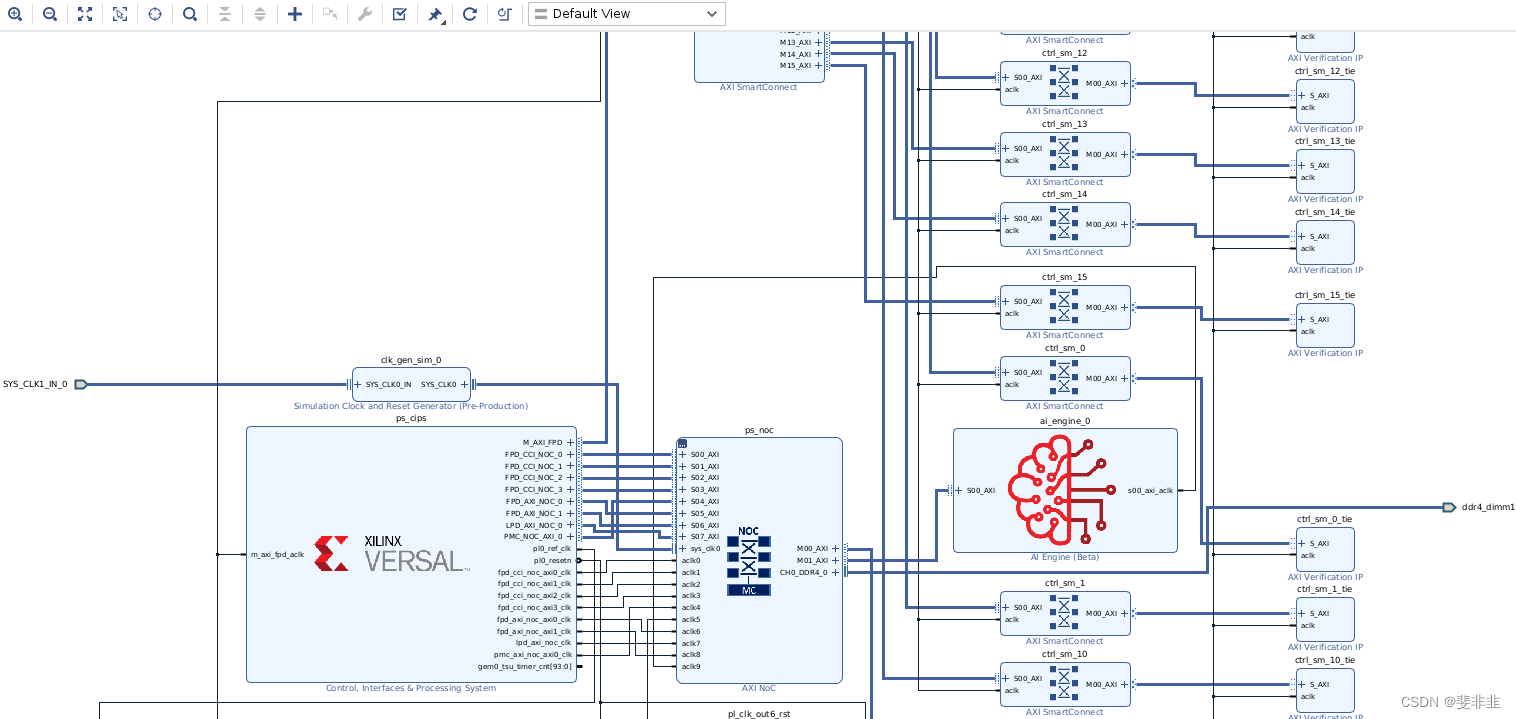

- Your design must contain an IP integrator block diagram containing the CIPS, NOC, and other infrastructure IP

- Your design must have at least one clock that you will expose to Vitis for use with any kernels that it adds This clock must have an associated proc_sys_reset block.

2. aie application

3. PL application

add PL kernels in HLS into the system project and build the whole system.

Add PL Kernels

In this example, HLS kernels are used which bridge between memory and the AXI4-Stream interface to input and output data from memory.

The mm2s kernel reads data from memory and inputs it to the AI Engine array.

The s2mm kernel receives output data from the AI Engine array and writes it to memory.

2322

2322

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?