1,set_input_delay约束理解

input_delay是指输入的数据到达FPGA的pad引脚时相对于时钟边沿的延迟有多大,单位是ns,数值可以是正,也可以是负。通过set_input_delay约束告诉编译器输入时钟和输入数据的相位关系。如下图所示假设时钟是没有skew的,那么下图中的input_delay就等于Clock to Out+Trace Dealy,即上游器件的时钟到触发器输出的延时+PCB上的布线延迟,即Tco+Tdelay。

2,具体案例

2.1,input delya min设置

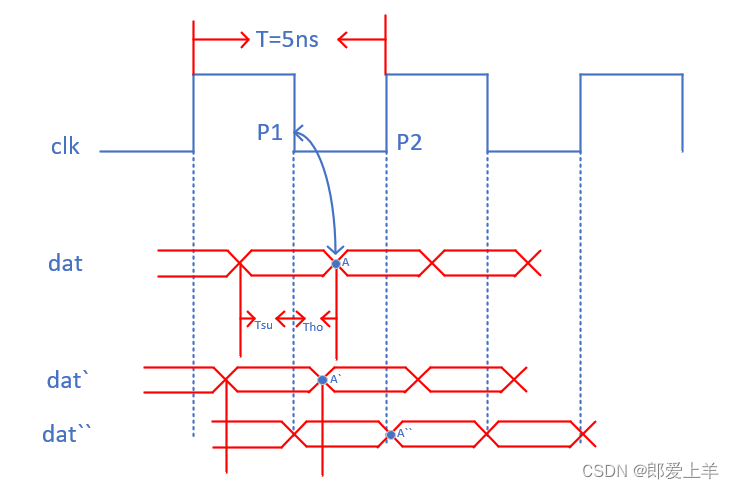

以LVDS输入为例子,LVDS双边沿采样,时钟周期为T=5ns,假设上游器件 建立时间Tsu=1.5ns,保持时间Tho=1.2ns,那上游器件的建立和保持时间会存在如下对应关系:

从图中可以看出,数据相对于时钟的最小延时min=Tho,即P1到A点的时间长度刚好满足上游器件的保持时间:

set_input_delay -clock clk -min 1.2 [get_ports dat]

假如约束的最小值min<Tho,会出现如下图示情况:即P1到A`点的时间长度不满足上游器件的保持时间:

综合上述两图,input delay最小的延时时间就是上游器件的保持时间。

2.2,input delya max设置

数据dat往后延时最大值不能超过P2的时间边沿,如超过P2边沿,即max> T/2 - Tho,会出现如下情况(双边沿是T/2,单边沿就是T):

A``不能满足满足上游器件的建立时间,

综合上述两图,input delay最大的延时时间就是上游器件的T/2 (双边沿)减去 保持时间。

min delay ~ max delay就是数据抖动时间

1136

1136

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?