IC君的第40篇原创文章 (欢迎关注公众号 icstudy)

一年一度的五一劳动节又到了,常常加班不止996的ICer又可以好好休息一下了,首先IC君祝大家劳动节快乐!

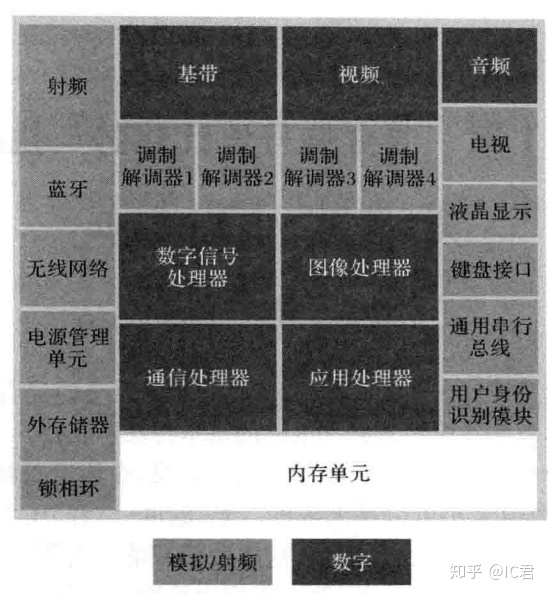

大家都知道对于一颗有点复杂度的芯片而言(比如SOC),通常都会包含数字电路和模拟电路。在设计的初期,也许数字模块和模拟模块是分开设计和仿真的。随着项目的推进,需要将这些模块都集成到一起,形成最终tapeout的芯片。

以前也写过一篇文章IC君:新入职IC工程师必备技能——数模混合篇

如何保证数字电路和模拟电路之间的连接性和协同工作的表现呢?

做仿真呗~

废话,当然要做仿真,要做什么仿真呢?

包含数字电路和模拟电路的数模混合仿真。

数模混合仿真顾名思义包括数字电路仿真和模拟电路仿真。那数字电路仿真和模拟电路仿真又是如何定义的呢?

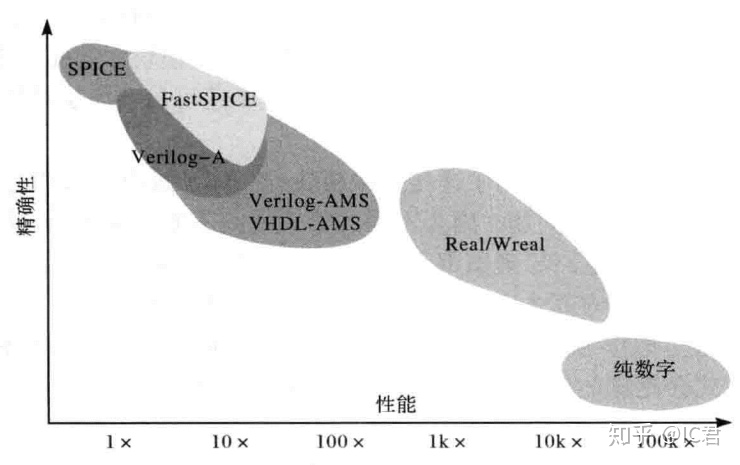

数字电路的仿真建模:verilog、system verilog、VHDL等等;

模拟电路的仿真建模:spice、verilog-A/AMS、VHDL-AMS、Real/Wreal、行为模型等等.

数字电路的仿真是以verilog为代表的,模拟电路的仿真有多种选择,最终数模混合有多种方式。这篇文章重点讨论verilog和spice的数模混合仿真方法。

常

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2681

2681

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?