A/D 和 D/A 接口信号转换

接口信号是指处于数模边界上的信号。

在Verilog-AMS-SPICE flow中,通过“Connect Modules”完成A/D 和 D/A转换。

在Verilog-SPICE 和 VHDL/Verilog-SPICE flow中,工具自动插入接口组件。

在VCS工具中使用-realport选项,可以在Verilog-SPICE flow中实现e2r (electrical to real) 或 r2e (real to electrical)信号转换。

接口组件自动插入准则

- 接口信号可以是单向的,即要么a2d,要么d2a

- 接口信号可以是双向的,即inout类型,仿真过程中可以在a2d和d2a两种状态间切换

- 接口信号方向由verilog端口确定

- 如果SPICE下例化verilog,则verilog的管脚定义决定接口信号方向

- 如果verilog下例化SPICE,同时该SPICE电路还有verilog形式的描述,则verilog描述中的管脚定义决定接口信号方向

- 如果verilog下例化SPICE,但SPICE电路没有verilog形式的描述,则接口信号全部为inout类型

- d2a转换中,默认高低电平是VDD和0V,可在d2a指令中修改

- a2d转换中,默认门限是50%的VDD,可在a2d指令中修改

- d2a转换中,用理想的源来模拟数字驱动

- a2d转换中

- 如果接口是单向的a2d类型,那么用驱动能力为6的数字驱动来表示模拟驱动

- 如果接口是双向的,那么仿真器将计算模拟驱动的输出电阻,然后映射到相应驱动能力的数字驱动

- 根据输出电阻估算驱动能力非常耗时,因此可以在a2d指令中使用

hiz_off选项来取消驱动能力计算

- 阻性元件(MOS晶体管的等效通道电阻和/或理想电阻):接馈电电源或接地的的线网输出电阻

- 在a2d转换中,计算Verilog驱动强度时忽略电路内部端口的BJTs、二极管或耦合电容的影响。

Verilog-to-SPICE 和 SPICE-to-Verilog 信号转换

转换信号值

d2a中转换信号值

| verilog值 | 晶体管电平值 |

|---|---|

| 0 | 0V, 或 VDD电压的某个比例(动态馈电情况下) |

| 1 | 馈电电压,或 VDD电压的某个比例(动态馈电情况下) |

| Z | 模拟节点不受Verilog驱动,节点的电压完全取决于模拟电路 |

| X | 0V |

a2d中转换信号值

| 晶体管电平值 | verilog值 |

|---|---|

| ≤ 低电压门限 | 0 |

| ≥ 高电压门限 | 1 |

| 接口是双向的,或者接口驱动能力计算得出模拟节点为HiZ | Z |

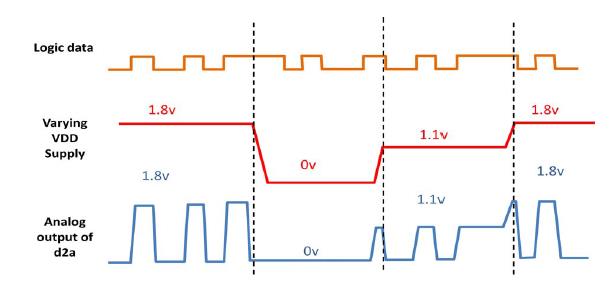

模拟动态馈电

在一些场合,馈电电压可能随着时间改变(如某模块时而断电,时而恢复供电)。为模拟这种行为,需要使用a2d和d2a指令的vdd选项,将电压门限设置为馈电电压的某个比例,比如设置

a2d loth=20% hith=80% node=top.i1.clk vdd=top.i2.vdd;

d2a hiv=100% lov=0% node=top.i1.rst vdd=top.i2.vdd;

转换信号强度

| Verilog strength level | purpose | Logic 0 keyword | Logic 1 keyword |

|---|---|---|---|

| 7 | Supply drive | supply0 | supply1 |

| 6 | Strong drive | strong0 | strong1 |

| 5 | Pull drive | pull0 | pull1 |

| 4 | Large capacitive | large | large |

| 3 | Weak drive | weak0 | weak1 |

| 2 | Medium capacitive | medium | medium |

| 1 | Small capacitive | small | small |

| 0 | High impedance | highz0 | highz1 |

当同一条线网上出现多个驱动时,驱动能力最强的决定线网的信号值。a2d转换时,默认驱动能力为6。

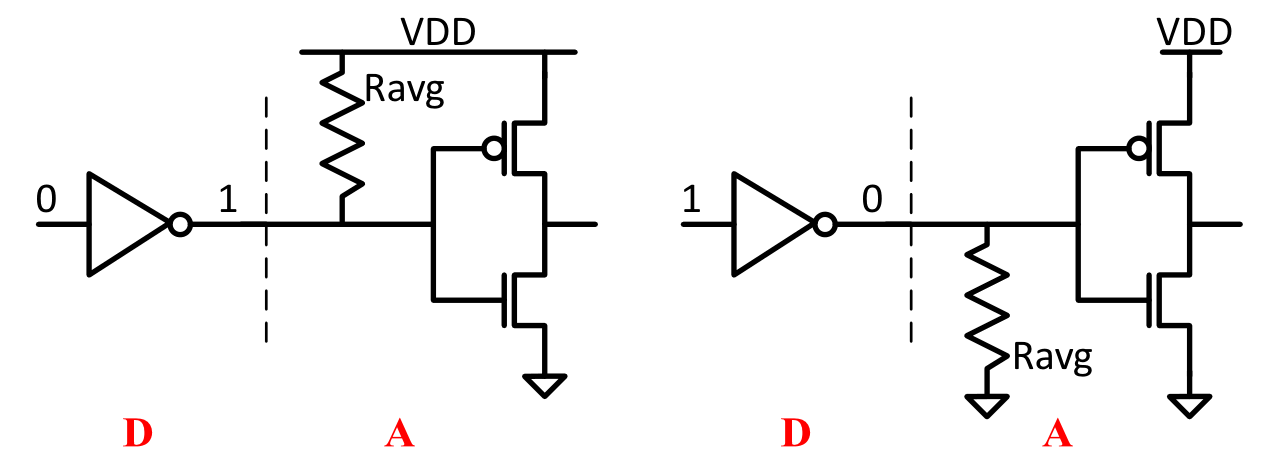

d2a转换时计算电阻

为了模拟d2a转换的verilog驱动能力,可以通过电阻映射文件(resistance map file)计算得到等效电阻。默认情况下,工具会从安装目录下读取 rmapAD.init 文件,通过数字驱动强度值,查找到对应电阻值区间,并对该区间取平均,作为该驱动强度的电阻值。例如:

// Example rmapAD.init Resistance Map File

resistance_map 90000.2-1e32 0 ;

resistance_map 70000.2-90000.2 1 ;

resistance_map 50000.2-70000.2 2 ;

resistance_map 7000.2-50000.2 3 ;

resistance_map 6000.2-7000.2 4 ;

resistance_map 1000.2-6000.2 5 ;

resistance_map 1.2-1000.2 6 ;

resistance_map 0-1.2 7 ;

那么驱动强度为6所对应的阻值: Ravg = (1.2 + 1000.2) / 2 = 500.7

如果希望工具读取自定义的电阻映射文件,在 rmapAD.init 文件中添加 rmap_file ./rmapADcustom.init; 即可。

d2a转换举例

a2d转换时计算强度

通过查找电阻映射文件,模拟端电阻值落在哪个区间,对应数字驱动强度值就为几。

a2d和d2a转换时分别使用不同的映射电阻值

resistance_map -from analog 90000.2-1e32 -to verilog 0;

resistance_map -from analog 70000.2-90000.1 -to verilog 1;

resistance_map -from analog 50000.2-70000.1 -to verilog 2;

resistance_map -from analog 5000.2-50000.1 -to verilog 3;

resistance_map -from analog 4000.2-5000.1 -to verilog 4;

resistance_map -from analog 3000.2-4000.1 -to verilog 5;

resistance_map -from analog 1.2-3000.1 -to verilog 6;

resistance_map -from analog 0-1.1 -to verilog 7;resistance_map -to analog 2002.2-1e32 -from verilog 0;

resistance_map -to analog 1500.2-2002.1 -from verilog 1;

resistance_map -to analog 1000.2-1500.1 -from verilog 2;

resistance_map -to analog 500.2-1000.1 -from verilog 3;

resistance_map -to analog 400.2-500.1 -from verilog 4;

resistance_map -to analog 300.2-400.1 -from verilog 5;

resistance_map -to analog 1.2-300.1 -from verilog 6;

resistance_map -to analog 0-1.1 -from verilog 7;

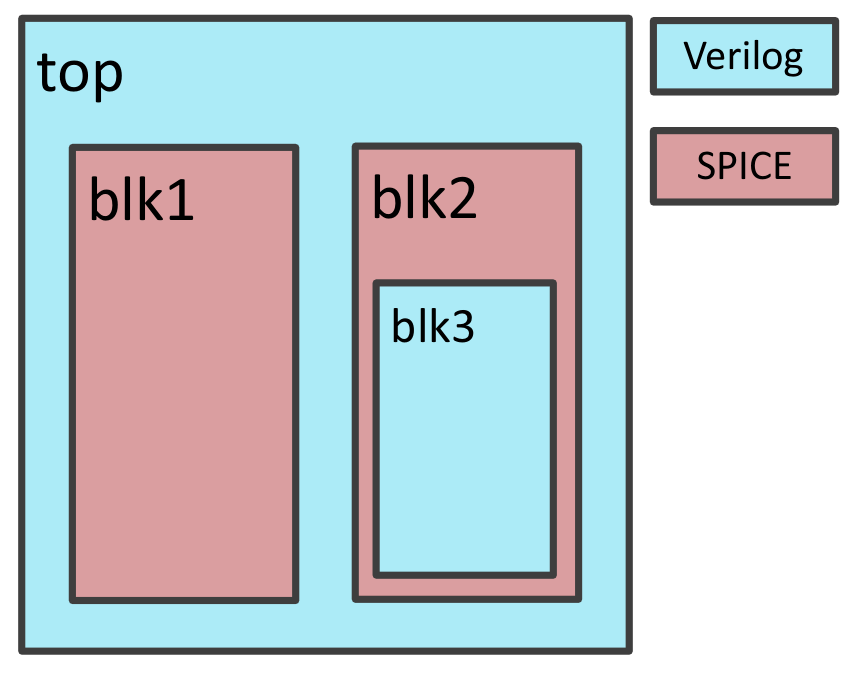

Verilog-Top/SPICE-Top flows

如果设计的顶层是SPICE网表,则称这个设计是SPICE-Top的。

同理,如果设计的顶层是Verilog、VHDL或Verilog-AMS,则称这个设计是Verilog-top, VHDL-top或Verilog-AMS-top的。

在SPICE-top的配置中,必须在 vcsAD.init 文件中添加 spice_top 指令。

在Verilog-top或者VHDL-top配置中,无需添加特殊指令。

Donut 配置

如果一个设计中,在verilog的顶层下面例化了SPICE网表,那么可以称这种结构为 Verilog-SPICE donut 配置。下图展示了一个Verilog-SPICE-Verilog donut 配置。

Nettype flow 中有多个 cell 视图

看不懂,暂时略

同步模拟和数字的事件

若要同步模拟和数字的事件,理论上数字域和模拟域的时间精度(仿真器使用的最小时间步长)需要一致。

通常,模拟时间精度不能大于数字时间精度,否则可能发生同步失调导致运行失败。同时,模拟时间精度也不能小于数字时间精度,否则模拟仿真器运行太慢(除非对准确度确实有更高要求)。

-

使用VCS AMS工具时,不会发生同步失调问题,因为CustomSim会自动调整模拟时间精度完成同步。

-

使用FineSim工具时,建议修改数字时间精度

vcs -ad -override_timescale=1ps/0.1ps

当然,也可以修改模拟时间精度:

.option finesim_tunit=0.1ps

-

使用HSIM工具时,HSIM会使用数模时间精度小的一方作为运行时精度。例如数字时间精度0.01ps,模拟时间精度0.1ps,则HSIM时间精度为0.01ps。如果数字时间精度1ps,模拟时间精度0.1ps,那么HSIM时间精度为0.1ps,但是,VCS(数字工具)采用的时间精度仍然是1ps(也就是说模拟时间精度会比数字时间精度小)。

例化Verilog-A 模型

首先使用.hdl指令读入Verilog-A文件。

然后,对于HSIM工具,使用.param HSIMUSEVA=module_name指令选择Verilog-A view;对于CustomSim工具,使用set_va_view指令选择Verilog-A view。

3191

3191

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?