T1:时钟延迟(已知)

T_cycle:时钟周期(已知)

△T=T3-T2(已知)时钟偏斜

建立时间 :Ts=T_cycle-T1+△T

建立时间约束(Tsetup),建立时间余量Tslack=Ts-Tsetup

保持时间:Th=T1-△T或者Th=T_cycle-Th

保持时间约束(Thold),保持时间余量Thslack=Th-Thold

影响因素:△T过大,影响保持时间,T1过大,影响建立时间

器件决定建立时间和保持时间门限。

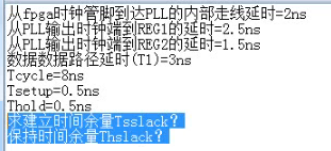

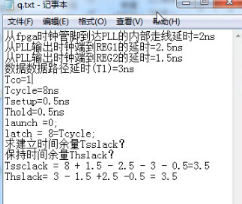

T1=3ns,T2=2.5ns,T3=1.5ns T=2ns Tcycle=8ns,Tsetup = 0.5ns,Thold =0.5ns

Tsslack=Tcycle-T1+(T3-T2)-Tsetup=8-3+(1.5-2.5)-0.5=3.5ns

Thslack=T1-(T3-T2)-Thold=3.5ns

另一种计算方法:

建立时间的余量=数据要求时间-数据到达时间

=(8+1.5-0.5)-(2.5+2+1)=3.5ns

2.13 10:30打卡下班

2.13 10:30打卡下班

2.14 9:00打卡上班

课堂作业:viso波形工具画图

等加群做案例,现去看看至芯直播课

下午学习时序分析的实际案例:

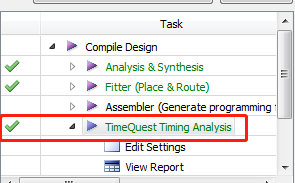

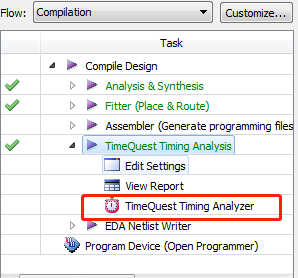

主要是应用TimeQuest

1.双击打开

界面如下:

![]()

![]()

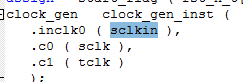

由程序可知,需要约束的时钟sckin

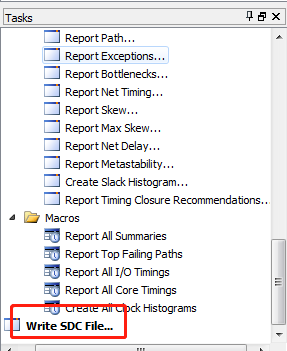

最后

生成

生成

打开后,可知道

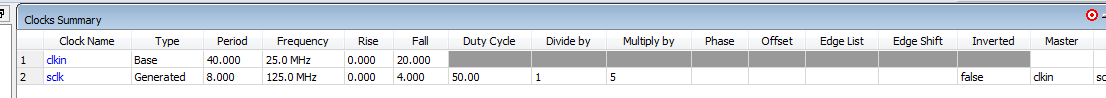

再来看看程序的锁相环

sclk 是由clk_in 5倍频来的,也要对其进行约束

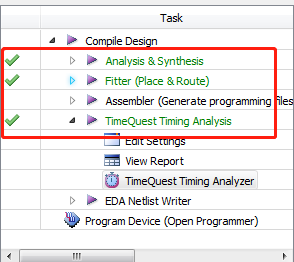

在重新综合布线时序分析

sclk_in没有timing,sclk有

随便点一路经延迟,可以观察走线信息

指出了每一部分具体的延迟时间

关键路径是在布局布线好的情况下,时间余量最小的就是关键路径;

继续分析

尝试改变时钟频率

重新编译

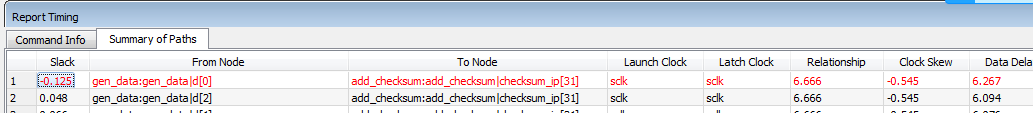

现在可以看到slack都变红了

下面开始消除违规

优化参数和修改代码的方式消除

1)软件消除

并未使能signalTap

2)优化方式

比如:

当我们选择area时,slack小一些

改变此数字,可看到明显的变化

现在就是通过软件的试错,修改到只有60个违规

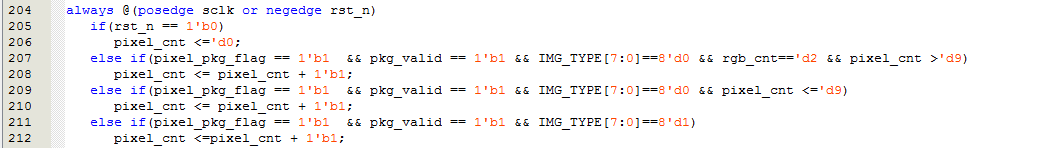

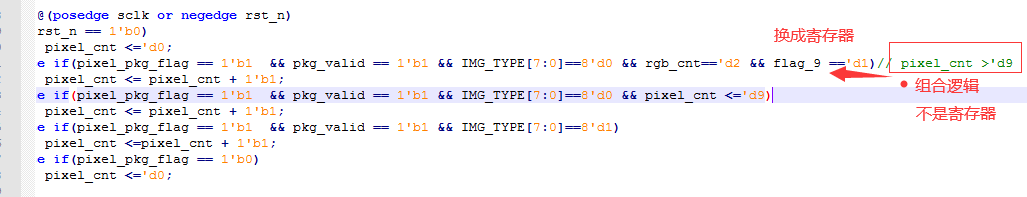

代码更改:

根据最长延迟,可定位到代码的部分,分析代码的走线,更改代码,使其消除

如定位代码

分析代码

目的:之前的比较是组合逻辑

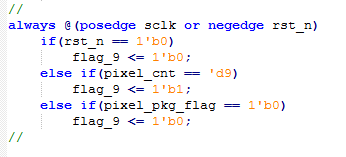

寄存机标志:flag_9;

现在观看变化:并没有太多变化;

不过,可以看出基本的方法就是插入寄存器,打断路径。

不过,自己根据自己的代码,做出调整,发现:违规还是10个

现在,还有1条

大的case消化时间,可分为小的case

瞬时时序违规没有了:

具体方法:把整个case分成两个小的case语句。

时序课程基本结束,下面会做补充。

7915

7915

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?