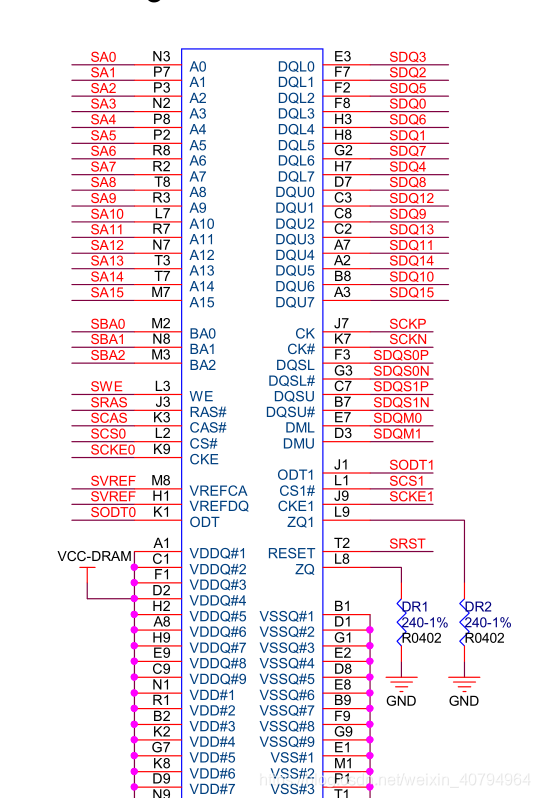

在最近的项目中接触到DDR3的电路,看到DDR的DQ数据线和SOC的DQ数据线并不是按顺序依次连接的。

如图:

在目前的嵌入式产品设计中,DDR/DDR2/DDR3 SDRAM已经成为各种CPU、ASIC的基本组成单元。 在PCB设计过程中,为了布线方便,减少走线交叉,经常会调整DQ数据线信号的顺序,一般的原则如下:

1. bytelane内部8根数据线可任意调整,

2. bytelane与bytelane之间也可以调整,但必须是整体调整, 注:bytelane包括DQ、DQS和DM,三种信号线必须对应一致。

原因:SDRAM只是单纯的用于CPU数据存取,不带内部命令解析,即使顺序调整,也可以保证CPU存入到SDRAM的数据再次读出来时顺序与写入顺序一致。 所以判断数据线顺序是否可以调整的最基本原则就是保证读出顺序和写入顺序一致,并且从设备不带内部命令解析。

违反上述两者中的任何一条,都会导致逻辑混乱,功能错误。 举例说明 :

1. Cavium的Video Codec ASIC外置RAM不支持线序调整,

2. 一般的CPU外接RAM均支持线序调整,如ARM等。

DDR3 SDRAM在PCB设计中,DQ数据线顺序可调整以优化布线,保持读写顺序一致。调整原则是保证数据线内部8根线及byte lane间整体调整,确保CPU存取数据的顺序一致性。某些ASIC如Cavium的VideoCodecASIC不支持线序调整,而大多数CPU如ARM则支持。

DDR3 SDRAM在PCB设计中,DQ数据线顺序可调整以优化布线,保持读写顺序一致。调整原则是保证数据线内部8根线及byte lane间整体调整,确保CPU存取数据的顺序一致性。某些ASIC如Cavium的VideoCodecASIC不支持线序调整,而大多数CPU如ARM则支持。

73

73

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?