一、晶体管与MOS管并联理论:

(1)、晶体管具有负的温度系数,即当温度升高时,导通电阻会变小。

(2)、MOS管具有正的温度系数,即当温度升高时,导通电阻会逐渐变大。

相比于晶体管,MOS管的特性更加适合并联电路中的均流,因此当电路中电流很大时,一般会采用并联MOS管的方法来进行分流。采用MOS管进行电流的均流时,当其中一路电流大于另一路MOS管中的电流时,电流大的MOS管产生的热量多,从而引起导通电阻的增大,减少流过的电流;MOS管之间根据电流大小的不同来反复调节,最后可实现两个MOS管之间的电流均衡。

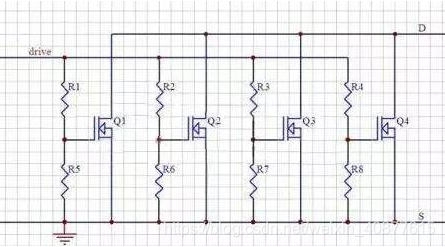

注:晶体管也可以通过并联来实现大电流的流通,但是此时需要通过在基极串接驱动电阻来解决各个并联晶体管之间的电流均衡问题。

二、晶体管(MOS管)并联注意事项:

(1)、各个晶体管(MOS管)的基极(栅极)不能直接相连,要分别串接驱动电阻进行驱动,以防止振荡。

(2)、要控制各个晶体管(MOS管)的开启时间和关断时间保持一致,因为如果不一致,先开启的管子或后关断的管子会因电流过大而击穿损坏。

(3)、为了以防万一,最好在各个晶体管(MOS)管的发射极(源极)串接均流电阻,当然这并非强制选项。

(4)、各个并联的晶体管(MOS管)之间要注意热耦合,因为电流集中在一方管子的主要原因就是由发热引起的。

三、晶体管(MOS管)并联应用:

(1)、功率开关MOSFET的集成IC芯片,其内部是将大量的小MOS管并联连接起来的,这样每一个MOS管单元中流过的电流很小,防止局部的电流集中(若电流局部集中,则器件就损坏),但是电路总体可以通过较大的电流,非常适合驱动电机等重负载设备。当然多个MOS管并联还可以改善高频特性,这已经成为目前功率开关MOS管的主要结构。

(2)、电池等供电设备是移动设备获取电力的主要来源之一,但是一般的高功率电池供电电流都非常大(功率使用可以达到100A),因此仅仅使用单MOS管作为开关器件还不能满足大电流的应用目的,这时多个MOS管并联便能大展身手了。

(3)、功率放大电路(射极输出电路)需要驱动较大功率的负载设备,这时单个晶体管(MOS管)的流通电流能力有限,远远实现不了大功率设备(100W,1000W等等)的驱动能力;而采用多管并联可以解决这一难题。

本文详细解析了晶体管与MOS管并联的理论基础,包括两者不同的温度系数特性,以及MOS管在并联电路中实现电流均流的优势。同时,文章还介绍了并联晶体管或MOS管时需要注意的关键事项,如基极或栅极的驱动、电流均衡电阻的使用,以及热耦合的重要性。最后,文章列举了并联晶体管或MOS管在功率开关IC、电池供电设备和功率放大电路中的具体应用。

本文详细解析了晶体管与MOS管并联的理论基础,包括两者不同的温度系数特性,以及MOS管在并联电路中实现电流均流的优势。同时,文章还介绍了并联晶体管或MOS管时需要注意的关键事项,如基极或栅极的驱动、电流均衡电阻的使用,以及热耦合的重要性。最后,文章列举了并联晶体管或MOS管在功率开关IC、电池供电设备和功率放大电路中的具体应用。

1556

1556

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?