More articles You can follow the official account:“IC练习生”

IC民工不定期更新

使用 Tessent shell的memlibCertify引擎验证TCD Memory library文件

用Tessent MemoryBist工具实现存储器的内建自测试需要特殊的memory模型,通常为Memory的库文件或者memory的TCD文件.这种抽象模型需要去形容测试向的存储器属性帮助工具提高测试覆盖率;

memlibCertify验证主要是验证内存的测试属性是否正确定义,并且与内存的行为模型一致;

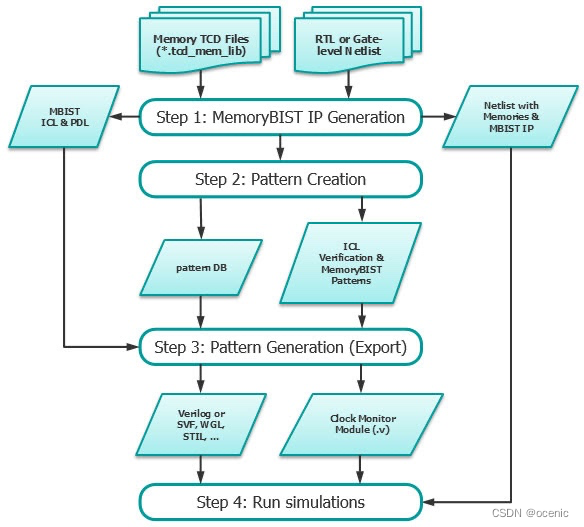

Pattern Generation

Tessent MBIST对于block,core或者top_level design的pattern的生成方式相似;

通常只在block&core level生成verilog的testbench;因为这部分电路通常会在更高的层次实例化调用,因此无需再这些level上生成manufacturing test pattern;

在顶层 在sign-off设计之后生成Verilog testbench ,测试机的测试向量随后产生,作为硅器件的manufacture测试;

在自底向上的设计流程中,在他们整合到更高层的设计中之前,低层次的 MBIST插入都会做独立的完整的验证.这种层次化的DFT的方法,使得可以在更小的设计部分中完成MBIST的插入,即使其他设计部分还没准备好.因为MBIST 仅需要一个时钟和一个低速的串行测试接口就可以运行;将已经插入MBIST的block整合在顶层进行验证是很容易的.

在自上而下的流程中,MBIST 插入在整个设计中一次完成。与层次化 DFT 插入相比,这种方法总体上需要的步骤更少,但是 MBIST 插入必须在整个设计中进行验证,然后才能sign-off。因此,与层次化设计方法相比,此过程需要更长的时间来执行,并且需要更多的计算资源。这种全芯片验证任务通常发生在非常关键的时间(例如,当芯片基本完成并且即将流片时),因此意外的延迟可能会影响设计进度。

创建仿真testbench 向量

默认会产生 signoff一级用于仿真的pattern;测试向量仅仅测试设计插入的控制器;当DFTSpec中的属性"simulate instruments in lower physical instances"设置为true时 设计中包含的更低层次的MBIST controller也可以同时被测试到;所有的控制器是并行仿真的;

文件准备

完整的block core or top_level design的TSDB

当前设计抽取的ICL模型

当前设计的PDL with procedure;

当前设计的门级网表

#生成pattern的相关命令

set pat_spec [create_patterns_specification]

#如果需要,将reduced-address-count设置成off 为了测试Memory的所有address range;;

set wrap [get_config_elements -in_wrapper ${pat_spec} Patterns(MemoryBist_P1)/TestStep/MemoryBist]

set_config_value reduced_adress_count -in_wrapper ${wrap} off

report_config_data $pat_spec

process_patterns_specification

#指向仿真库文件的源;

set_simulation_library_sources -y ./memlibs -extension {v}

#执行BIST testbench的仿真

run_testbench_simulation

#检查监控仿真

check_testbench_simulations

创建Manufacturing Test pattern(制造测试向量)

生成pattern根据一个模式中可能处于活动状态的 ATE异步时钟的数量进行分组; 在默认的specification中max-asyn_clock_sources 属性所标记的数量为不限制.

manufacturing test pattern常常执行完整存储器地址空间的测试;pattern specification种的属性reduced-adress-count默认为off;支持多种文件格式的pattern,可在PatternSpecification中manufacture_pattern_formats指定,默认为STIL文件格式;

pattern生成流程

输入同样是 TSDB ICL和PDL,配置好当前设计

#在创建pattern的spec的时候需要指定 manufacturing 选项

set pat_spec [create_patterns_specification manufacturing]

#直接

process_patterns_specification

#生成的pattern会存放在 TSDB文件夹下的pattern内

生成MBIST的验证patterns

验证向量一般会包括:

一个ICL验证向量

一个或者多个 Memory BIST向量

ICL验证向量会在抽取ICL模型之后自动创建;用于验证ICL的描述是否正确,与设计实际的硬件实现是否匹配;

MBIST pattern测试实现的MBIST controller是否被设计内合适的时钟所驱动,以及指示BIST控制器进行存储器的测试;

示例

PatternsSpecification(blockA,rtl,signoff) {

Patterns(ICLNetwork) {

ICLNetworkVerify(blockA) { } }

Patterns(MemoryBist_P1) {

ClockPeriods { CLK : 12.0ns; }

#指定时钟引脚 和时钟周期 会在testbench中创建对应的时钟生成器,在生成manufacturing testpattern时一般为ATE提供的时钟;

TestStep(run_time_prog)

#一个MBIST pattern包含一个或多个TestStep,TestStep会按顺序执行可以执行指定Memory Bist以及Bisr的控制器操作

{ MemoryBist {

run_mode : run_time_prog;

reduced_address_count : on;

#通过 打开reduce_adress_count实现更快的仿真;因为Memory的TCD 文件之前已经通过全地址空间的验证.

Controller(blockA_rtl_tessent_mbist_c1_controller_inst)

{ DiagnosisOptions {

compare_go : on;

#Mbist控制器的Go输出可以在每一个 clock周期进行比较,如果期望值和观测值比较发生mismatch,Go端口的输出为low

compare_go_id : on;}

#能够将单个数据比较bitsshift out出来,此信息用于识别导致期望与观测值不匹配的数据位

RepairOptions {

check_repair_status : on; } }

}

}

}

Patterns(MemoryBist_ParallelRetentionTest_P1) {

ClockPeriods { CLK : 12.0ns; }

TestStep(ParallelRetentionTest) {

MemoryBist {

run_mode : hw_default;

parallel_retention_time : 0;

reduced_address_count : on;

Controller(blockA_rtl_tessent_mbist_c1_controller_inst) {

parallel_retention_group : 1;

DiagnosisOptions { compare_go_id : on; } }

}

}

}

}

本文介绍了如何使用Tessent Memory Bist工具进行内存的内建自测试(BIST)和验证。内容涉及memlibCertify引擎的使用来验证内存测试属性,Tessent MBIST的模式生成,以及仿真和制造测试向量的创建。此外,还详细说明了不同测试阶段的流程,如在层次化设计中的MBIST插入和全芯片验证。

本文介绍了如何使用Tessent Memory Bist工具进行内存的内建自测试(BIST)和验证。内容涉及memlibCertify引擎的使用来验证内存测试属性,Tessent MBIST的模式生成,以及仿真和制造测试向量的创建。此外,还详细说明了不同测试阶段的流程,如在层次化设计中的MBIST插入和全芯片验证。

2255

2255

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?