More articles You can follow the official account:“IC练习生”

IC民工不定期更新

BAP

BAP(BIST access port)会覆盖连接到BAP上的memory controler的一些默认操作模式;

通过消除串行配置MBIST控制器的shift cycle,大大缩短测试时间,代价是在BAP和控制器之间存在额外的连接;

BAP的高级访问属性部分是通过IJTAG协议进行配置的,这种控制器的配置可能被用来做ATE环境中的制造测试,以及通过 Tessent MissionMode控制器进行的in-system test;

高级BAP 存储器访问也提供了通过连接到BAP的系统信号直接启动存储器测试的能力,而不是串行的通过IJTAG网络将测试的配置信息和结果输入输出;这种直接的访问接口支持低延迟的协议配置MBIST控制器,执行GO/NoGo测试,监控测试通过的状态,只是一些模式比如详细的diagnosis的操作是不可用;

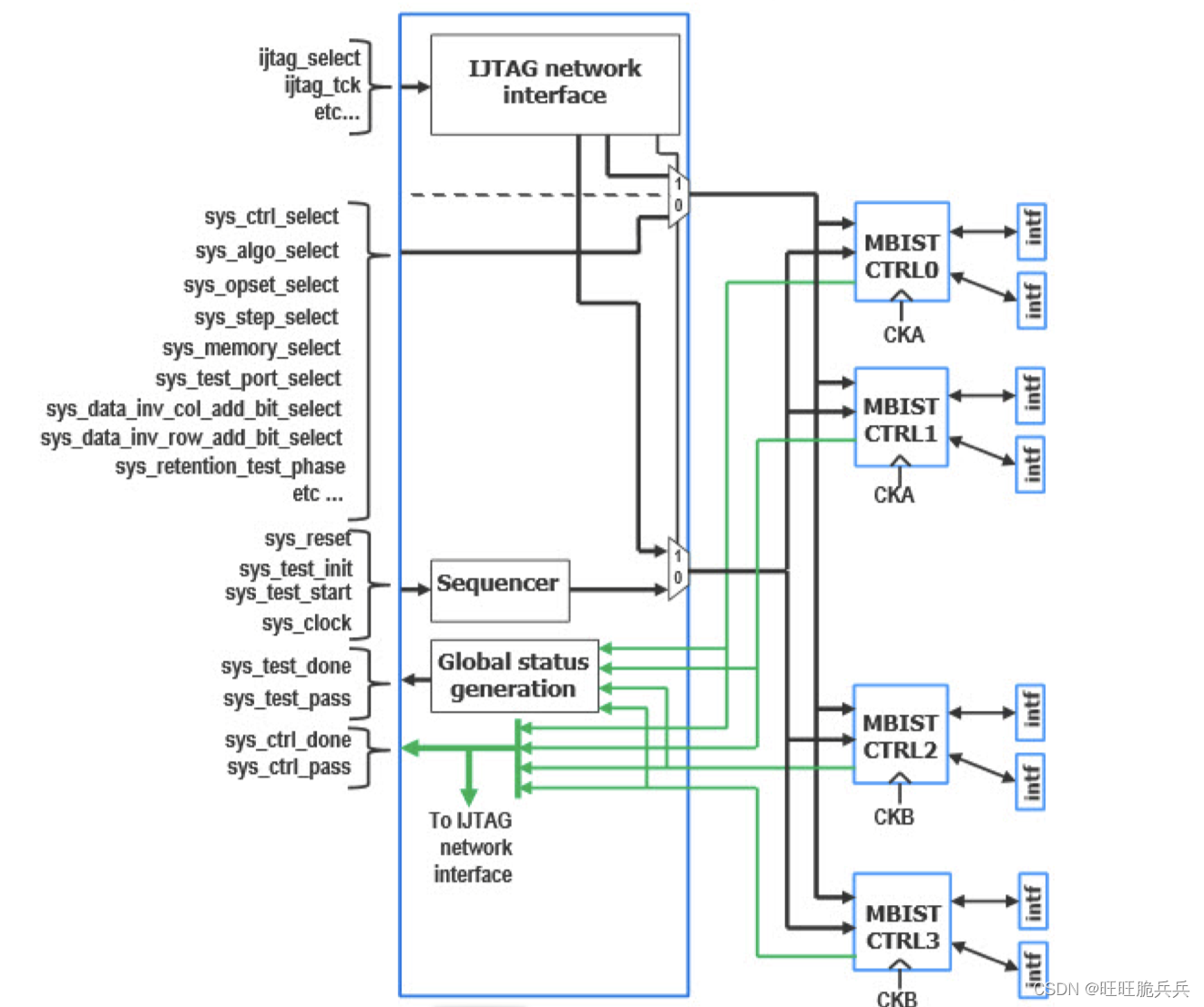

BAP 结构

上图:高级BAP 存储器访问特性由两部分组成: IJTAG网络接口以及BAP的直接访问接口;

BAP的连接是用户配置的直接连接到function 逻辑;

上图右侧的输出端口连接BAP和MBIST的控制器,发送到Mbist控制器的信号被添加到BAP中IJTAG TDRs所配置,或者,如果BAP direct access Interface存在则直接由它来控制;可以通过来自function的系统信号直接控制存储器测试.BAP内的sequencer(序列产生器)能够以低延迟的协议启动和定制存储器测试;在这种实现方式中,使用单个sequencer可以最小化BAP的门面积;sequencer的时钟,sys_clock的频率,应该和IJTAG_tck相当,频率较低,确保生成的控制信号能够以正确的顺序到达MBIST controller;

直接访问接口提供了配置存储器测试的基础选项,可以改变测试算法和操作;你可以选择哪个控制器,哪个step和哪个存储器去基于系统内的测试需要运行测试;比如,如果分配的测试时间有限,可以利用这种灵活性,通过选择具有很少指令的短算法,或者尽在一个存储器上执行MBIST测试;

Repair的分析也可以通过BAP的直接访问接口进行,分析结果通过访问BISR控制器可以用来进行软件,硬件的增量修复;

为每个functional 时钟创建一个sequencer,可以进一步减少开启停止控制器的时间需求,可以更精确的约束在同一时钟域中的sequencer到MBIST 控制器的critical path;

BAP Direct Access interface Pins

BAP的pin的创建是由DFTspec配置的;

指定 DFTspec中的属性:direct_access 为 on,创建 BAP的Direct Access interface;

BAP 直接访问接口的插入

通过 DFTspec 进行配置

MemoryBist{

BistAccessPort {

DirectAccessOptions{

direct_access: on;

}

}

}

对于高级的in-system的用法,使用DFT spec中的ExecutionSelection 字段,根据需要配置系统端的端口;

时钟连接

BAP 直接访问接口支持两种不同的时钟方案,每种方案对sys_clock的连接和信号都有不同的影响;(function时钟和MBIST时钟)

可以通过 DFTspec中的 direct_access_clock_source字段对时钟进行配置;

时钟连接 则使用Connection下DrectAcess/CLockDomain进行配置;

当direct_access_clock_source 被指定为 common时,将在BAP中创建单个test sequencer,管理又有链接的控制器的Memory test;对于此设置,必须指定与系统时钟的连接;

系统logic clock的频率至少要比MBIST的时钟慢4倍,放心,对测试时间没有影响;仅在BAP的test sequencer上使用,使得在没有优化时序路径的时候,sequencer发送的不同的事件有足够的时间传播到控制器.

当direct_access_clock_source 指定为 per_bist_clock_domain时, 将在BAP内部为每个MBIST时钟域创建一个单独的sequencer,每个sequencer的sys_clock会自动连接到 对应时钟域的MBIST的时钟

在任一时钟方案,驱动sys_test_start的系统逻辑可以来自任何时钟域(里面做了同步).

时序

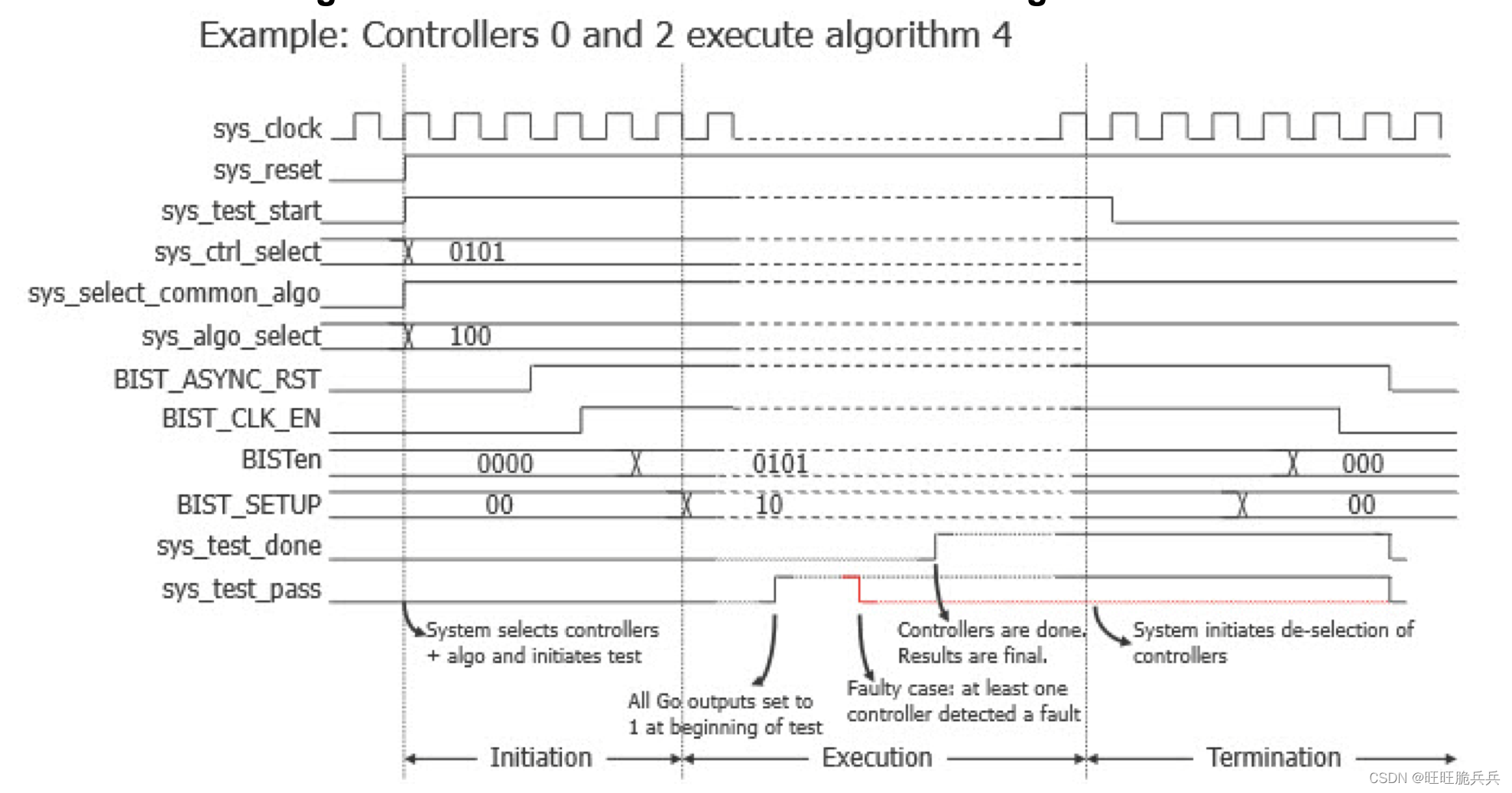

如图所示,低频的function时钟被用来生成sequencer的控制信号,用来控制所有连接到BAP上的MBIST controller;

sys_reset是sequencer的异步复位信号,所有的BAP的输出信号都被设置成inactive的值;当sequencer的复位被释放,sys_test_start信号被用来初始化一个测试,此信号会经过一个同步器,防止跨时钟域传输的问题;

测试初始化事件时序:

- 释放所有MBIST controllers的复位, BIST_ASYNC_RST由0 -> 1;

- 是能所有MBIST controller的时钟, BIST_CLK_EN由0->1;

- 选择MBIST controller,BISTen由000->101;

- 开始测试选择的Mbist controller, BIST_setup由00->10;

在测试执行期间,sys_test_pass持续为高,直到测试完成(sys_test_done信号由0->1)检测到错误为止;

一旦测试完成,sys_test_start输入被设置为0;之前面熟的时间会以相反的顺序执行一遍.在sys_test_start信号去初始化一个新的测试之前至少需要6个时钟周期的空挡去复位;

时钟结构

BAP支持两种不同的时钟结构,如何选择依赖于in-system test是如何执行的;

如果系统控制逻辑执行在一个慢速的功能时钟上,BAP接口能使用相同的时钟源去控制in-system test;BAP内部只会生成单个序列发生器去控制所有的MBIST controller;BAP接口的输出到MBIST controllers之间的延迟的是不重要的,只要信号按照上一节所述顺序到达即可.选择一个和TCK相似的慢速时钟,可以让他们更容易满足时序关系;

如果系统的控制逻辑之行在一个快速的功能时钟上,BAP接口能够被配置为基于每一个时钟域配置in-system test;为每个时钟域的MBIST的各自生成一个sequencer;这种实现方式进一步减少开启停止控制器的时间,从sequencer到MBIST controller共享相同的function时钟,关键路径也能得到更精确的约束;除了sequencer的时钟输入,其他信号比如reset,memory test pass/fail,以及completion status都是每个时钟域独立的;

采样 PASS和DONE信号

对于单个和多个sequencer的实现方式,采样pass/done的信号输出有略微不同;

对于单个sequencer的情况,全局的sys_test_done,sys_test_pass状态信号,以及每个controller的sys_ctrl_pass和sys_ctrl_done状态信号是不会寄存在BAP接口中的;这些信号直接来自于各个MBIST controller的DONE和GO信号,可能来自不同的时钟域.针对这种情况,需要考虑怎样在function逻辑中捕获这些信号去避免潜在的跨时钟域的问题.

- 等待一个合适的时间,等所有的controller都将测试跑完;

- 使用由sys_test_clock或者其他合适的function时钟驱动的同步单元对sys_test_done输出做同步;

针对多个sequencer的情况,不用考虑PASS DONE的同步问题;

3907

3907

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?