在10.28日的博客中讲述了如何设计异步十进制加法计数器, 这里我们再以异步十六进制加法计数器的设计, 加深对异步时序逻辑电路设计思路的理解.

设计方案1:

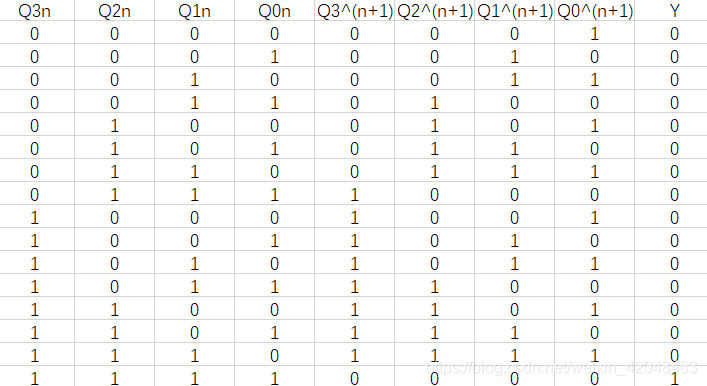

第一步, 和同步时序逻辑电路的设计套路一样, 列十六进制加法计数器的状态表:

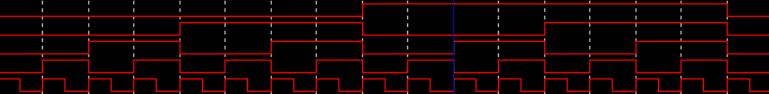

第二步, 将状态表转换为时序图, 并从中找出Q0、Q1、Q2和Q3的变化规律:

从时序图中可以看出, 只要系统时钟迎来上升沿, Q0的状态就会变化; Q1变化在Q0的下降沿处, Q2变化在Q1的下降沿处, Q3变化在Q2的下降沿处. 根据这里的分析, 得到时钟方程 CP0=CP, CP1=Q0n', CP2=Q1n', CP3=Q2n'.

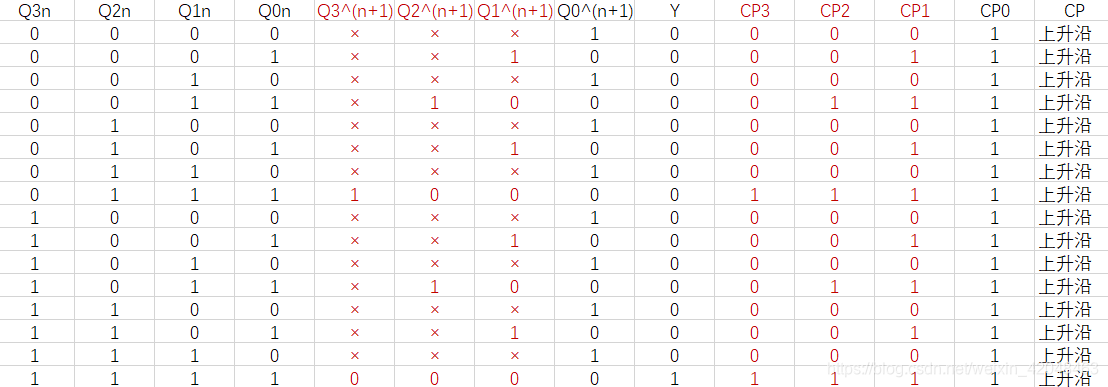

第三步, 根据时钟方程修改状态表:

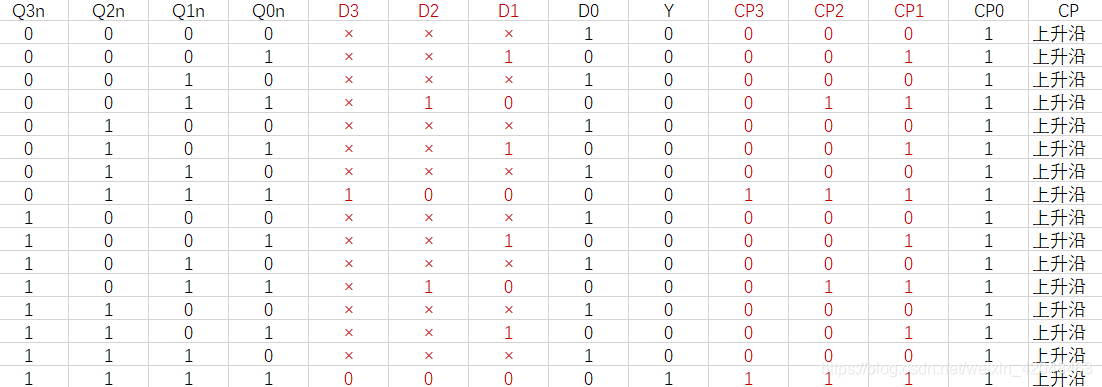

第四步, 根据修改后的状态表, 绘制状态激励表(统一选择上升沿触发的D触发器):

第五步, 根据绘制的状态激励表, 求输出方程和

本文通过详细解析两种设计方案,深入探讨异步时序逻辑电路中十六进制加法计数器的设计,重点讨论了时钟选择对电路工作的影响,展示了从状态表到电路逻辑图的完整设计过程。

本文通过详细解析两种设计方案,深入探讨异步时序逻辑电路中十六进制加法计数器的设计,重点讨论了时钟选择对电路工作的影响,展示了从状态表到电路逻辑图的完整设计过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2615

2615

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?