着实是苦恼啊!找半天找不到NC-verilog仿真好的教程,那么~只能自己动手了!撒开!我要放大招了!

一、简介

ncverilog 是shell版的,nclaunch是以图形界面为基础的,二者调用相同内核;ncverilog的执行有三步模式和单步模式,在nclaunch中对应multiple step和single step。基于shell的ncverilog操作(尤其是单步模式)更适合于大批量操作,ncverilog的波形查看配套软件是simvision(这玩意儿还是很重要的,在设计环境不出错的前提下,如果仿真出现问题,就需要利用simvision查看波形及追踪电路),其中包含原理图、波形、信号流等查看方式

1.1 三命令模式

ncvlog -f run.f

第一个命令中,run.f是整个的RTL代码的列表,值得注意的是,我们需要把tb文件放在首位,这样可以避免出现提示timescale的错误

注意:ncvlog执行以后将产生一个名为INCA_libs的目录和一个名为worklib的目录

ncelab tb -access wrc

第二个命令中,access选项是确定读取文件的权限。其中的tb是你的tb文件内的模块名字。

注意:ncelab要选择tb文件的module,会在snapshot文件夹下生成snapshot的module文件

ncsim tb -gui

第三个命令中,gui选项是加上图形界面在这种模式下仿真,是用“ - ”的。而下边要说的ncverilog是采用“ + ”的三命令模式下GUI界面较好用,其对应的命令会在console window中显示

注意:选择snapshot文件夹下生成的module文件进行仿真

1.2单命令模式:

ncverilog +access+wrc rtl +gui

在这里,各参数与三命令模式相同。注意“ + ”通常都使用单命令模式来跑仿真,但要配置好一些文件单命令模式下文件的配置:

目录下有源文件、测试台文件、file、run四个文件在linux下执行source run后再执行simvision来查看 run文件内容: ncverilog +access+rw -f file file文件内容: cnt_tb.v(注意把tb文件放在前)cnt.v

tb文件中应该包含:

initial

begin

$shm_open("wave.shm"); //打开波形保存文件wave.shm

$shm_probe(cnt_tb,"AS"); //设置探针

end

A – signals of the specific scope 为当前层信号设置探针

S – Ports of the specified scope and below, excluding library cells

C – Ports of the specified scope and below, including library cells

AS – Signals of the specified scope and below, excluding library cells 为当前层以以下层信号都设置探针, 这是最常用的设置方法

AC – Signals of the specified scope and below, including library cells

M– ,表示当前scope的memories, 可以跟上面的结合使用, “AM” “AMS” "AMC"什么都不加表示当前scope的ports;

$shm_close //关闭数据库

在仿真以前,你必须编译和描述它。编译过程将把源文件中的用HDL编写的单元编译成内在的描述。描述设计将在设计的实例化,结构化信息的基础上建立设计的层次结构,建立信号的连接,计算所有对象的初始值。你编译,描述和仿真你的设计要用到以下的工具:

- ncvlog:编译verilog文件

- ncelab:描述设计并且生成仿真的snapshot。

- ncsim:对snapshot进行仿真。

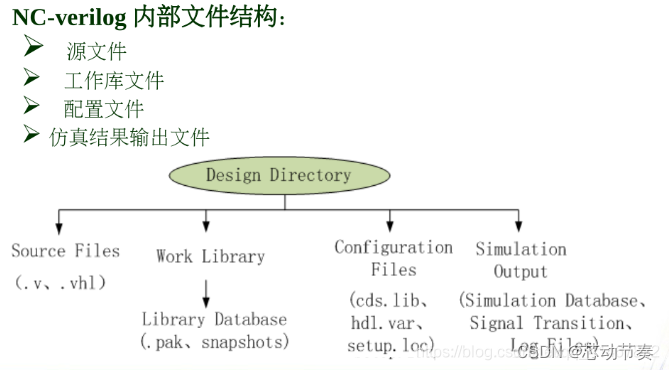

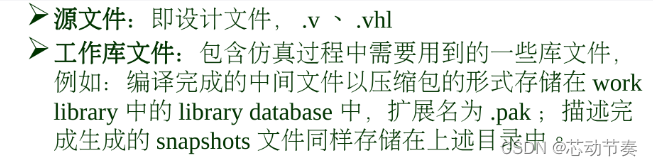

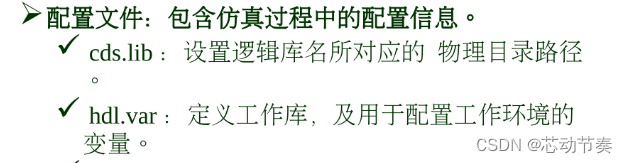

二、NCverilog文件结构

三、仿真设计项目代码

export pattern=""

export design=""

ncverilog -access rwc -w

#为设计中没有指定`timescale的module指定默认的timescale

-timescale 1ns/1ps

#调用64-bit版本的ncvlog

-64

#指定PLI1库

loadpli1=debpli:novas_pli_boot

#指定库文件的扩展名,与-y配合使用

+libext+.v+.vp

#自动开始仿真

-run

#打印内存和CPU的使用情况统计

-status

#允许多个文件定义同一个对象

-allowredefinition

# 延迟模式 {Zero,PUnit,Unit,Path,Distr,None}

-delay_mode zero

#屏蔽Specify块中的时序以及SDF中的延时和时序检查

-nospecify

#关闭时序检查

-notimingchecks

#为连续的udp指定恒定的延迟

-seq_udp_delay 5ps \

+define+ARM_UDMODEL +define+MEM_CHECK_OFF+VIRAGE_WUPPORT_TESTPINS_FFV

# 使用指定的命令行文件

-f [file]

#定义输出的log文件名

-l [log]

四、提高NC-Verilog仿真效率的技巧

回顾一些NC-Verilog的命令行选项,并说明这些选项如何影响仿真效率。同时,我们也展示了一些技巧,以帮助用户的NC-Verilog在最大效率下仿真一个设计和测试平台。

文中的命令行选项语法采用单步启动的方式(ncverilog +),这些选项也适合多步启动模式(ncvlog, ncelab, 或ncsim)。

4.1 安装最新发布的软件

首先确认你是否安装了最新的Cadence LDV版本。自动1996年发布第一版NC-Verilog以来,我们的研发队伍一直把仿真器的仿真效率作为重点来研究。在后来推出的新版本里,不断按各种设计风格优化仿真器,因此使用最新版本是最有利的。直到2002年2月,最新版本是LDV 3.4(s1)。

4.2 使用NC-Verilog内置的profiler

NC-Verilog在仿真引擎内开发了一个profiler工具。该工具每秒中断仿真器100次,并将终端时的结构记录下来,生成一个日志文件。日志文件里列出了被中断次数最多的模块、代码行和结构类型。这些信息可以帮助你诊断是哪些代码或模块在仿真时耗费了最多的时间。通过修改这些模块,就能提升仿真效率。

Profiler功能很容易启动,并对仿真只产生非常小的影响。

% ncverilog +ncprofile <other_options>

or

% ncsim –profile snapshot_name <other_options>

在仿真结束时,profiler会创建一个日志文件(ncprof.out),文件里列出了profile运行的细节。关于如何利用 profiler日志文件,可参考Cadence在线文档(Cadence NC-Verilog Simulator Help, Version 3.4, Chapter 14)。

4.3禁止时序验证来提升效率

缺省情况下,如果在设计中考虑了时序,NC-Sim将进行标准延迟格式(SDF)的全时序标注(annotation),并在仿真时检查时序。在进行功能验证时,如果你不需要仿真时序,就可以通过禁止一些时序检查功能来提高NC-Sim的仿真速度。这样虽然不能验证时序,但是提高了仿真效率,减少了仿真内存需求。

下面是一些用来禁止时序检查的一些命令行。

% ncverilog +delay_mode_distributed +notimingcheck +noneg_tchk

或

% ncelab –delay_mode dist –notimingchecks –noneg_tchk

下面还列出了关于时序的全局选项:

ncverilog option ncelab option

+nonotifier -nonotifier Disables notifier register

+notimingcheck -notimingchecks Disables timing check

+delay_mode_unit -delay_mode unit Delay 1 simulation time unit

+delay_mode_zero -delay_mode zero Zero delay

+delay_mode_distributed -delay_mode dist Ignores specify block delays

Cadence LDV 3.3(2001年7月)增加了通过一个时序控制文件来为各个模块设置时序选项的功能。你可以模块为单位来设置是否进行时序检查,是否允许I/O路径延迟、端口延迟、库单元延迟和全时序检查。时序控制文件里要写明要配置的实例(instance)。命令行语法是:

% ncverilog +nctfile <timing_ctl_file> <other options>

或

% ncelab –tfile <timing_ctl_file> snapshot_name <other_options>

时序控制文件的语法在Cadence 在线文档(Cadence NC-Verilog Simulator Help, Version 3.4, Chapter 8)中可以找到。

4.4 提高SDF的精度

时序信息通过SDF文件传递给一个设计。在LDV 3.1以前的版本里,缺省的SDF精度是10ps。从LDV 3.1开始,所有的时序宽度(包括小于10ps的)都允许使用,这样仿真的时序结果更加精确,但是仿真变得更慢。在多数情况下,10ps就足够了,因此你也许想用下面的方法来改变精度:

% ncverilog +ncelabargs+”-sdfprecision 10ps” <other options>

或

% ncelab –sdf_precision [10ps|1ps|100fs] <other_options>

4.5 关于负时序(negative timing)检查

LDV 3.3缺省的仿真配置为负时序检查。这样,LDV 3.3和以前的版本的仿真结果就有所不同。

负时序检查有下列的选项:

ncverilog option ncelab option

+neg_tchk -neg_tchk Still exists for backward compatibility

+noneg_tchk -noneg_tchk Sets negative timing checks to zero

(matches previous behavior)

4.6设置访问属性

缺省情况下,NC在非调试模式运行,仿真速度很快。可以通过设置访问属性和行调试(line-debug)功能来配置在仿真过程中信号、模块、和代码的访问属性。这样做降低了仿真的速度。

如果你想在代码中设置断点,就必须使用行调试选项。该选项对仿真效率影响非常大。

% ncverilog +linedebug <other options>

或

% ncvlog –linedebug <other_options> <verilog_source_files>

也可以设置设计的全局访问属性。下列的命令可以用来配置设计为允许读、写和交叉访问(connectivity access)。

% ncverilog +access+[rwc] <other options>

或

% ncelab –access [rwc] snapshot_name <other_options>

r : read capability for waveform dumping, code coverage, etc

w : write access for modifying values through PLI or tcl code

c : connectivity access to querying drivers and loads in C or tcl

前面曾经提到过,这些选项将降低仿真的速度。读属性是通常要使用的,它对仿真性能影响非常小。

为了给部分对象、模块或实例设置访问属性,可以创建一个访问属性文件,并在文件中说明那些对象的访问属性。然后用在运行 elaborator 时使用 –afile选项。

% ncverilog +ncafile+<access_filename> <other _options>

or

% ncelab -afile <access_filename> snapshot_name <other_options>

% ncsim snapshot_name <other options>

也可以用 –genafile 选项来自动生成访问属性文件。当仿真使用了Tcl、PLI或probing功能,无法提前确定对象的访问属性,就可以采用自动生成访问属性文件的方法。 Elaborator 在生成仿真快照(snapshot)时会考虑你给出的 –genafile选项;然后,当运行仿真时,Tcl或PLI访问过的对象就会被记录下来。退出仿真的时候,访问属性文件就生成了。举个例子:

% ncverilog +ncgenafile+access.txt <other _options>

或

% ncelab -genafile access.txt test.top <other_options>

% ncsim test.top <other options>

仿真运行完成后,生成了一个access.txt 文件。你可以通过 –afile 选项来使用这个文件(象前面介绍的那样):

% ncverilog +ncafile+access.txt <other _options>

或

% ncelab -afile access.txt test.top <other_options>

访问属性文件的语法可在Cadence 在线文档(Cadence NC-Verilog Simulator Help, Version 3.4, Chapter 8) 中找到。

小结

本文提供各种提高仿真速度的方法。

提高仿真效率的最简单办法是选用最新版的Cadence LDV。我们应该经常运行NC-Sim Profiler来判断仿真器在哪里耗费最多的时间。然后集中精力优化那些代码。

还可以使用命令行选项来提高仿真效率。你可以通过这些选项来配置时序功能、改变SDF精度和配置对象的访问属性。提高仿真效率、可靠性和准确性对于验证设计都很重要。

NC 仿真时,第一步是编译整个设计, 使用的命令是ncvlog, 这一步将会检查语法和静态语义错误. 若无错误,那么讲生成VST. VST是Verilog Syntax Tree 的缩写, 它是后续的ncelab和ncsim命令所必需的中间数据格式, 该数据会存储在以pak为扩展名的文件中, 可以使用ncls来查看文件中的对象。

ncvlog 基本语法: ncvlog [-options] filename.v

例1: > ncvlog -messages alu.v ( 编译 alu.v文件, 并显示详细的信息)

五、NCverilog命令

#1. ncvlog

#ncvlog [options] source_file ...

Options:

-DEFINE // Defines a macro

-FILE // Load command line arguments from rmation

-MESSAGES // Specifies printing of informative messages

-NOCOPYRIGHT // Suppresses printing of copyright banner

-NOSTDOUT // Turn off output to screen

-NOWARN // Disables printing of the specified warning message

Examples:

#// To compile all the modules in source.v

% ncvlog source.v

#// To compile with informative messages

% ncvlog -messages source.v

#2. ncelab

ncelab [options] [lib.]cell[:view]

Options:

-MESSAGES // Specifies printing of informative messages

-NOCOPYRIGHT // Suppresses printing of copyright banner

-NOSTDOUT // Turn off output to screen

-TIMESCALE // Set default timescale on Verilog modules.

-ACCESS // Set default access visibility. {+rwc} turn on read/write/connectivity.

-FILE // Load command line arguments from

-LOADPLI1 // Specify the library_name:boot_routine(s) to dynamically load a PLI1.0 application

-MAXDELAYS // Selects maximum delays for simulation

-MINDELAYS // Selects minimum delays for simulation

-TYPDELAYS // Selects typical delays for simulation

-NONEG_TCHK // Disallow negative values in SETUPHOLD & RECREM timing checks

-NONOTIFIER // Notifiers are ignored in timing checks.

-NOSPECIFY // Don't execute timing checks, ignore path delays and skip SDF annotations.

-NOTIMINGCHECKS // Don't execute timing checks

-NOWARN // Disables printing of the specified warning message

-NO_TCHK_MSG // Turn off timing check warnings

-SDF_NO_WARNINGS // Do not report SDF warnings

Examples:

// To elaborate my_lib.top:behav

% ncelab my_lib.top:behav

% ncelab my_lib.top

% ncelab top

// To elaborate with informative messages

% ncelab -messages my_lib.top:behav

#3. ncsim

ncsim [options] [lib.]cell[:view]

Options:

-FILE // Load command line arguments from

-GUI // Enter window mode before running simulation

-INPUT // Script to be executed during initialization

-MESSAGES // Specifies printing of informative messages

-NOCOPYRIGHT // Suppresses printing of copyright banner

-NONTCGLITCH // Suppress delayed net glitch suppression messages

-NOSTDOUT // Turn off output to screen

-NOWARN // Disables printing of the specified warning message

-SDF_NO_WARNINGS // Do not report SDF warnings

Examples:

// To simulate the snapshot my_lib.top:snap

% ncsim my_lib.top:snap

% ncsim my_lib.top

% ncsim top

// To simulate while writing to the log file ./ncsim.log

% ncsim -log ./ncsim.log my_lib.top:snap

// To update the snapshot my_lib.top:snap and simulate

% ncsim -update my_lib.top:snap

#4. ncverilog

ncverilog [all valid Verilog-XL arguments]

Supported Dash options:

-f Read host command arguments from file

Supported plus options:

+access+ //Turn on Read, Write and/or Connectivity Access

+define+ //Define a macro from commandline

+loadpli1= //Specify the library_name:boot_routine(s) to dynamically load a PLI1.0 application from commandline

+maxdelays //Selects maximum delays for simulation

+mindelays //Selects minimum delays for simulation

+typdelays //Selects typical delays for simulation

+ncdumpports_format+ //Specify EVCD format flag for $dumpports

+neg_tchk //Allow negative values in SETUPHOLD & RECREM timing checks (default)

+noneg_tchk //Disallow negative values in SETUPHOLD & RECREM timing checks

+nocopyright //Suppresses printing of copyright banner

+no_notifier //Notifiers are ignored in timing checks

+nosdfwarn //Do not report SDF warnings

+nospecify //Suppresses timing checks and path delays in specify blocks.

Ignore SDF annotations.

+nostdout //Turn off output to screen(terminal)

+notchkmsg //Turn off timing check warnings

+notimingcheck //Don not execute timing checks

+nowarn+ //Disables printing of the specified warning message

+sdf_nowarnings //Do not report SDF warnings

#5. ncsdfc

ncsdfc [options] sdf_file

Options:

-COMPILE // Compile the specified SDF files (default)

-DECOMPILE // Decompile the specified SDF files

-LOGFILE // Specifies the file to contain log information

-MESSAGES // Specifies printing of informative messages

-NOCOPYRIGHT // Suppresses printing of copyright banner

-OUTPUT // Redirects compiled SDF output to the specified file

-WORSTCASE_ROUNDING // Truncate min delays, round max delays up

Examples:

// To compile an SDF file:

% ncsdfc dcache.sdf

Creates compiled SDF file dcache.sdf.X

// To specify a name for the compiled SDF file:

% ncsdfc ipipe.sdf -OUTPUT ipipe.compiled

Creates compiled SDF file ipipe.compiled

// To decompile a compiled SDF file:

% ncsdf -DECOMPILE ebox.sdf.X

Creates decompiled SDF file ebox.sdf.X.sdfd

// To specify a name for the decompiled SDF file:

% ncsdfc -DECOMPILE ebox.sdf.X -OUTPUT ebox.sdfd

Creates decompiled SDF file ebox.sdfd

#6. nchelp

nchelp [options] tool error

nchelp [-cdslib | -hdlvar]

+access<+/-rwc> Turn on read, write and/or connectivity access

+allow_unused_properties Allow simulator to enable all properties

-allowredefinition Allow mutiple files to define the same object

+amsconnrules+ specify connect rules to use

+amsmatlab Dynamically link vpi code for AMS/Matlab

-amsmt_enable to enable AMS multithread capability

-amsmt_nthreads number of threads for AMS multithreading.

-amsvhdl_ext Override extensions for VHDL AMS sources

+append_key Append keystrokes to existing key file

-arr_access Allow tf_nodeinfo access to Verilog arrays

-asext Add extensions to assembly sources

+assert Enable PSL language features

+assert_count_traces Use trace-based counting for assertions

+assert_sc Enable PSL language features

+assert_vhdl Enable PSL language features

+assert_vlog Enable PSL language features

-bb_nonsynth Blackbox unsynthesizable modules in halsynth

-bb_unbound_comp Ignore unbounded component for synthesis checks

-bb_vital Blackbox design-units containing VITAL constructs

-c Parse and elaborate, do NOT simulate

-catcxx Positional option used to combine C++ sources

-catcxxsize Sets the CATCXX partition size for large groups

-categories List the categories and their descriptions

-ccext Add extensions to C sources

-check Specify checks and categories of checks

+checkargs Check command-line arguments for validity

-clean Deletes previous INCA_libs directory if is exists

-comb_depth Enable Logic Depth calculation

+compile Parse only, do NOT elaborate

+controlassert+ Specifies a file containing assertion controls

-cpost Compile C files after elaboration

+crshell Create shell files for import mode

-cxxext Add extensions to C++ sources

-D Define a macro for the C and C++ compiler

-date Print date and time when each engine is invoked

-debug Equivalent to -access +rw, Specman debug

-debugscript Specify a debug script file name

+define+ Define a macro from command line

-defineall Define macro from command line for all compilers

+defparam+ Redefine the value of a Verilog parameter

-delay_mode Delay mode {Zero,PUnit,Unit,Path,Distr,None}

+delay_mode_distributed Use distributed delay mode

+delay_mode_path Use path delay mode

+delay_mode_punit Use precision unit delay mode

+delay_mode_unit Use unit delay mode

+delay_mode_zero Use zero delay mode

-design_facts_file Generate design facts during structural checks

-design_info Design Information file

-distcomp Option used to turn distributed compilation on

-distcompargs, Pass user specified argument to distributed comp

-distcompjobs Number of parallel distributed compiles to run

-distplat Specify underlying platform used for distrib comp

-dpi Add appropriate build options for dpi designs

-dpi_void_task Return value of export/import tasks will be VOID.

+dut_prof+ Profiler report contains summary for design unit

-dynamic Build a shared object for simulation

-dynvhpi Enable user to create VHDL drivers at run time

-efence Debug ncsim with Electric Fence.

-efenceelab Debug ncelab with Electric Fence

-end Terminate the list of files

-extbind Bind file for binding SV/VHDL to SV/VHDL

-F Scan file for args relative to file location

-f Scan file for args relative to irun invocation

-forceelab Force ncelab to execute

-format Enables shorter compiling messages from ncsc_run

-g Turn on C debugging

-gcc_vers 3.2.3 or 4.1 Linux only

-gdb Run ncsim under gdb

-gdbelab Run ncelab under gdb

-gdbpath Use the provided gdb instead of what is shipped

+genassert_synth_pragma Enable generating assertions from synth pragma

-gnu Choose the GNU C and C++ compiler

+gui Invoke the Graphical User Interface

-h Print a minimal help message

-hal Call hal instead of ncsim

-halargs Pass options directly to hal

-halsynth_detailcheck Perform detailed check on unsynthesizable modules

+helpalias Show the different ways to enter an option

+helpall Display all supported option

+helpargs Print help for all the options in use

+helpfileext Show all the file types and their extensions

+helphelp Print out all the options controlling help

-helpncverilog Show the ncverilog form of the options

-helpshowmin Show the minimum characters required for dash opt

+helpshowsubject Show all the subjects for -helpsubject

+helpsubject Display help on the specified subject

+helpverbose Show the verbose help text

+helpwidth+ Set max width for help messages (def 89)

-I Directory to search for C/C++ include files

+ieee1364 Report errors according to IEEE 1364 standards

+import Prepare this verilog design for import to VHDL

+incdir+ Specify directories to search for `include files

-inst_top Specify the top-level instance for HAL analysis

-iusld Prefix `ncroot`/tools/lib path to LD_LIBRARY_PATH

-iusldno Disable the -iusld option

-k Set key file name

-L Directory to search for lib files

-l Set logfile name

-l archive or shared library to be linked in

-level Specify levels in HAL analysis

+libext+ Specify extensions to be used for the -y search

+liborder Library search rule (see documentation)

+librescan Library search rule (see documentation)

+libverbose Print verbose messages about instance binding

-linksysc Use libsystemc.so (dynamic) or libsystemc_ar.a

-lintpragma Process lint pragma in the design

-loadcfc Dynamically load a CFC application

-loadfmi Dynamically load an FMI library

+loadpli1= Specify the PLI1 library_name:boot_routine(s)

+loadsc+ Specify SystemC lib to be dynamically loaded

-loadvhpi Dynamically load a VHPI application

+loadvpi= Specify the VPI library_name:boot_routines(s)

-location Print the location of the installation

-log_amsspice Place amsspice output into the specified logfile

-log_hal Place the hal output into the specified logfile

-logic_depth Enable Logic Depth calculation

-loop_unroll_size Specify the loop unroll limit for halsynth

+max_error_count+ Specify the maximum number of errors processed

+mixesc Handle escaped identifiers in imported model

+multisource_int_delays Make interconnect timing be multisource capable

+name+ Generate snapshot with specified name

-native Use the native C and C++ compiler

+nc64bit Invoke 64bit version

+nca_ext+ Override extensions for archive files

+ncafile+ Specify an access file to be used

+ncams Force Verilog-AMS and VHDL-AMS compilation

+ncamsfastspice Enable Fast SPICE simulator (UltraSim)

+ncamslic Check out an AMS license

+ncamspartinfo+ Mixed-signal partition information

+ncamsv_ext+ Override extensions for Verilog-AMS sources

+ncanalogcontrol+ Specify analog simulation control file

+ncanno_simtime Enable delay annotation at simulation time

+ncappend_log Append output log to existing log

-ncb_environment Specify environment file to be loaded by Ncbrowse

-ncb_file File for Ncbrowse to load command line arguments

-ncb_filter Filter for report generation by Ncbrowse

-ncb_format Set the format of messages in the report

-ncb_nodefaultenv Prevent Ncbrowse from using default environment

-ncb_order Set the order in which items are shown

-ncb_report Specify the report file to be created by Ncbrowse

-ncb_sortby Specify a sort order to Ncbrowse for report

+ncbatch Run simulation in batch mode, this is the default

+ncbinding+ Force explicit submodule or unit L.C:v binding

+ncc_ext+ Override extensions for C sources

+ncccargs Pass arguments to the C compiler

+nccd_lexpragma Process preprocessor directive before lex pragmas

+nccds_implicit_tmpdir+ Specify location for design data storage

+nccds_implicit_tmponly Force tools to read design data only from tmpdir

+nccdslib+ Specify a cds.lib file to be used

+ncchecktasks Check that all $tasks are built-in system tasks

+ncchkdigdisp Perform digital net's discipline compatibility

+ncconffile+ Generate a configuration file with the given name

+ncconfflat Requires -CONFFILE, generate a VHDL flat config

+ncconfhier Requires -CONFFILE, gen VHDL hierarchical config

+ncconfname+ Requires -CONFFILE, specify output config name

+nccontrolrelax+ Enable specific relaxed VHDL interpretation

+nccovdesign+ Select coverage design name

+nccovdut+ Select DUT for Coverage

+nccoverage+ Enable coverage instrumentation

+nccovfile+ Specify coverage instrumentation control file

+nccovnomodeldump Disable coverage design database (model) dumping

+nccovoverwrite Enable overwrite of coverage output files

+nccovtest+ Select coverage test name

+nccovworkdir+ Select coverage workdir

+nccpg+ Assigns to all generics/params of this name

+nccpp_ext+ Override extensions for C++ sources

+ncdebug Equivalent to -access +r

+ncdefault_ext+ Override the default extension map

+ncdesign_top+ Specifies top design unit for design-top comp

+ncdisable_enht Disable enhanced timing features

+ncdiscapf Disable the capital F input file mode

+ncdiscipline+ Discipline to use for undisciplined digital wires

+ncdisres+ Set discipline resolution

+ncdpiheader+ Create DPI header file for export functions

+ncdresolution Sets discipline resolution to '-disres detailed'

+ncdumpports_format+ Specify EVCD format flag for $dumpports

+ncdynlib_ext+ Override extensions for dynamic library files

+nce_ext+ Override extensions for e sources

-ncelab_args, Pass arguments to elaborator (ncsc_run compat)

+ncelab_compile requires -CONFILE, compile the configuration file

+ncelabargs+ Pass arguments to elaborator

+ncelabexe+ Specify elaborator with statically linked PLI

+ncelabfile File for generated elab options from import

+ncendlib Terminate the list of library files

+ncendstage Terminate the list of e stage files

+ncerror+ Increase the severity of a warning to an error

+ncescapedname Print out escaped names in logfile

+ncexit Exit simulation instead of issuing a TCL prompt

+ncexpand Force expansion of all vector nets

+ncextassertmsg Prints Extended Assert message Information

+ncextend_tcheck_data_limit/ Relax timing check data limit

+ncextend_tcheck_reference_limit/ Relax timing check reference limit

+ncfatal+ Increase the severity of a warn/error to fatal

+ncgateloopwarn Enable potential zero-delay gate loop warning

+ncgenafile+ Generate an access file for PLI and TCL

+ncgeneric+ Associate value with top-level generic

+ncgnoforce Assigns the value if default value not found

+ncgpg+ Assigns to all generics/params of this name

+ncgverbose Logs the gpg activity to the ncelab logfile

+nchdlvar+ Specify an hdl.var file to be used

+nciereport Generate interface element report

+ncignore_defexpr Ignore default expressions on variable,signal,...

+ncinitbiopz Initialize boundary inout port to 'Z'

+ncinitialize+ Initialize variables in the design

+ncinitzero Enable zero initialization of time and integer

+ncinput+ Read TCL commands from file

+ncinsert+ Specify string to be inserted after matching comp

+ncintermod_path Make interconnects be multisource capable

+nclexpragma Enable lexical pragma processing

+nclib_binding Defaults back to the IUS5.4 binding search order

+nclibcell Mark all cells with `celldefine

+nclibdirname+

Specify directory name to store created library

+nclibdirpath+ Relative path where libraries should be created

+nclibmap+ Specify the library mapping file

+nclibname+ Specify the name of a library to search

+nclicq Queue simulation till license is available

+nclinedebug Enable line debugging capabilities

+nclist Produce a VHDL source listing in specified file

+nclog_ncelab+ Place the ncelab output into specified logfile

+nclog_ncsc_run+ Place the ncsc_run output into specified logfile

+nclog_ncsim+ Place the ncsim output into the specified logfile

+nclog_ncvhdl+ Place the ncvhdl output into specified logfile

+nclog_ncvlog+ Place the ncvlog output into specified logfile

+nclog_svpp+ Place the svpp output into specified logfile

+nclps_assign_ft_buf Disable continuous assignment as feed through net

+nclps_cpf+ Specify a CPF file for low power simulation

+nclps_iso_off Turn off port isolation

+nclps_logfile+ Specify a log file for low power simulation

+nclps_off Turn off low power simulation

+nclps_rtn_lock Lock the retained reg value

+nclps_rtn_off Turn off state retention

+nclps_simctrl_on Enable runtime control over low power simulation

+nclps_stime+ Specify a time to start low power simulation

+nclps_stl_off Turn off state loss

+nclps_verbose+ Specify a level of information reporting

+nclps_verify Enables automatic Low Power verification

+nclps_vhdlpwron Brings back VHDL objects to a defined state

+ncls_all Run ncls with the -all option

+ncls_dep Run ncls with the -dep option

+ncls_so Run ncls with the -source option

+ncls_ss Run ncls with the -snapshot option

+ncmakelib+ Compile HDL files into specified library

+ncmatchinst+ Specify name of instance to match for -INSERT

+ncmaxdelays Select maximum delays for simulation

+ncmindelays Select minimum delays for simulation

+ncmodelincdir+ Specify a list of directories separated by :

+ncmodelpath+ For Verilog-AMS, specify list of source files

+ncmultview Allows selection of arch/config for binding

+ncnamemap_mixgen Do name mapping from VHDL generics to Vlog params

+ncno_cross_def_bind Suppress cross-language default binding

+ncno_notifier Ignore notifiers in timing checks

+ncno_sdfa_header Do not print the SDF annotation header

+ncno_tchk_xgen Turn off X-generation in VITAL timing checks

+ncno_vpd_msg Turn off VITAL pathdelay warnings

+ncno_vpd_xgen Turn off X-generation in VITAL pathdelays

+ncnobinding+ Skip instances of unit given as argument

+ncnobuiltin Do not use any built-in IEEE operators

+ncnocifcheck Disables constraint checking in VDA functions

+ncnocopyright Suppress printing of copyright banner

+ncnodeadcode Turn off dead code optimization

+ncnoesp Disable edge-sensitive iopath delays

+ncnoipd Ignore interconnect delays

+ncnokey Suppress generation of the default keyfile

+ncnolicpromote Do not use a mixed language license

+ncnolicsuspend Disable suspending licenses for SIGTSTP

+ncnoline Do not locate source line on errors

+ncnolog Suppress generation of the default logfile

+ncnomempack Do not pack memories

+ncnomxindr Do not generate NOMXINDR error; split net instead

+ncnontcglitch Suppress delayed net glitch suppression message

+ncnoparamerr Do not flag setting undefined parameters as error

+ncnopragmawarn Disable pragma related warning messages.

+ncnoscynceverydelta Turn Delta cycle accuracy off

+ncnosncomp Do not compile Specman input files

+ncnosource Do not check source file timestamps in update

+ncnospecview Do not invoke the Specview GUI

+ncnostdout Turn off output to screen (terminal)

+ncnotimezeroasrtmsg Suppress printing of time zero assert messages

+ncnovitalaccl Turn off VITAL acceleration

+ncnovitalcheck Suppress VITAL compliance checking

+ncnowarn+ Disable printing of the specified warning

+ncnoxilinxaccl Turn off Xilinx acceleration

+ncntc_level+ Select NTC algorithm 1 or 2 (default is 2)

+ncntc_verbose Display verbose information about NTC process

+ncntcnotchks Generate NTC delay while removing timing checks

+nco_ext+ Override extensions for object files

+ncomicheckinglevel+ Specify OMI checking level {Min, Std, Max}

+ncoverride_precision Override the timescale precision in Verilog

+ncoverride_timescale Override the timescale directives in Verilog

+ncpassword Prompt for sim passwd for SimVis walkup connect

+ncpli_export Export symbols from loadpli, loadvpi

+ncpliverbose Print information for PLI/VPI task registration

+ncppdb+ Invoke the post-processing environment

+ncppe Enter post-processing mode

+ncpragma Enable pragma processing

+ncpreserve Preserves resolution of single-driver sigs

+ncprofile Generate a run-time profile of the design

+ncprofoutput+ Specify an output file for profiling data

+ncprofthread Allow threaded processes to profile

+ncpromt Prompts to select arch/config/view for entity/mod

+ncpropspath+ Specify analog occurrence property database file

+ncrandwarn Enable all SV randomize failure warnings

+ncredmem Use reduced memory image size

+ncreflib+ Add the library to the list of libraries searched

+ncrelax Enable relaxed VHDL interpretation

+ncrun Begin simulation automatically

+ncs_ext+ Override extensions for assembly files

+ncsavechoice+ Specify name of file in which to save bindings

+ncsaveenv Save the shell environment variables

-ncsc_msgs Tell ncsc to run ncsc messages on or off

+ncscargs+ Pass arguments to ncsc_run

+ncscope_discipline+ Specify one scope based discipline

+ncscparameter+ Associates values with top level SystemC params

+ncscprocessorder+ Allow System C process order to vary

+ncscscreateviewables Create ncsc_viewable objs inserted by ncsc_wizard

+ncscynceverydelta+on|off Turn Delta cycle accuracy on

+ncsdf_cmd_file+ Specify file of SDF annotation commands

+ncsdf_nocheck_celltype Do not check the accuracy of CELLTYPE field

+ncsdf_nortis Disable retain input sense

+ncsdf_precision+ Specify precision which SDF data will be modified

+ncsdf_simtime Allow SDF annotation during simulation

+ncsdf_verbose Include detailed information in SDF log file

+ncsdf_worstcase_rounding Truncate SDF min delays, round max

+ncsdfnowarn Do not report SDF warnings

+ncseq_udp_delay+ Specify a constant delay for sequential UDPs

+ncsetdiscipline+ Set discipline for a specified scope.

+ncshare Reuse any available view with NCUID

-ncsim_args, Pass arguments to simulator. (ncsc_run compat)

+ncsimargs+ Pass arguments to simulator

+ncsimcompatible_ams+ Specify compatibility language hspice or spectre

+ncsimexe+ Specify simulator with statically linked PLI

+ncsimfile File for generated sim options from import

+ncsmartlib Specifies multiple library compilation in OIC

+ncsmartorder Order-independent compilation (OIC) for VHDL

+ncsmartscript+

4343

4343

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?