NC Verilog是Cadence公司开发的Verilog仿真工具,用于验证和调试HDL设计。

创建运行环境

本文使用的工程目录如下所示

work

├── rtl # 用于存放仿真验证的.v文件

│ ├── Detected_1001.v # DUT

│ ├── Detected_1001_tb.v # TestBench

├── sim # 运行仿真的目录。在此目录下运行nc_sim进行仿真、波形调试和覆盖率检测等

│ ├── run_test # 用于启动nc_sim的脚本

│ ├── my_test.flist # 列出所有与设计相关的.v文件的目录

│ ├── script.tcl # 放置需要nc_sim执行的命令

│ ├── run_iccr # 查看覆盖率的脚本

启动编译并仿真

如何启动编译并仿真:进入sim目录,在命令行执行run_test:source run_test

但是在启动编译并仿真前需要配置好sim目录下的三个文件

-

run_test

irun -gui -f my_test.flist -input script.tcl -message -coverage all -covtest cov_name -covoverwrite +access+rwc +sv-gui:打开图形界面-f my_test.flist:加入文件列表,文件列表放在my_test.flist文件中-input script.tcl:添加(执行)一些输入命令,命令放置在script.tcl的脚本文件中-message:执行信息显示-coverage all:收集覆盖率选项。all表示收集所有的覆盖率-covtest cov_name:存放覆盖率数据的目录-covoverwrite:再次运行时可覆盖已生成的覆盖率数据库,不加则不能覆盖+access+rwc:打开文件读写功能+sv:加入System Verilog特性

-

my_test.flist:列出所有与设计相关的 .v文件,包括test_bench文件、所有电路模块 (注意要给出文件的路径位置)

../rtl/Detected_1001_tb.v ../rtl/Detected_1001.v -

script.tcl

database -open waves -shm -default probe -create -all -depth alldatabase -open waves -shm -default:保存波形文件。保存的波形文件最终保存在当前仿真文件夹里的waves.shm目录中probe -create -all -depth all:给所有的信号创建探针。因此,这里就是把所有的信号的波形都保存下来

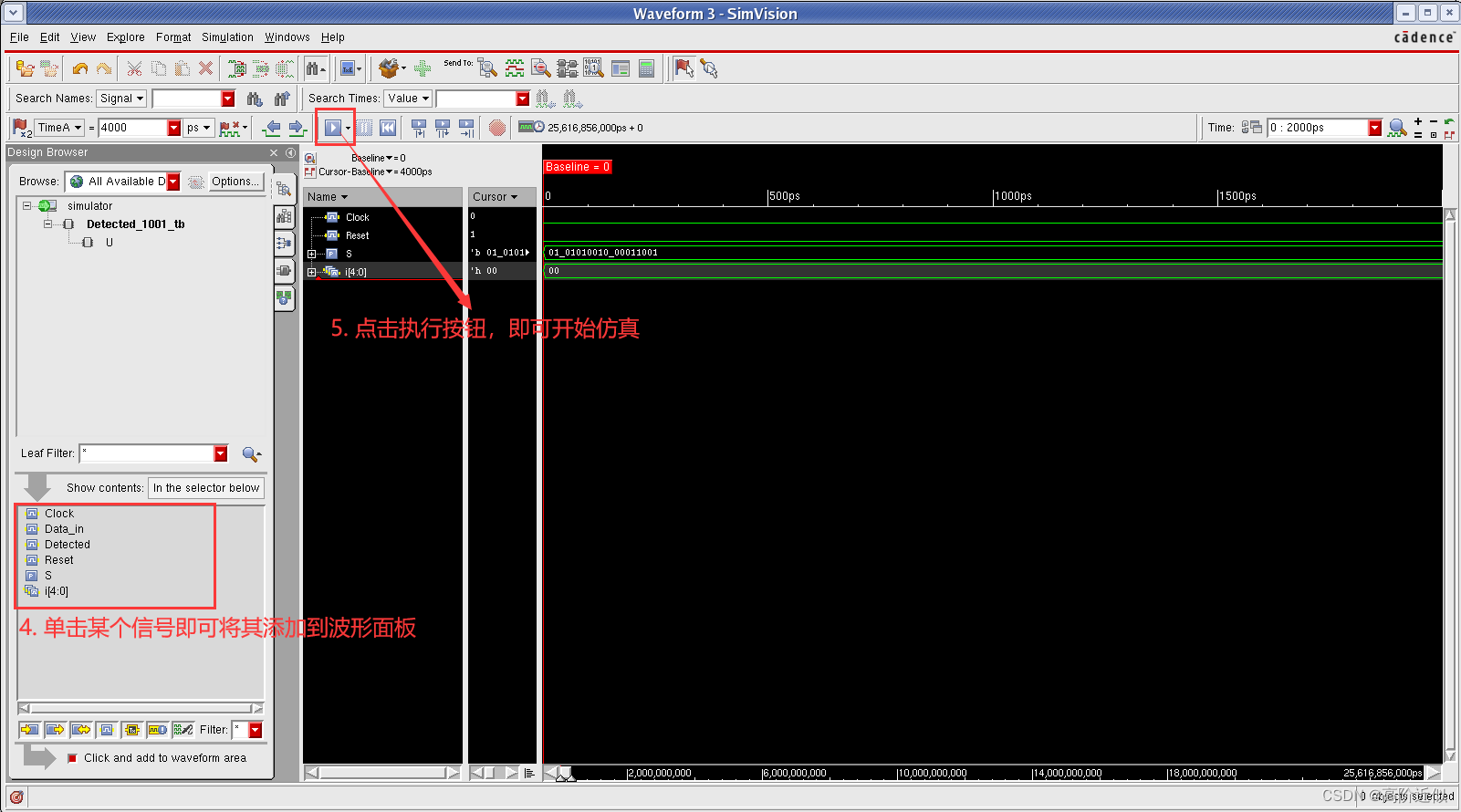

波形查看与调试

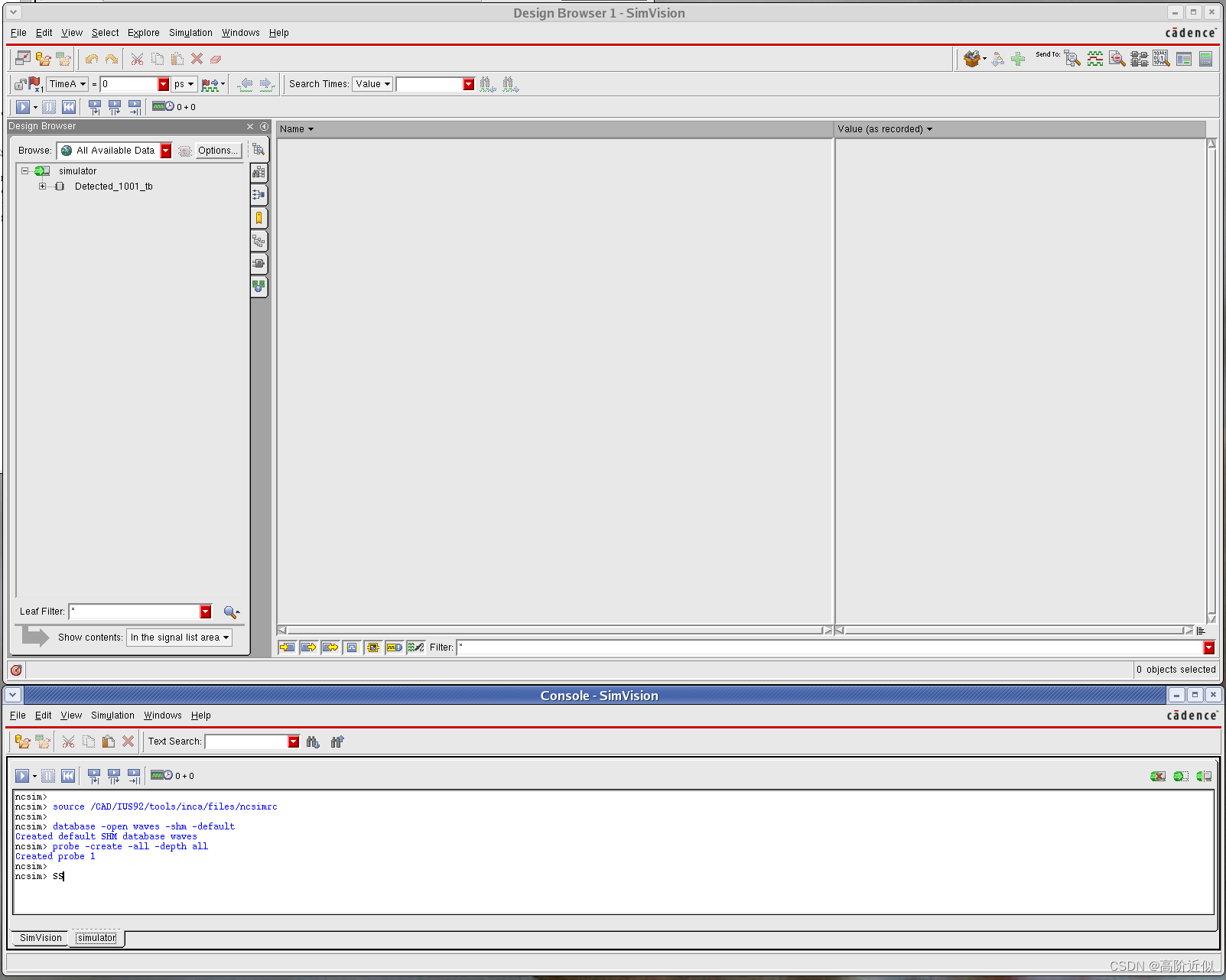

在执行完 source run_test 后,会弹出以下两个窗口

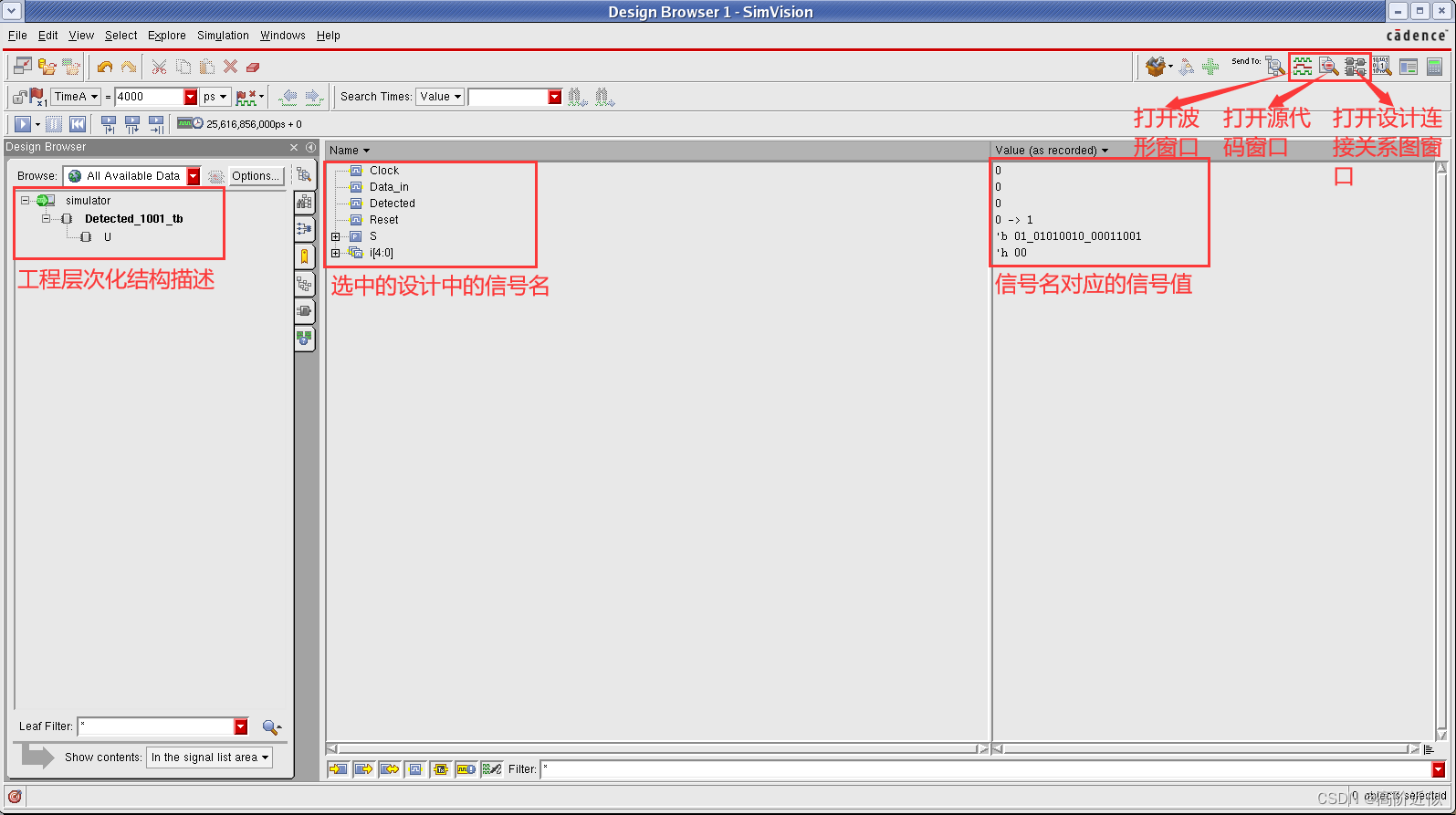

Design Browser 是设计浏览器窗口,显示整个设计的信息

Console 是命令窗口,显示仿真代码中的 display 语句、printf 语句的结果,也可以在此窗口中键入新的命令

Design Browser面板介绍

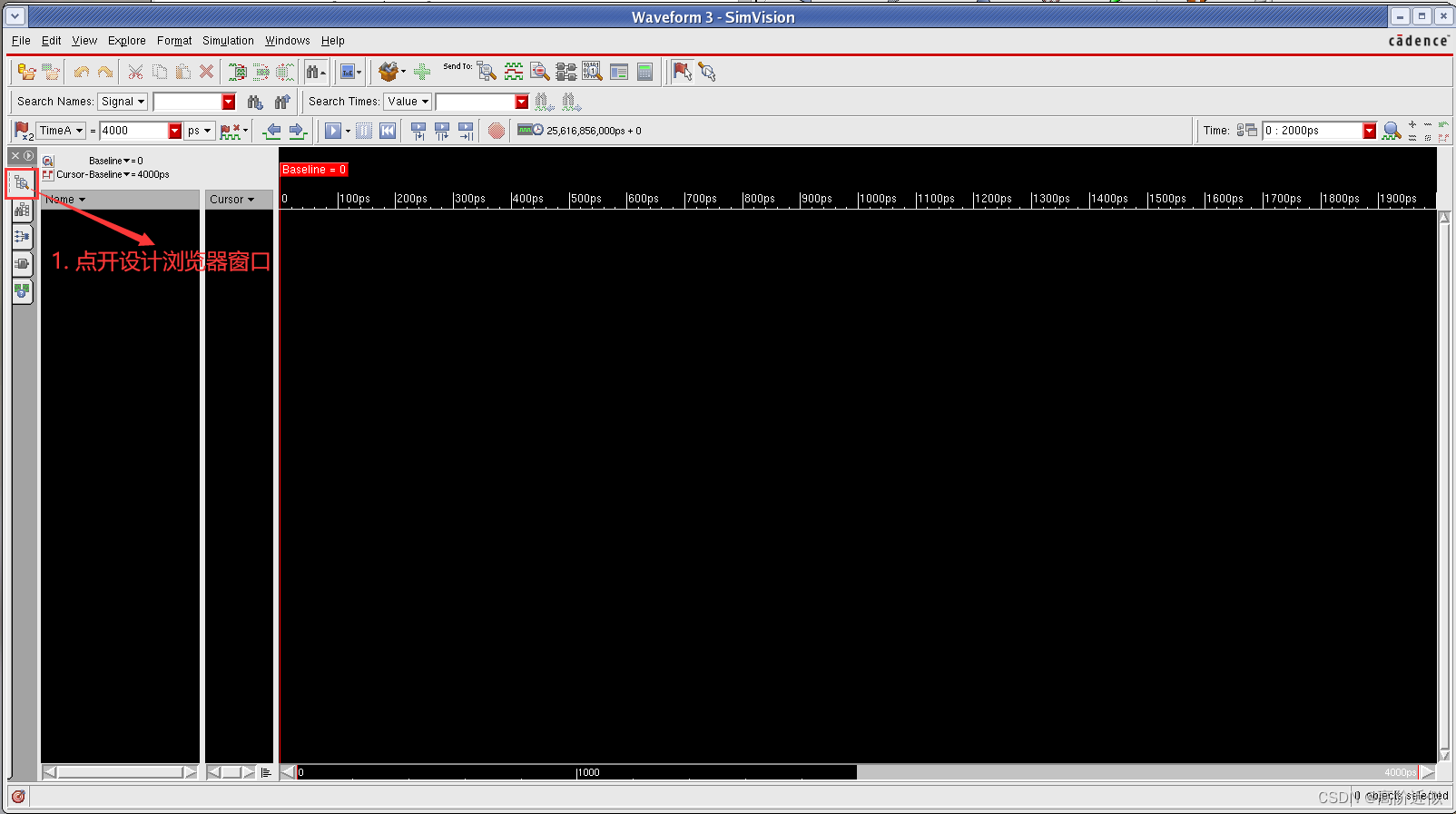

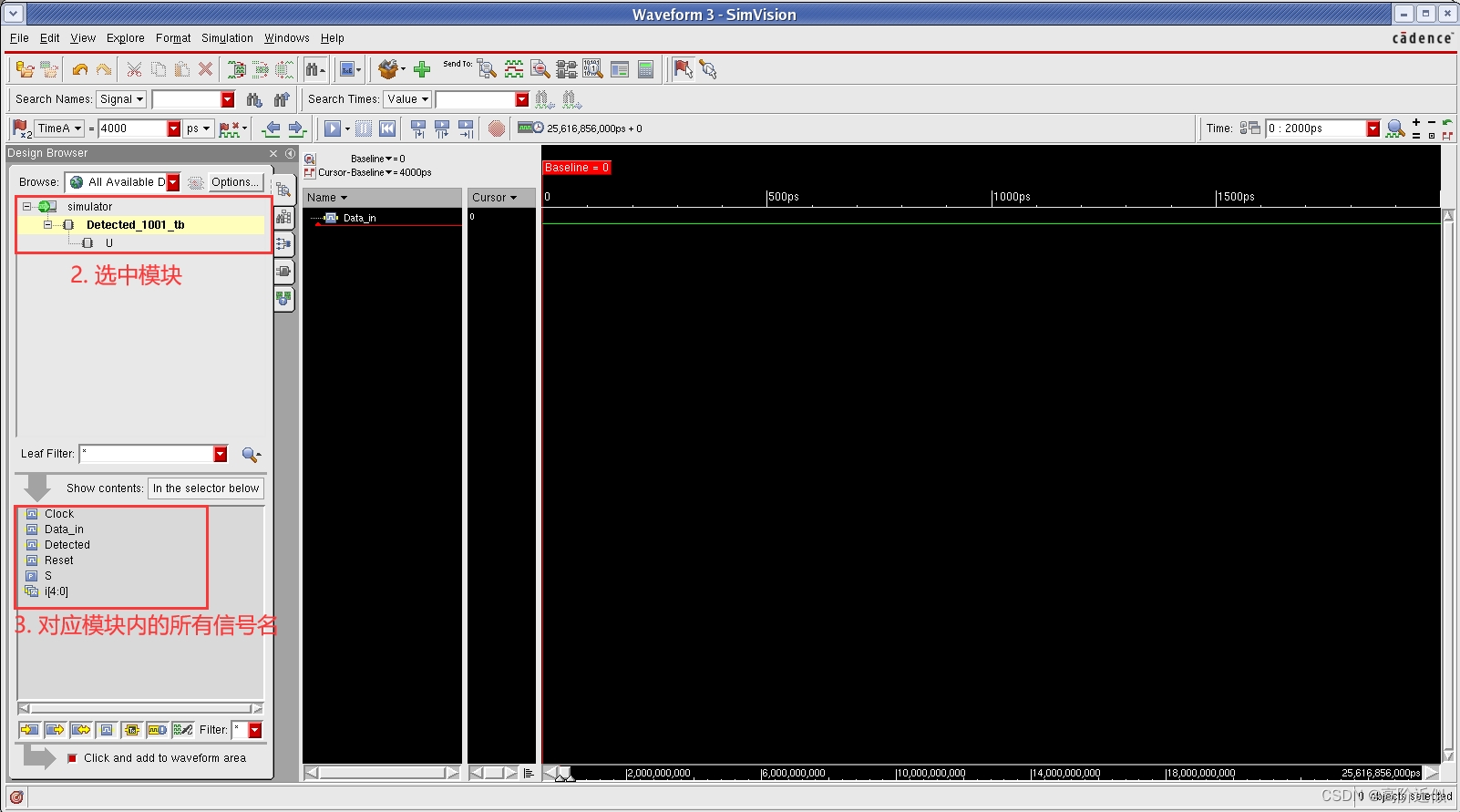

点击“打开波形窗口”按钮,可以打开波形界面如下:

然后点开设计浏览器窗口,可以看到设计层次化信息和信号。将想要查看的信号放到波形界面,就可以通过运行仿真查看波形。

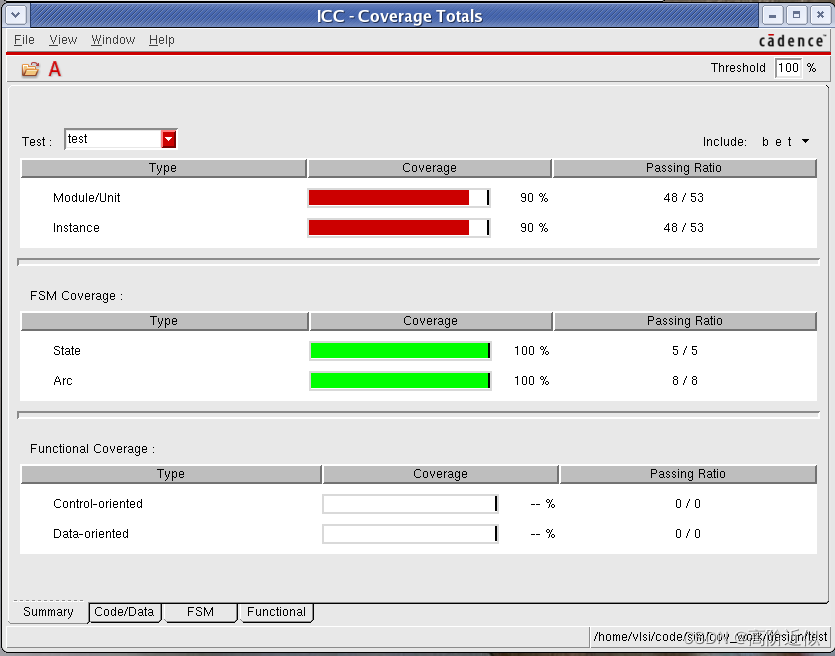

查看覆盖率

-

当编译仿真结束后,会在当前目录(sim)下生成一个名为 cov_work 的目录,覆盖率信息就保存在这个目录下

-

功能调试结束后,关闭图形界面(点击

File->Exit SimVision,不要直接点击窗口右上角的x关闭),然后在命令行里启动查看覆盖率的工具。采用命令:source run_iccr,run_iccr脚本的内容如下所示iccr -test test -gui

6283

6283

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?