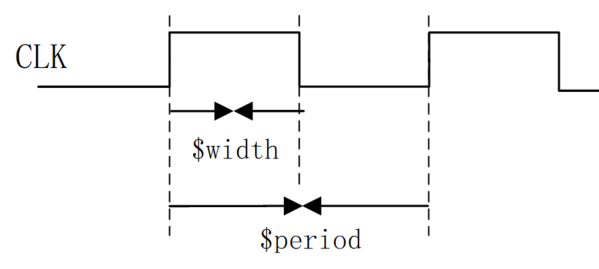

有些数字设计,例如 flash 存储器,还需要对脉冲宽度或周期进行检查,为此 Verilog 分别提供了系统任务 $width 和 $period。用法如下:

$width(ref_event, time_limit) ;

- ref_event: 边沿触发事件

- time_limit: 脉冲的最小宽度

$width 用于检查边沿触发事件 ref_event 到下一个反向跳变沿之间的时间,常用于脉冲宽度的检查。如果两次相反跳边沿之间的时间小于 time_limit,则会报告 violation。

$period(ref_event, time_limit) ;

$period 用于检查边沿触发事件 ref_event 到下一个同向跳变沿之间的时间,常用于时钟周期的检查。如果两次同向跳边沿之间的时间小于 time_limit,则报告中会打印 violation。

检查信号 CLK 宽度和周期的 specify 块描述如下:

specify

$width(posedge CLK, 10);

$period(posedge CLK, 20);

endspecify

886

886

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?