1. Verilog捕获信号上升沿

(1)verilog代码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/11/08 15:36:43

// Design Name:

// Module Name: pedge_nedge

// Project Name:

// Target Devices:

// Tool Versions:

// Description: 捕获信号上升沿

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module pedge_nedge(

input wire clk, //时钟输入

input wire rst, //复位

input wire signal_in, //信号输入

output wire signal_pedge //信号上升沿

);

//*********信号输入打两拍,消除亚稳态***********

reg signal_1;

reg signal_2;

always@(posedge clk)begin

{signal_2,signal_1} <= {signal_1,signal_in};

end

//******************************************

//****************捕获上升沿******************

reg pedge;

reg level_h;

always@(posedge clk or negedge rst)begin

if(rst == 1'b0)

pedge <= signal_2;

else

pedge <= signal_2;

end

always@(posedge clk or negedge rst)begin

if(rst == 1'b0)

level_h <= 1'b0;

else if((signal_2 == 1'b1)&&(pedge == 1'b0))

level_h <= 1'b1;

else

level_h <= 1'b0;

end

//******************************************

assign signal_pedge = level_h;

endmodule

(2)仿真代码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/11/08 17:23:19

// Design Name:

// Module Name: tb_pedge_nedge

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tb_pedge_nedge(

);

reg clk; //时钟输入

reg rst; //复位

reg signal_in; //信号输入

wire signal_pedge; //信号上升沿

initial begin

clk = 1'b0;

rst <= 1'b0;

#10

rst <= 1'b1;

end

always #5 clk = ~clk;

initial begin

signal_in <= 1'b0;

#17

signal_in <= 1'b1;

#10

signal_in <= 1'b0;

#25

signal_in <= 1'b1;

#6

signal_in <= 1'b0;

end

pedge_nedge pedge_nedge_inst(

.clk(clk), //时钟输入

.rst(rst), //复位

.signal_in(signal_in), //信号输入

.signal_pedge(signal_pedge) //信号上升沿

);

endmodule

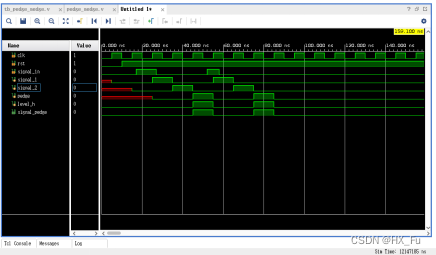

(3)仿真结果

2. Verilog捕获信号下降沿

(1)verilog代码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/11/08 15:36:43

// Design Name:

// Module Name: pedge_nedge

// Project Name:

// Target Devices:

// Tool Versions:

// Description: 捕获信号下降沿

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module pedge_nedge(

input wire clk, //时钟输入

input wire rst, //复位

input wire signal_in, //信号输入

output wire signal_nedge //信号下降沿

);

//*********信号输入打两拍,消除亚稳态***********

reg signal_1;

reg signal_2;

always@(posedge clk)begin

{signal_2,signal_1} <= {signal_1,signal_in};

end

//******************************************

//****************捕获下降沿******************

reg nedge;

reg level_l;

always@(posedge clk or negedge rst)begin

if(rst == 1'b0)

nedge <= signal_2;

else

nedge <= signal_2;

end

always@(posedge clk or negedge rst)begin

if(rst == 1'b0)

level_l <= 1'b0;

else if((signal_2 == 1'b0)&&(nedge == 1'b1))//和捕获上升沿在此处区别

level_l <= 1'b1;

else

level_l <= 1'b0;

end

//******************************************

assign signal_nedge = level_l;

endmodule

(2)仿真代码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/11/08 17:23:19

// Design Name:

// Module Name: tb_pedge_nedge

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tb_pedge_nedge(

);

reg clk; //时钟输入

reg rst; //复位

reg signal_in; //信号输入

wire signal_nedge; //信号下降沿

initial begin

clk = 1'b0;

rst <= 1'b0;

#10

rst <= 1'b1;

end

always #5 clk = ~clk;

initial begin

signal_in <= 1'b0;

#17

signal_in <= 1'b1;

#10

signal_in <= 1'b0;

#25

signal_in <= 1'b1;

#6

signal_in <= 1'b0;

end

pedge_nedge pedge_nedge_inst(

.clk(clk), //时钟输入

.rst(rst), //复位

.signal_in(signal_in), //信号输入

.signal_nedge(signal_nedge) //信号上升沿

);

endmodule

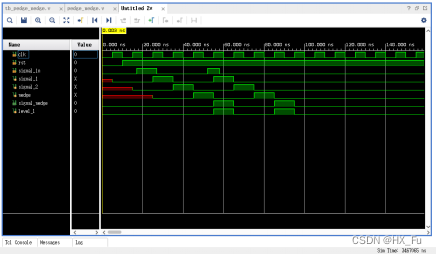

(3)仿真结果

6776

6776

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?