原理:

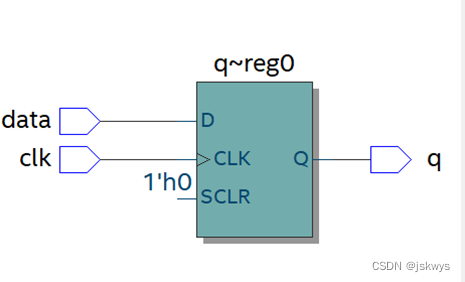

1. 基本的上升沿触发器仅在时钟信号从低电平转换到高电平(即上升沿)的瞬间,才采样输入数据并改变其输出状态。如果在这之前输入发生变化,输出不会响应,直到下一个上升沿到来。这确保了输出对于时钟边沿的稳定性和抗干扰性。

2. 除了基本的上升沿触发功能外,这种触发器还包含一个同步复位(Reset)输入。当复位信号为高(或其他定义的激活电平)并且时钟信号发生上升沿时,触发器的输出被强制设为预先定义的复位状态(通常是0)

3. 异步复位允许触发器的输出在任何时刻,只要复位信号有效,就能立即复位,不依赖于时钟信号。这意味着即使在没有时钟上升沿的情况下,复位也能起作用。

4. 这类触发器不仅具备异步复位功能,还增加了一个时钟使能(Clock Enable, CE)输入。时钟使能信号决定是否允许时钟信号影响触发器的状态变化。当CE为高时,触发器对时钟上升沿敏感;当CE为低时,即使有时钟上升沿,触发器的输出也不会改变。

工具:Quartus18.1

程序代码:

module exp5_9(data,clk,q);

input data,clk;

output q;

reg q;

always@(posedge clk)

begin

q<=data;

end

endmodule测试文件:

`timescale 1ns/1ps

module tb_exp5_9;

reg data;

reg clk;

wire q;

exp5_9 uut(

.data(data),

.clk(clk),

.q(q));

initial begin

data = 0; clk = 0;

#15 data = 1; #15 data = 0;

#15 data = 1; #15 data = 0;

#15 data = 1; #15 data = 0;

#15 data = 0; #15 data = 1;

#15 data = 0; #15 data = 1;

#15 data = 1; #15 data = 0;

#15 data = 1; #15 data = 1;

#15 data = 0; #15 data = 1;

end

always #20 clk=~clk;

endmodule网表文件:

1248

1248

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?