Verilog HDL基本结构

**HDL(Hardware Description Language)**硬件描述语言是对硬件电路进行行为描述、寄存器传输描述或者结构化描述的一种语言。

FPGA作为可编程硬件,采用HDL语言作为编程语言。

通过HDL语言可以对FPGA的功能进行描述,描述完成后的源代码,通过综合(将高层次的寄存器传输级别的HDL设计转化为优化的低层次的逻辑网表)和实现及生成目标文件后,下载到FPGA以实现对FPGA进行配置,配置后的PGA实现了HDL语言描述的功能。(下载:1.jtag调试模式,断电,消失2.下载到flash)

1 一个简单的组合逻辑实例

1.1 模块声明

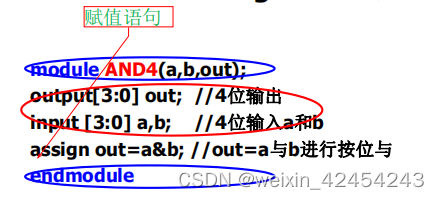

从模块的声明开始,最开始就是关键词module ,然后是这个模块的名字叫AND4 ,最后是endmodule。assign是是组合逻辑的赋值语句。

module AND4(a,b,out);

output[3:0] out; //4位输出

input [3:0] a,b; //4位输入a和b

assign out=a&b; //out=a与b进行按位与

endmodule

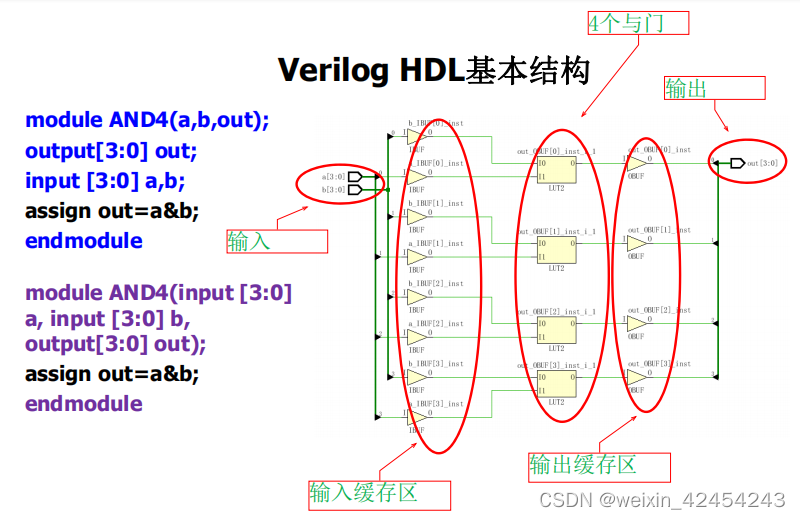

1.2 端口定义的两种写法

法一:端口声明和端口定义分开写

module AND4(a,b,out);

output[3:0] out;

input [3:0] a,b;

assign out=a&b;

endmodule

法二:端口声明和端口定义写在一起

module AND4(input [3:0]

a, input [3:0] b,

output[3:0] out);

assign out=a&b;

endmodule

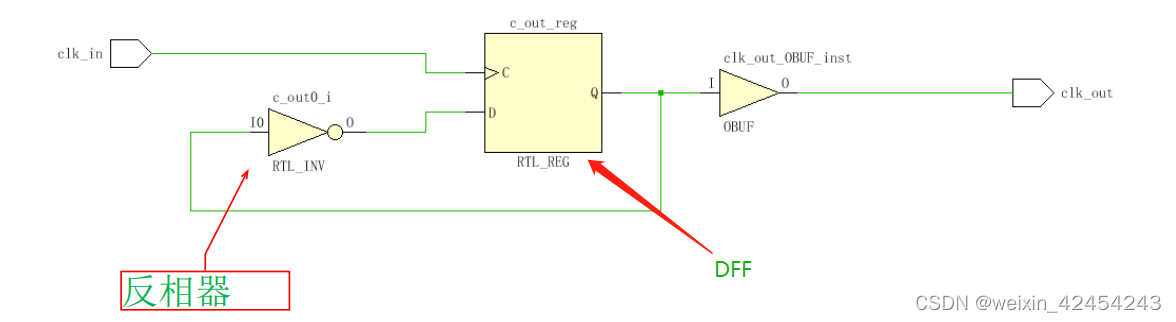

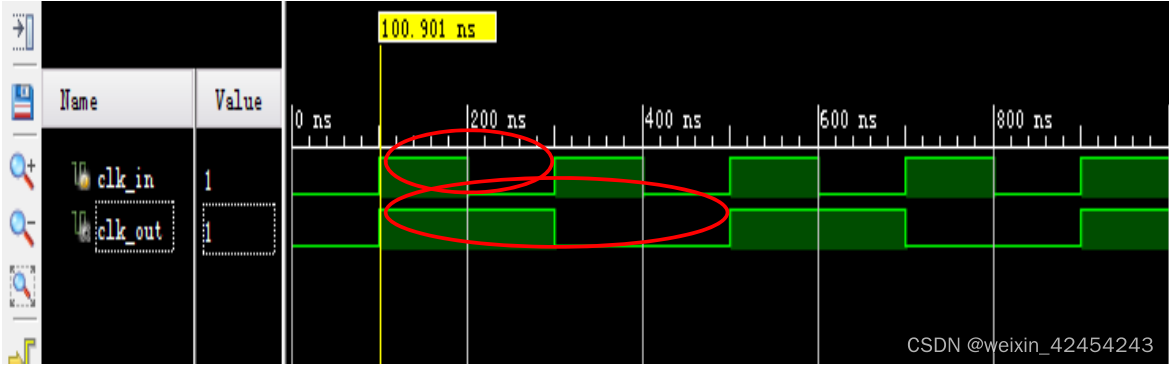

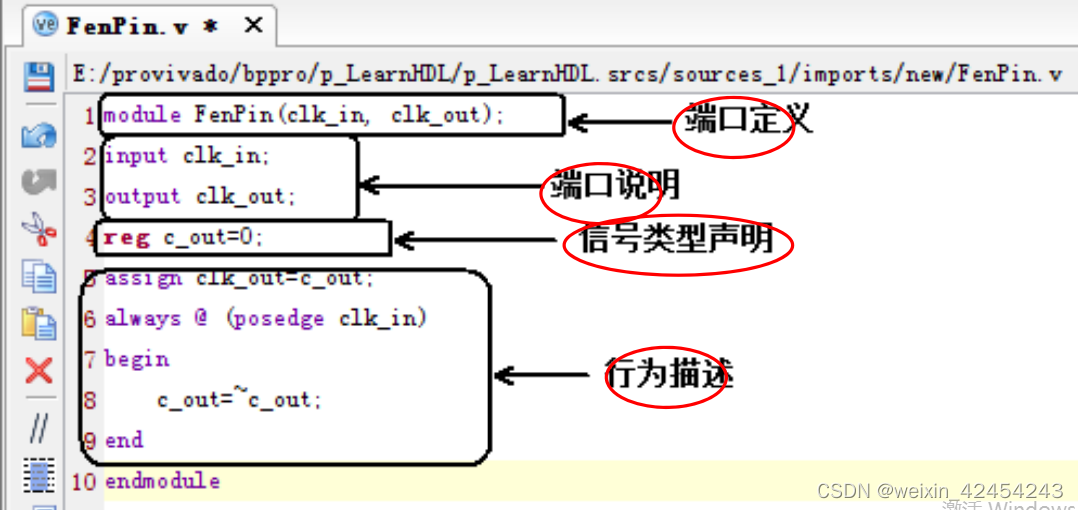

2 一个简单的时序逻辑实例

2分频:在always块中只能对寄存器变量赋值。

module FenPin(input clk_in, output clk_out);

reg c_out=0;

assign clk_out=c_out;

always @ (posedge clk_in)

begin

c_out=~c_out;

end

endmodule

3 Verilog HDL结构要求

- Verilog HDL程序是由模块构成的。每个模块嵌套在module和endmodule声明语句中。

- 每个Verilog HDL源文件中只有一个顶层模块,其他为子模块。可以每个模块写一个文件。

- 每个模块要进行端口定义,并说明输入输出端口,然后对模块的功能进行行为逻辑描述。

- 模块中的时序逻辑部分在always块的内部,在always块中只能对寄存器变量赋值。

- 模块中对端口或其他wire型变量的赋值,必须在always块的外部使用assign语句,通常是将寄存器的值送出。

- 程序书写格式自由,一行可以写几个语句,一个语句也可以分多行写。

- 除了endmodule语句、begin_end语句和fork_join语句外,每个语句和数据定义的最后必须有分号。

- 可用/…/和//…对程序的任何部分作注释。加上必要的注释,可以增强程序的可读性和可维护性。

verilog的一般语法结构:

module 模块名(端口名1,端口名2,端口名3,端口名4,...);

端口定义说明(input,output,inout);

参数定义(可选);

数据类型定义(wire,reg等);

//…………………………以上为描述接口说明部分…………………………//

//…………………………以下为描述逻辑功能部分…………………………//

实例引用低层次模块和基本门级元件;

连续赋值语句(assign);

过程赋值语句(initial和always);

功能描述语言;

任务和函数;

endmodule

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?