引言:本文继续介绍Xilinx 7系列FPGA SelcetIO电平标准及相关端接匹配电路。具体内容包括:

- LVDCI电平标准

- LVDCI_DV2电平标准

- HSLVDCI电平标准

- HSTL电平标准

1.LVDCI电平标准

图1、LVDCI I/O可用的bank类型

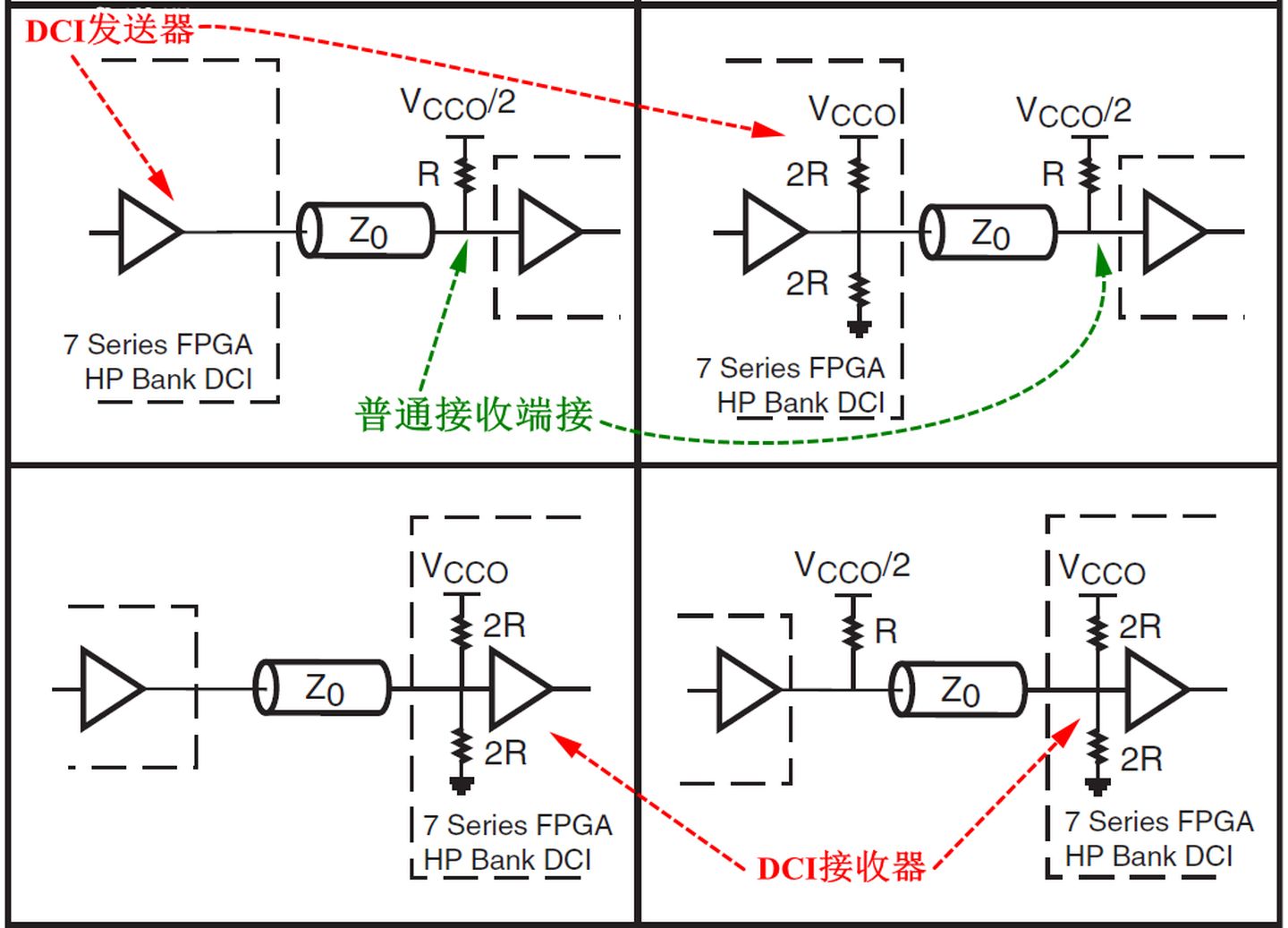

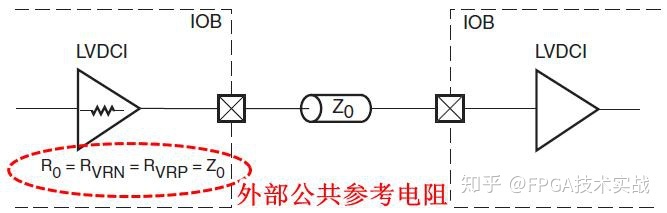

LVDCI接收器本质上和LVCOMS接收器一样。7系列器件HP I/O提供可控阻抗输出驱动器以匹配串行端接,而不需要外部源端电阻。阻抗通过外部公共的参考电阻进行设置,阻抗等于传输线特征阻抗。DCI I/O标准支持LVDCI_15和LVDCI_18标准。

图2显示了单向LVDCI I/O标准可控阻抗驱动器拓扑。

图2、单向LVDCI I/O标准可控阻抗驱动器拓扑

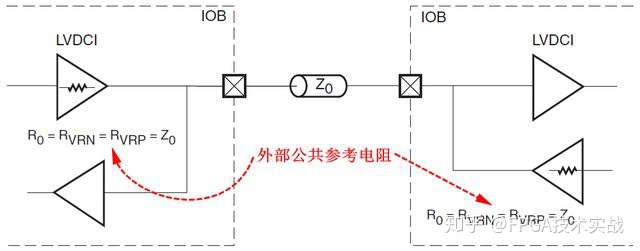

图3显示了双向受控阻抗驱动器拓扑。

图3、双向受控阻抗驱动器拓扑

2.LVDCI_DV2电平标准

具有半阻抗(源端接)的受控阻抗驱动器也可以为驱动器提供参考电阻的一半阻抗。这需要将外部公共参考电阻值增大到2倍,这样可以降低通过VRN和V

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1460

1460

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?