deng-广州

一、前言

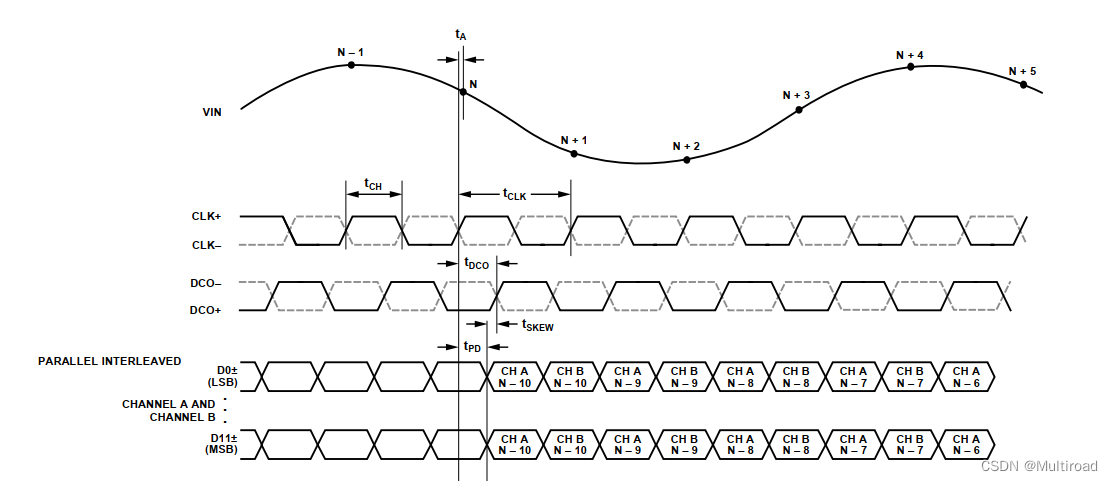

在我们的应用中,需要采用ADC进行数据采集。ADC芯片是ADI公司的AD9613芯片。通过芯片的数据手册可以得知,这款芯片是双通道的高速ADC,接口采用DDR输出。

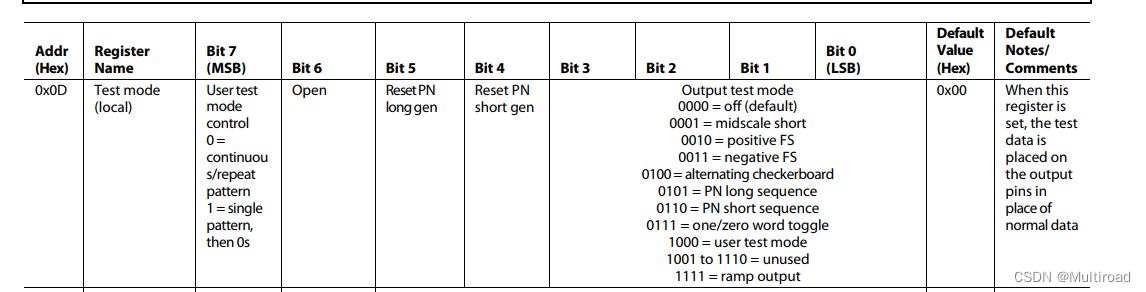

通过芯片手册了解,内置测试模式,如图:

-

调试过程

这个调试来源于一个相对简单的新项目,由一个新来的年轻同事执行。这个项目中的所有模块,都是可以从其他项目工程中获得,只是FPGA的芯片进行了更换。

-

前期调试问题

刚开始调试的时候,我是并没有进行太多的关注。在调试ADC的时候,我让他先试用ADC的内部测试模式进行调试,确定一下接口有没有问题。

然而,同事在使用SPI配置寄存器的时候,捣鼓了很久,都没有成功输出测试模式,我让他检查SPI的时序是否正确,硬件电源是否正常,时钟是否正常。

经过检查,确定硬件没有问题,SPI的时序也没有问题,毕竟这个模块是我之前使用过的,用这个模块调试过这款芯片,并且也用来调试过相似的另一款芯片,读写芯片配置都没有问题的。有个表现是:读芯片的ID是成功的,也验证了SPI模块是没有问题的,但是,就是写完寄存器之后,回读回来,发现寄存器并没有变化(其实,我也忘了这个芯片配置的一个特殊的地方,这款芯片的寄存器配置进去之后,需要配置一个特定的寄存器,才能生效);

然后,我让他再读一下芯片手册看看,不行的话, 让硬件的同事帮忙直接在ADC的输入端接个正弦信号进去看看。(这里,我就没关注了)。

过了一两天,这个同事没有调试寄存器了,而是直接的接入设备的信号测试,我粗看了一下信号,单次采样的信号的波形是差不多的。然后就没有更加没有关注了,基本上数据链路是通了的。

这一个阶段,本来应该通过SPI配置寄存器,读写寄存器正确,然后配置ADC的测试模式,可以验证接口是否存在问题的。

-

突然来的要求

等到周五的时候,boss说要下周二拿样机设备区展示,需要赶快准备好样机。这时候,项目经理跟我说,这个程序还有问题,信号幅度不对,信号也表现出很多噪声,使用示波器测试模拟新哈,并没有那么毛毛躁躁的波形的。

-

紧凑的调试

由于作为整机的表现不好,虽然系统的信号链路不长,但是,我们首先定位问题所在。

第一步,我们屏蔽ADC的输入,采用自测数据输入,也就是除了数据是采用特定的,其他所有的设置以及控制信号都是正常设置;在这一步,我们看到预想的信号是稳定,正常的;因此,我们判断后面的链路以及嵌入式处理等都不存在问题;

第二步,我们验证ADC是否正常;这一步,我们首先使用ila采集数据,发现数据进来后,很多毛刺冒出来,基本上,我们确定信号进来的时候就出现问题;

异常波形表现

第三步,我们采用外部信号源,输入一个正弦信号,发现信号还是有毛刺;这一步,我们一开始怀疑时钟问题或者是时序问题。因此,我们检查ADC的输入时钟。在这一步,我们用示波器的两个表笔进行检查,发现ADC的差分时钟输入并非是180度相位的差的,表现上来看是90度相位差。在这里,我们怀疑是不是FPGA得输出时钟信号问题(ADC的时钟是FPGA输出)。

这个怀疑的问题,我们很快就排查掉。因为FPGA的输出差分时钟,不会相位相差90度的,不管是直接使用一个obufds,还是通过ddr后再输出。我们认为是示波器的两个表笔的信号延时不一致导致的。很快,通过用这套设备测量其他设备的差分时钟得到验证;

第四步,我们添加了ADC的输入约束,综合结果来看,也没有出现报警,我们也使用了selectIO的数据延时设置,通过延时不同的相位。在这一步,不同的延时,的确接口信号发生了变化,有些延时是导致信号波形完全不一致,但是,我们几乎试了所有的延时,居然没有一个延时是完全好的。这就跟理论不一致,因为我们的ddr输入,满足的tap的情况应该很多,不管再差,肯定有某些tap延时是好的。并且,也问了硬件同事,保证信号线是等长设计的。

第五步、在这一步,我们貌似陷入了困局。这时候,觉得还是使用测试模式来验证,才是正道。因为如果ADC链路正常,测试模式肯定是正常的。在这一步,我们明确了测试模式的输出,配置ADC输出ramp模式,发现数据还是出现毛刺;于是,我么你确定我们的IP模块设置有问题;

第六步、我打开代码, 重新核对里边的信号,看看有没有发现信号映射错误。发现了复位信号没有设置,默认是’0’;我马上对比了之前的设置,都是有一个复位信号的。顿时,感觉找到问题了。于是,将IP的复位信号用系统复位接上,一看测试模式,问题解决;

-

二、总结与感想

在这次的调试中,明确了以后开发的顺序要能乱,一些问题没解决,不要理想当然得跳过,起码要知道根本原因,否则最终还是要面对的;

5059

5059

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?