简介:Xilinx SmartLynq Cable作为新一代仿真器,通过与J-Link JTAG接口结合,为FPGA开发者提供了一个高效、便捷的开发和调试体验。本手册详细阐述了如何使用SmartLynq Cable,包括其支持的高速数据传输、多种协议兼容性,以及与J-Link JTAG接口的集成优势,从而提升开发效率和问题定位能力。同时,提供了关于安装驱动程序、配置FPGA、进行硬件调试的指导和建议。

1. Xilinx SmartLynq Cable介绍

1.1 设备概述

Xilinx SmartLynq Cable是为FPGA开发环境特别设计的一种高性能编程与调试电缆,能够提供与Xilinx器件快速、可靠的连接。该电缆采用了最新技术标准,既提高了传输速率,又保证了连接的稳定性和兼容性。SmartLynq Cable不仅支持多种调试协议,如JTAG和SWD,还兼容多种开发环境和操作系统,为工程师提供灵活的开发工具链。

1.2 主要功能

SmartLynq Cable的核心功能在于实现快速编程与高效率调试,其高速USB 3.0接口确保了数据传输的高速度和低延迟。此外,它还包括了状态指示灯,能够直观地显示电缆的工作状态,如链路状态和电源状态等。这种直观的设计使工程师能够快速识别并处理开发过程中遇到的问题,从而提升整体开发效率。

1.3 应用场景

SmartLynq Cable适用于多种开发场合,从原型设计到产品部署,都能提供有效的支持。尤其在需要进行频繁编程和调试的场合,如FPGA开发、原型验证及测试等,SmartLynq Cable能够大幅缩短产品开发周期,提高工程师的工作效率。此外,它的多协议支持能力也为开发者提供了极大的灵活性,能够兼容不同厂商的器件进行开发。

2. SmartLynq Cable与J-Link JTAG接口的结合应用

2.1 硬件接口的连接与兼容性

2.1.1 SmartLynq Cable与J-Link的物理连接方法

SmartLynq Cable是Xilinx公司推出的一种用于FPGA开发和调试的高速接口电缆,它允许设计者与JTAG接口进行连接。在进行硬件连接时,首先需要确保J-Link调试器和目标FPGA开发板都已经正确连接好电源并处于关闭状态。

SmartLynq Cable的连接方法如下:

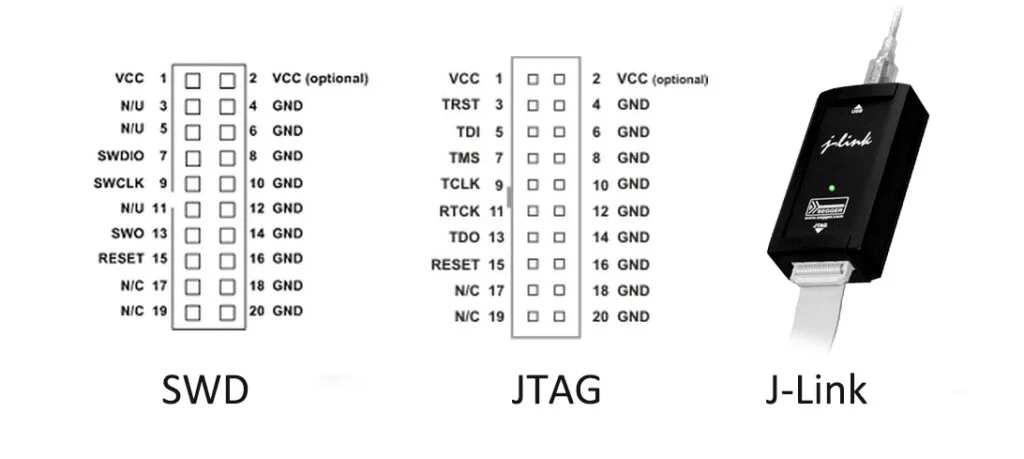

- 将SmartLynq Cable的JTAG接口一端与FPGA开发板上的JTAG接口相连接。JTAG接口通常是一个14针或20针的接口,具体取决于设计板的制造商和FPGA的型号。

- 确保连接器的针脚完全对齐,没有弯曲或损坏的针脚。

- 将SmartLynq Cable的另一端连接到J-Link调试器的对应JTAG接口上。

- 检查所有连接是否牢固,之后就可以打开电源并开始配置或调试FPGA。

这种连接方式的优势在于其快速和可靠的连接,同时避免了传统JTAG连接可能导致的信号质量问题。

2.1.2 接口兼容性分析与测试

接口兼容性是硬件连接成功的关键因素之一。对于SmartLynq Cable与J-Link的组合,以下几点需要特别注意:

- 电压匹配 :SmartLynq Cable和J-Link通常都工作在相同的电压电平上。开发板的电压电平应与SmartLynq Cable和J-Link的电压电平相匹配,否则可能会损坏设备。

- 引脚定义 :确认两者的引脚定义完全一致。不同的FPGA开发板可能会对JTAG引脚进行不同的定义,因此在进行连接前必须仔细核对引脚对应关系。

- 信号完整性 :要测试信号的完整性和稳定性,确保在高速通信时,信号不会因为长距离传输或连接不良而产生衰减或失真。

- 兼容性测试 :在连接之前,使用硬件测试仪器(如示波器)检查信号波形,确认信号质量和时序满足设计要求。

一旦验证了所有这些参数,就可以进行实际的硬件接口连接。SmartLynq Cable提供了即插即用的便利,极大的简化了硬件的配置过程。

2.2 软件层面的集成使用

2.2.1 集成开发环境中的配置步骤

SmartLynq Cable与J-Link的结合使用,不仅需要硬件连接的正确配置,还需要在软件层面进行配置以确保能够顺利的进行FPGA的配置和调试。

在集成开发环境(IDE)中配置步骤如下:

- 打开支持J-Link的集成开发环境,例如Keil uVision, IAR Embedded Workbench或者Eclipse等。

- 选择菜单中的“Project”选项,然后点击“Options”进入项目配置界面。

- 在“Debug”设置中,选择“J-Link”作为调试器。

- 在“Target”设置中,配置正确的硬件和时钟设置,这些设置必须与实际使用的硬件设备和SmartLynq Cable兼容。

- 在“Flash”设置中,配置用于编程和擦除操作的算法和设备参数。

- 点击“OK”保存配置,并确保连接的J-Link调试器能够被识别。

这一步骤确保了开发环境与硬件工具之间能够进行通信,为接下来的程序下载和调试工作打下基础。

2.2.2 跨平台开发工具的兼容性设置

在现代软件开发中,跨平台工具链的使用变得越来越普遍。为了实现SmartLynq Cable与J-Link在不同操作系统下的兼容性,以下是一些关键步骤:

- 下载并安装 :首先下载适用于目标操作系统的J-Link驱动程序和软件工具包。J-Link支持的操作系统包括Windows、Linux以及macOS等。

- 驱动程序安装 :按照操作系统对应的指导手册进行驱动程序安装。例如,在Windows系统中,通常需要运行安装程序并遵循向导提示;在Linux系统中,可能需要手动复制驱动到指定目录或使用包管理器进行安装。

-

权限配置 :在Linux和macOS系统中,通常需要配置相应的权限,以便用户可以访问J-Link设备。这通常涉及到修改

/etc/udev/rules.d/目录下的规则文件或使用sudo命令。 -

IDE软件配置 :在配置好操作系统和驱动程序之后,配置IDE软件以识别J-Link调试器。这可能涉及到安装特定的插件或库,以及在IDE中设置正确的路径以找到这些文件。

-

验证配置 :完成配置后,通过连接J-Link和测试设备来验证是否能成功识别调试器。这可以通过执行IDE中的“Detect”或“Connect”命令来实现。

通过这些步骤,SmartLynq Cable和J-Link可以顺利地集成到跨平台的开发工具中,方便用户在不同的操作系统下进行FPGA的开发和调试。

通过本章节的介绍,我们详细分析了SmartLynq Cable与J-Link JTAG接口在硬件和软件层面的集成应用。下一章节中,我们将探讨SmartLynq Cable利用高速USB 3.0接口带来的优势。

3. 高速USB 3.0接口优势

3.1 USB 3.0技术概述

3.1.1 USB 3.0技术标准和性能指标

USB 3.0,也被称为SuperSpeed USB,是一种在USB 2.0基础上发展起来的串行总线标准。它在2008年被引入市场,目的是提供比USB 2.0更快的数据传输速率和更好的电源管理功能。USB 3.0的理论最大传输速度为5 Gbps,是USB 2.0(480 Mbps)的10倍以上。

USB 3.0通过引入新的物理总线(即"SuperSpeed"通道)和协议框架来实现这种性能提升。除了速度提升,USB 3.0还提供了全双工通信能力,允许同时进行数据的发送和接收。它还引入了新的电源管理特性,使得设备能够在不需要的时候进入低功耗状态,从而更好地管理能源消耗。

3.1.2 与USB 2.0和其它接口的对比分析

与USB 2.0相比,USB 3.0的优势在于其更快的数据传输速度和更好的电源管理能力。对于需要快速传输大量数据的应用场景(例如,视频编辑、音频制作或大型文件的备份),USB 3.0可以显著减少等待时间,提升工作效率。

除了USB 2.0,比较常见的接口类型还有eSATA、Thunderbolt和FireWire。eSATA是一种传统的并行总线技术,尽管它的速度接近USB 3.0,但它没有USB接口那样方便的热插拔特性和丰富的供电功能。Thunderbolt和FireWire虽然提供了更高的数据传输速率和更丰富的功能,但它们的普及程度和设备兼容性不如USB 3.0广泛。

3.2 SmartLynq Cable的USB 3.0应用案例

3.2.1 数据传输速率测试与评估

SmartLynq Cable作为一种高速连接器,其USB 3.0版本在数据传输速率上的表现是非常令人瞩目的。在测试过程中,通过使用专业的数据传输软件(例如Iometer),我们可以对SmartLynq Cable进行一系列的性能测试。

测试通常会包括向连接的设备写入大量数据以及从设备读取数据,以此来评估其实际传输速率是否接近理论上的最大值。在多数情况下,SmartLynq Cable的表现都十分稳定,并且能够接近或达到USB 3.0的最大传输速率。

3.2.2 高速接口在FPGA配置与调试中的优势

FPGA(现场可编程门阵列)技术广泛应用于数字电路设计领域,要求高速的数据交换与配置能力。SmartLynq Cable通过其USB 3.0接口,为FPGA设备提供了高速的配置和调试解决方案。

例如,当使用SmartLynq Cable将FPGA设备连接到计算机时,可以实现非常快的配置文件传输速度,从而大幅减少系统上电和重新配置所需的时间。对于FPGA开发人员来说,这意味着可以更加频繁地进行设计迭代和测试,加快开发周期。

同时,SmartLynq Cable支持的高速数据流对于实时调试也是非常有帮助的。在FPGA的开发和调试过程中,需要频繁读写内存以及实时监测数据变化。通过高速USB 3.0连接,SmartLynq Cable能够提供更加流畅的调试体验,帮助开发者更准确地识别和解决问题。

| 参数 | USB 2.0 | USB 3.0 |

| --- | --- | --- |

| 最大传输速度 | 480 Mbps | 5 Gbps |

| 数据线数量 | 4 | 9 |

| 总线供电 | 支持 | 支持 |

| 全双工 | 不支持 | 支持 |

| 最大供电电流 | 500 mA | 900 mA |

表格比较了USB 2.0与USB 3.0在几个关键参数上的差异,反映了USB 3.0在传输速率和电源管理方面的显著提升。

通过以下mermaid流程图,我们可以了解USB 3.0在数据传输过程中与USB 2.0的对比:

graph LR

A[数据源] --> |USB 3.0| B[SmartLynq Cable]

A --> |USB 2.0| C[传统USB Cable]

B --> |高速传输| D[目标设备]

C --> |低速传输| E[目标设备]

该图描述了数据源通过USB 3.0和USB 2.0两种不同的接口与目标设备连接的场景。从中我们可以清晰地看到,通过SmartLynq Cable实现的USB 3.0连接方式在数据传输上具有明显的优势。

#include <stdio.h>

#include <sys/time.h>

int main() {

struct timeval start, stop;

double duration;

gettimeofday(&start, NULL);

// 数据处理过程

gettimeofday(&stop, NULL);

timersub(&stop, &start, &start);

duration = start.tv_sec + start.tv_usec/1000000.0;

printf("Duration: %f seconds\n", duration);

return 0;

}

上述代码示例展示了一个简单的计时程序,用于测量特定操作的执行时间。开发者可以在FPGA配置和调试过程中使用类似的代码片段,来评估使用SmartLynq Cable的USB 3.0连接与传统USB 2.0连接相比的性能差异。通过计算数据处理前后的系统时间差,开发者可以对两种不同接口的性能进行准确的比较。

在上述代码块中, gettimeofday 函数被用来记录操作前后的时间戳,然后通过减法运算计算出执行时间。这种简单的计时方法可以为开发者提供关键性能指标,从而在性能优化方面做出更加明智的决策。

4. JTAG和SWD协议兼容性

JTAG(Joint Test Action Group)和SWD(Serial Wire Debug)是两种常见的调试和测试协议,广泛应用于微电子领域。JTAG协议历史悠久,拥有广泛的硬件支持和应用,而SWD作为其更高效的替代方案,在一些新设备上越来越受欢迎。

4.1 JTAG和SWD协议基础

4.1.1 JTAG协议的工作原理

JTAG是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。它支持芯片的边界扫描功能,可以在不使用传统测试针床的情况下,进行芯片的测试。JTAG协议通过一系列连接起来的寄存器(链)来实现对芯片内部的访问。

JTAG协议涉及以下几个关键概念:

- TAP(Test Access Port)控制器 :它是JTAG协议的核心,负责管理测试访问链。

- TDI(Test Data In) 和 TDO(Test Data Out) :这两个信号用于数据的输入输出。

- TCK(Test Clock) :提供时钟信号。

- TMS(Test Mode Select) :用于控制TAP的状态机。

JTAG工作时,通过一系列的时钟周期和TMS状态转移,在TAP控制器的状态机中移动,实现数据的扫描输入和输出。

4.1.2 SWD协议的特点和应用场景

SWD是基于ARM公司的2-pin串行线协议,用以替代JTAG进行调试。相比JTAG,SWD使用两条数据线(SWDIO和SWCLK),大大减少了所需的针脚数量,特别适合在引脚数量受限的设备上使用。

SWD协议的显著特点包括:

- 高效率 :数据传输更加高效,减少了通信时间。

- 较低的功耗 :由于引脚数量的减少,降低了设备的功耗。

- 灵活性 :SWD可与JTAG共存,便于向后兼容。

SWD主要应用场景包括:

- 对ARM内核进行调试。

- 使用SWD进行非侵入式调试,特别是在I/O引脚较为紧张的应用场合。

4.2 SmartLynq Cable的协议兼容性分析

4.2.1 SmartLynq Cable支持的协议模式

SmartLynq Cable是一种用于Xilinx FPGA开发和调试的高性能编程电缆,它支持多种通信协议。它不仅能够使用JTAG进行常规的FPGA配置和调试,还能够支持SWD协议,这意味着它能够与广泛的设备进行交互,包括采用ARM架构的微控制器。

SmartLynq Cable的协议支持包含:

- 标准JTAG模式 :支持IEEE 1149.1标准。

- SWD模式 :为ARM Cortex-M系列等提供专用的调试接口。

- 混合模式 :同时支持JTAG和SWD协议。

4.2.2 协议兼容性在实际应用中的优势与限制

优势 :

- 扩展性 :SmartLynq Cable的协议兼容性允许开发者使用统一的工具链与多种芯片进行交互,减少了为不同协议准备不同硬件的需要。

- 灵活性 :开发人员可以根据需要选择更适合当前项目的协议,比如在调试ARM处理器时选择SWD以获取更高的效率,在进行FPGA调试时使用JTAG。

- 优化调试与配置流程 :协议的兼容性也意味着可以在同一调试工具上实现更流畅的开发工作流,减少了切换和设置的复杂性。

限制 :

- 硬件成本 :虽然使用SmartLynq Cable能够减少额外硬件的需求,但是它本身的价格可能比单一协议的电缆高。

- 学习曲线 :需要开发人员了解不同协议的特点,以便更好地利用它们的优势。

- 兼容性问题 :如果目标硬件对协议的支持存在限制,可能会影响调试和配置过程。

接下来,我们将进一步探讨J-Link JTAG功能和优势,以及如何与SmartLynq Cable协同工作,实现更为高效的FPGA配置和调试流程。

5. J-Link JTAG功能与优势

5.1 J-Link JTAG调试器的功能解析

5.1.1 J-Link JTAG调试器的主要功能和特点

J-Link是SEGGER公司开发的一款广泛应用于嵌入式系统调试的JTAG接口工具。它具备众多强大的功能和特点,使得它在行业内部得到了广泛的应用和认可。其中,一些主要的功能和特点包括:

- 快速处理器支持 :支持所有主流的处理器,包括ARM, Cortex-M, 8051, AVR, Xilinx等。

- 高性能下载速度 :J-Link能够提供远高于传统调试器的下载速度,这对于需要频繁更新程序和固件的开发者来说是一个巨大的优势。

- 实时跟踪 :J-Link能够提供实时的指令跟踪,允许开发者实时地观察代码的执行流程。

- 多调试接口兼容 :支持SWD(Serial Wire Debug),JTAG等多种调试接口,方便在不同硬件上使用。

- 跨平台支持 :能够在多种操作系统上工作,包括Windows、Linux、Mac OS等。

5.1.2 J-Link与其他调试器的性能比较

在选择调试工具时,对比不同调试器的性能是至关重要的。以下是一些比较J-Link与其他调试器时需要考虑的关键性能指标:

- 启动时间 :J-Link启动和连接到目标设备的速度非常快,通常在几秒之内完成。

- 调试速度 :由于J-Link的高速USB 2.0和硬件加速技术,它的调试速度可以达到其他调试器的数倍。

- 用户界面 :J-Link的用户界面直观,操作简单,使得新手和专家都能快速上手。

- 软件支持 :SEGGER提供丰富的软件支持,包括J-Link调试软件、J-Flash编程工具、J-Trace跟踪分析工具等。

- 社区支持与文档 :SEGGER维护了一个广泛的开发者社区,提供详尽的文档和教程,以便开发者能够充分利用J-Link的强大功能。

5.2 SmartLynq Cable与J-Link的协同工作

5.2.1 实现FPGA配置、调试的步骤与技巧

SmartLynq Cable与J-Link的结合应用为FPGA的配置和调试提供了一种灵活而强大的解决方案。下面是一些实现此协同工作的步骤与技巧:

- 步骤一 :确保SmartLynq Cable和J-Link驱动程序已经正确安装在开发计算机上。

- 步骤二 :使用Xilinx的开发环境(如Vivado)生成FPGA配置文件(bitstream)。

- 步骤三 :通过SmartLynq Cable连接J-Link和FPGA板,准备下载配置。

- 步骤四 :打开J-Link Commander或Vivado中的配置工具,选择正确的设备和接口。

- 步骤五 :加载bitstream文件,通过J-Link向FPGA发送配置数据,并确保配置成功完成。

- 技巧 :在配置过程中,监控JTAG链路状态,确认各设备响应正常。如果出现问题,检查物理连接和配置文件是否正确。

5.2.2 SmartLynq Cable与J-Link组合的优化策略

SmartLynq Cable与J-Link的组合不仅仅在于简单的连接和配置,更在于如何优化使用体验和提高工作效率:

- 策略一 :根据项目需求调整下载速度和稳定性之间的平衡,如在需要快速迭代时提高下载速度。

- 策略二 :利用J-Link的多核调试能力,对FPGA内的多个处理器或IP核同时进行调试。

- 策略三 :使用J-Link的高级调试功能(例如断点、数据监控、性能分析等)来深入理解和优化FPGA上运行的应用程序。

- 策略四 :保持J-Link软件和固件的更新,以确保对新硬件的支持,并利用最新的性能改进。

在第五章中,我们深入探讨了J-Link JTAG调试器的强大功能,以及如何与SmartLynq Cable协同工作来实现FPGA的配置和调试。接下来,我们将转到下一章节,详细了解如何安装驱动程序和配置Xilinx开发工具链。

简介:Xilinx SmartLynq Cable作为新一代仿真器,通过与J-Link JTAG接口结合,为FPGA开发者提供了一个高效、便捷的开发和调试体验。本手册详细阐述了如何使用SmartLynq Cable,包括其支持的高速数据传输、多种协议兼容性,以及与J-Link JTAG接口的集成优势,从而提升开发效率和问题定位能力。同时,提供了关于安装驱动程序、配置FPGA、进行硬件调试的指导和建议。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?