本篇分析vivado分析hold time的方法,hold time 比较难理解,如图一所示,

图一

它的意思是reg1的输出不能太快到达reg2,这是为了防止采到的新数据太快而冲掉了原来的数据。保持时间约束的是同一个时钟边沿,而不是对下一个时钟边沿的约束。reg2在边沿2时刻刚刚捕获reg1在边沿1时刻发出的数据,若reg1在边沿2时刻发出的数据过快到达reg2,则会冲掉前面的数据。因此保持时间约束的是同一个边沿。

在时钟沿到达之后,数据要保持Thold的时间,因此,要满足:

Tdata_path = Tco + Tlogic + Trouting ≥ Tskew + Thold

上面一段摘抄自别的文章,对于这个公式,Tskew为时钟到达目的寄存器时延和到达源寄存器时延的差值。

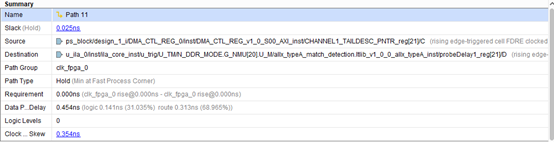

下面拿一条路径为例,研究vivado分析hold time的时序路径方法。如图二所示,

图二

Source为 图一中reg1的 C端,Destination为图二中reg2的D端,

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1969

1969

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?