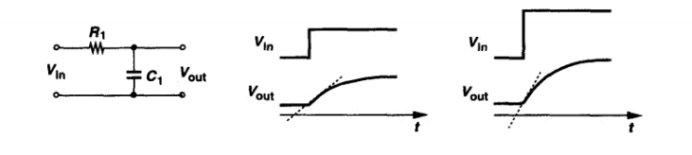

一阶系统的单位阶跃响应

最简单的就是RC响应。阶跃响应的S函数为1/S.系统传递函数为1/(1+SRC)。可以得到最终的Vout S域传输函数,转化为时域响应为:

前面一段为Slew rate,为大信号响应,后面一段为小信号响应,在adc设计中,往往前面有buffer存在,需要把buffer的输入信号跟输出信号的偏差小于LSB/2,才能使ADC的性能不受影响。

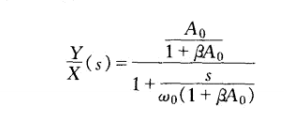

如果buffer 是单极点运放组成的buffer,运放的开环增益为A0/(1+S/W0),则整个buffer的闭环增益为:

如果β=1,则闭环增益为1/(1+S/A0/W0),对比RC响应,A0W0跟 1/RC在同一位置。所以单极点运放的闭环响应跟RC响应一致。而且注意到A0W0就是这个运放的GBW。所以如果我们能够确认经历多少个Γ后输入和输出偏差小于LSB/2的电压,那么我们就可以确定这个buffer的GBW指标。

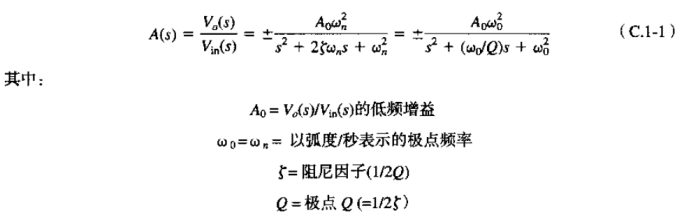

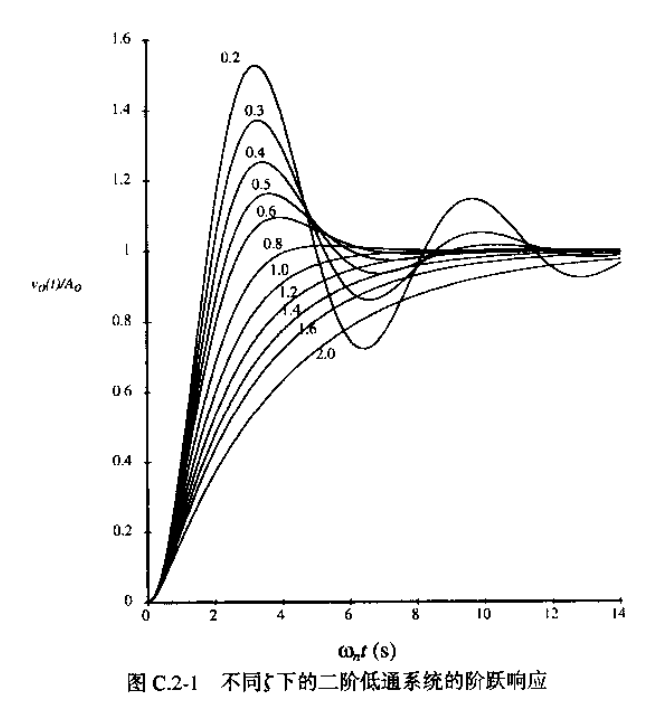

二阶系统的单位阶跃响应

如果运放有两个极点,一个极点在GBW带宽内,一个极点在GBW 带宽外,形成二阶系统,它的闭环传输函数为:

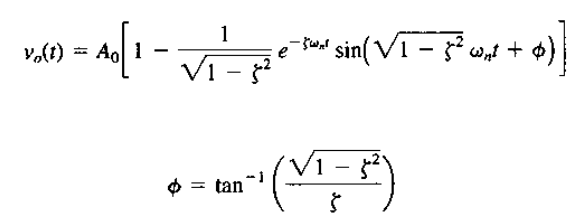

它的二阶系统的单位阶跃响应为:

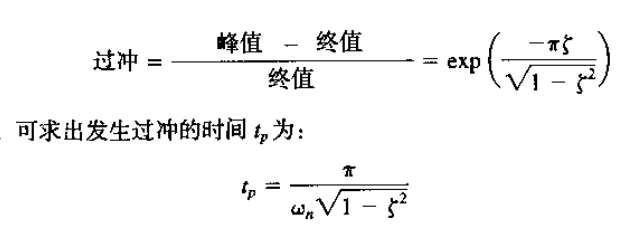

当ζ<1时,知道过冲tp的值,就可以求出Wn。

知道了ζ和Wn,就可以求出相位裕度和单位增益带宽的值,从而说明时域分析和频域分析可以一一对应起来。

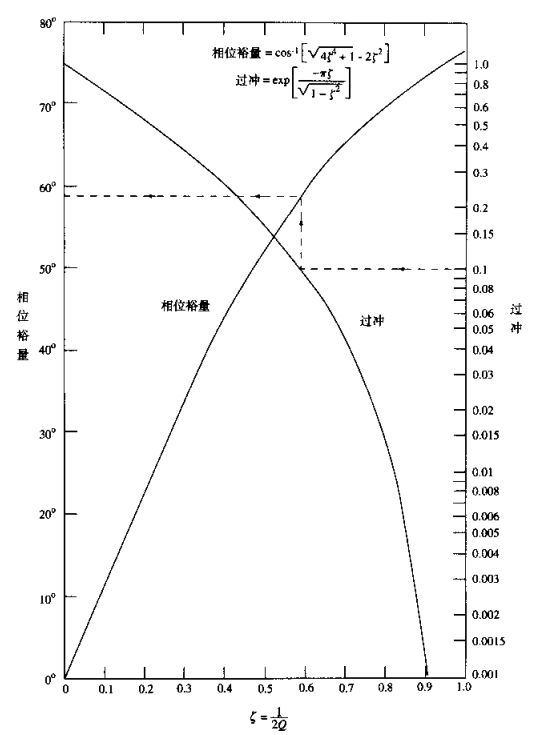

刚刚看了一个两极点的运放系统,现在看一个PLL系统

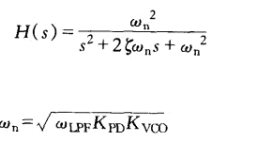

一阶锁相环,它的闭环传递函数为:

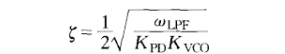

转换为ζ和Wn为:

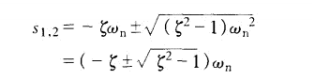

两个极点为:

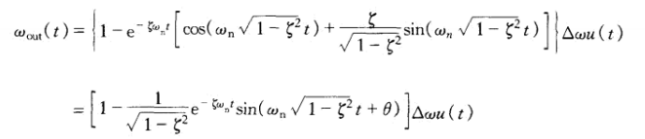

它的单位阶跃响应为:

可以看到PLL和运放的单位阶跃响应表达式是一样的。所以理解了运放系统就很容易理解设计PLL系统,因为它们的理论基础是一样的。

864

864

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?