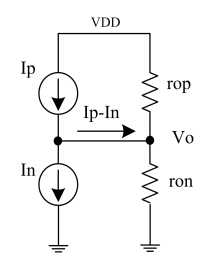

差分运放的输出一般由PMOS和NMOS 管组成,由于工艺偏差等原因,Ip和In 电流不一定相等,当Ip>In,Vo往上升到VDD,PMOS进入线性区;当Ip<In,Vo往下走到GND,NMOS管进入线性区,导致差分运放无法正常工作,所以需要共模反馈电路,使PMOS和NMOS均工作在饱和区。

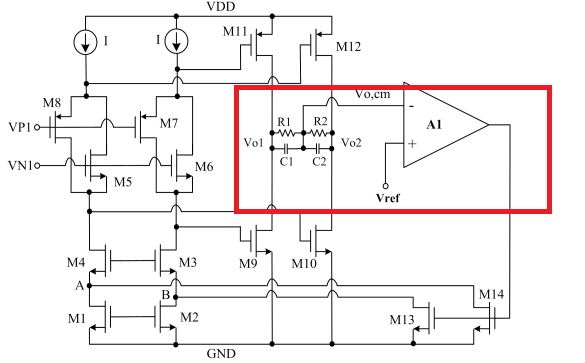

共模反馈电路一般有三个工作流程组成,如上图红框部分:1)先检测输出共模电压 2)将检测到的共模电压跟Vref 比较 3)将得到的误差反馈给放大器的偏置电流。

共模反馈电路主要分两种架构:连续时间共模反馈和离散时间共模反馈。

连续时间共模反馈架构主要是电阻分压的结构,如上图所示,它的优缺点如下:

1)电阻R1和cm-sense 电路的输入电容Cp形成一个极点,可通过并联一个电容C1的方法,引入一个左半平面的零点,来减小高频极点的影响。其表达式为:(1+SR1C1)/(1+SR1(C1+Cp)),如果要做到零极点抵消,C1/Cp要取一定值以上。

2)电阻会减小开环差动增益,可source buffer 来解决问题,但会限制摆幅,还带来一定的offset。

3)线性范围大,无论差模输出电压多大,提取的共模电压始终是(Voutp+Voutn)/2

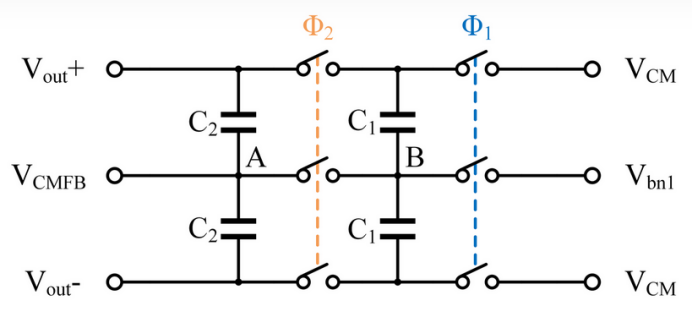

离散时间共模反馈架构主要是开关电容结构,如上图所示,它的优缺点如下:

1)没有输出swing 限制

2)没有阻性的负载效应

3)需要非交叠时钟

4)时钟馈通注入噪声

5)sc-cmfb 的仿真,与开关电容电路类似,主要是pss-pac仿真的方法或者做tran仿真,在option里填写actimes和acnames做ac或stb仿真,比较复杂。

一般共模反馈的方法时控制放大器的电流源,这里如果是fold cascade结构,可以考虑用CMFB控制cascade的电流源而不是输入差分对的电流源,因其在共模环路中较少的节点,所以更容易补偿。

从性能上讲,希望共模反馈的单位增益足够大,但由于CMFB的环路相较于差模通路可能有更多的高频极点,故一定的功耗要求下,其共模GBW一般难做的高。一般是差模GBW的1/3。

对于CMFB控制cascade电流源,可以将cascade电流源分为两半,其中一半用CMFB控制,一半接恒定的偏置电流。这里拆分cascade电流来减小共模环路的gm,这样共模GBW减小,相位裕度增加,另外,恒定偏置部分也可以帮助共模电压的初始建立,减小CMFB大的扰动。

4564

4564

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?