拆解文献:《a digital clock and data revovery architecture for multi gigabit binary links》

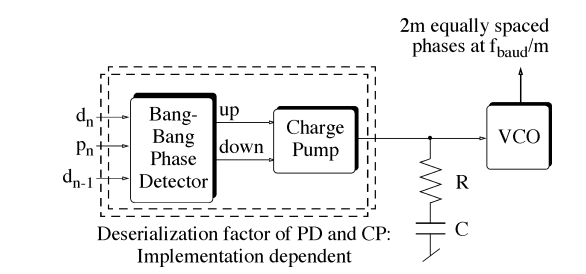

模拟CDR 由BBPD、Charge Pump、RC LPF、VCO组成,BBPD有时候工作在serdes 速率上。下图是模拟CDR的组成。由于BBPD 只能鉴相,所以需要额外的鉴频电路。一般是先通过PFD+CP+LPF+VCO的PLL环路,先让系统把频率锁定,然后再切换到BBPD+CP+LPF+VCO环路中去,其中CP+LPF+VCO环路可以复用。

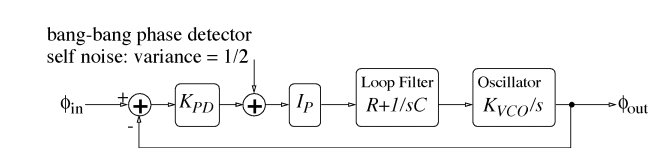

上图中的环路线性模型如下:

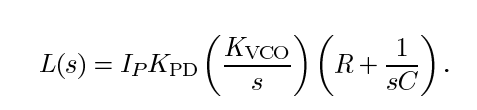

上图的传输函数为:

由于数字可以有更低的功耗,更好的工艺迁移特性,我们试着把模拟CDR 转变成数字CDR。需要把传输函数从S域转成Z域。

因为e^x 用泰勒级数为1+x+x2/2+…+xn/n!+…,从而推出Z^(-1) =Z^(-ST) 约等于1-sT或者1-sT+s^2 T^2 /2,T为采样周期,ST远小于1.一般CDR和PLL的带宽远小于fs,因此一般系统就可以用Z^(-

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8617

8617

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?