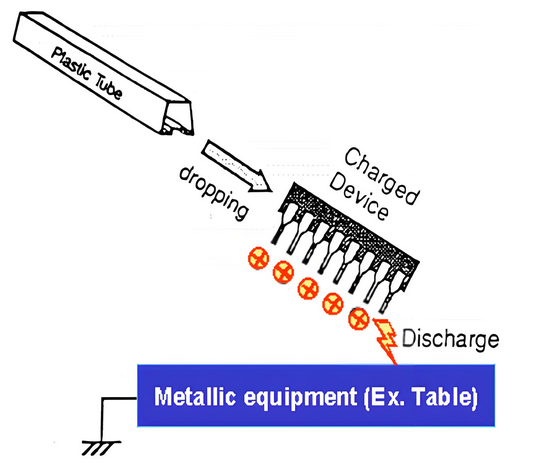

在电子产品的设计与生产过程中,静电放电(ESD)是一个不可忽视的问题。其中,带电器件模型静电放电CDM(charge device mode)是一种常见的ESD现象,特别是在芯片面积比较大,先进工艺上更容易发生。

CDM的主要原理

芯片因为摩擦生电或其他因素导致其自身内部积累了大量电荷。在这个过程中,芯片并未立即受损。然而,当这个带有静电的芯片在处理过程中,其引脚与接地电位(如金属机壳、工具等)接触时,芯片内部的静电会迅速从引脚流出,形成静电脉冲,即CDM放电。

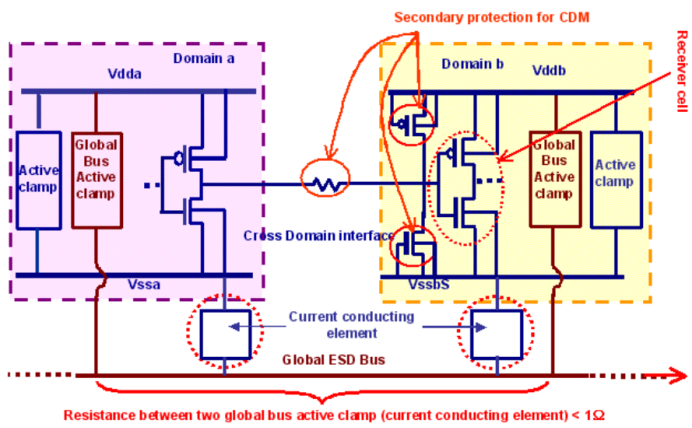

CDM保护结构如下:

如果芯片内部没有CDM 保护机制,则地金属线上domain b 域中vssb积累的电荷就会通过NMOS管栅极漏电流,再经过Domain a 域中的PMOS的寄生二极管到Vdda,Vdda再经过Global Bus active clamp泄放到全局ESD地(Global esd bus)。这样NMOS的栅极就会被打坏。电源金属线上domain b 域中vddb积累的电荷,也是类似的道理。由于先进工艺栅氧比较薄,很容易被击穿,所以需要加电阻来减小栅漏电流,同时加GGMOS ESD保护器件来保护栅极。

设计需考虑以下事项:

1)GGMOS的放置需尽可能的离需保护的器件近

2)需要用跟保护器件同样的地和电源,还有阱。

3)Global bus active clamp 需尽可能放在cross domain interface 接口附近,从而更快的泄放电流

4)两个Global bus active clamp之间的global esd bus线要小于1Ω电阻

5)Esd 电阻阻值要大于200Ω

6)有时因为面积的原因,会省去GG_PMOS,主要原因是一般VDD的金属线面积比较小,所以积累的电荷能量小。同时GG_NMOS 比GG_PMOS 相比,NMOS比PMOS的电子迁移率更高,ESD特性更好,更喜欢用GG_NMOS.

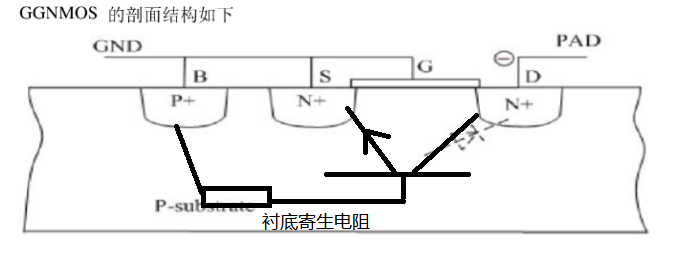

GGNMOS的工作原理如下:

当PAD 端聚集大量的负电荷时,通过PN结二极管,电荷通过Psub由B端泄放到GND。

当PAD端聚集大量的正电荷时,利用寄生的三极管把电荷泄放掉。

1)大量的正电荷聚集在Drain端,正电荷通过Drain和Psub之间的反偏PN结转移到Psub,这部分正电荷聚集到同为P型材料的B端,转移到GND,形成电流I

2)上面的电流I与衬底寄生电阻形成正压降,使衬底psub与source形成得PN结导通

3)寄生的三极管被打开,大量的正电荷通过gate 下面的区域迅速由Drain端转移到source端,聚集的正电荷得以快速的泄放到地

2178

2178

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?