目录

CDM ESD Protection in 90-nm CMOS

A Multi-ESD-Path in 65-nm CMOS

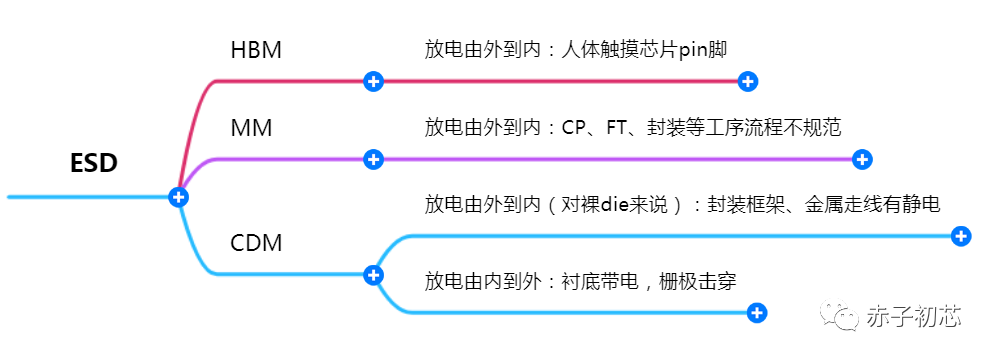

ESD类型回顾

A 24 GHz Low-Noise Amplifier Using RF Junction Varactors for Noise Optimization and CDM ESD Protection in 90-nm CMOS

Ming-Hsien Tsai, Student Member, IEEE, and Shawn S. H. Hsu, Member, IEEE

SOC芯片通常采用先进的CMOS工艺制程,具有比以前更薄的栅极氧化物和更大的芯片尺寸,大的衬底可能积累大量的电荷,导致CDM事件期间的高ESD放电峰值电流。传统CDM保护器件使用栅极接地NMOS被添加到输入级的栅极。然而,这种方法通常会在信号路径上引入显著的寄生电容,这不适合RF应用。

变容二极管被用作ESD保护器件,并与90nm CMOS中24GHz的LNA核心电路共同设计,ESD保护、噪声系数、增益和功耗共同优化。变容二极管与输入匹配网络共同设计,具有源极电感退化的共源共栅LNA具有减少米勒效应、改善输入/输出隔离、增强放大器稳定性以及同时进行噪声和输入匹配的可能性的优点。

本文探讨了在90nm和65nm CMOS工艺中针对CDM ESD(静电放电)保护的电路设计策略。通过使用RF变容二极管优化了24GHz低噪声放大器的噪声系数和ESD保护,同时在65nm工艺中设计了一种多ESD路径低噪声放大器,以承受4.3A的TLP电流。全芯片ESD防护方案包括二极管、RC钳位电路和栅极接地的NMOS,以提供全方位的ESD保护,同时兼顾芯片性能和面积效率。

本文探讨了在90nm和65nm CMOS工艺中针对CDM ESD(静电放电)保护的电路设计策略。通过使用RF变容二极管优化了24GHz低噪声放大器的噪声系数和ESD保护,同时在65nm工艺中设计了一种多ESD路径低噪声放大器,以承受4.3A的TLP电流。全芯片ESD防护方案包括二极管、RC钳位电路和栅极接地的NMOS,以提供全方位的ESD保护,同时兼顾芯片性能和面积效率。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2489

2489

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?