目录

MOSFET击穿电压-Drain(漏极)->Source(源极)穿通击穿

MOSFET击穿电压-Drain(漏极)->Bulk雪崩击穿

MOSFET击穿电压-Drain(漏极)->Gate(栅级)击穿

基本概念

ESD(Electro-Static discharge)的意思是“静电释放”,在芯片的制造、运输、使用过程中,芯片的外部环境或者内部结构会积累一定量的电荷,这些积累的电荷会瞬间通过芯片的管脚进入集成电路内部,峰值电流可以达到数安培,也可能有几百伏甚至成千上万伏电压。EMI(Electromagnetic Interference)是电磁干扰,EMC(Electro Magnetic Compatibility)包括EMI和EMS,是“电磁兼容性”,指设备或系统在其电磁环境中符合要求运行并不对其环境中的任何设备产生无法忍受的电磁干扰的能力,和ESD注意区分。

ESD产生来源

1、人体放电模式(HBM,Human Body Model):人体通过摩擦等方式积累了静电,再去碰触芯片时,人体上的静电便会经由芯片的PIN脚进入芯片内部,再经由芯片放电到地。

2、机器放电模式(MM,Machine Model):机械手臂等设备本身积累了静电,当机器碰触芯片时,该静电便经由芯片的PIN脚放电。

3、元器件充电模式(CDM,Charge Device Model):芯片先因磨擦或其他因素而在内部积累了静电,但在静电积累的过程中芯片暂未受到损伤。这种带有静电的芯片在处理过程中,当其PIN脚碰触到接地面时,内部的静电便会经PIN脚自IC内部形成放电,此种模式的放电时间可能只在几ns内。

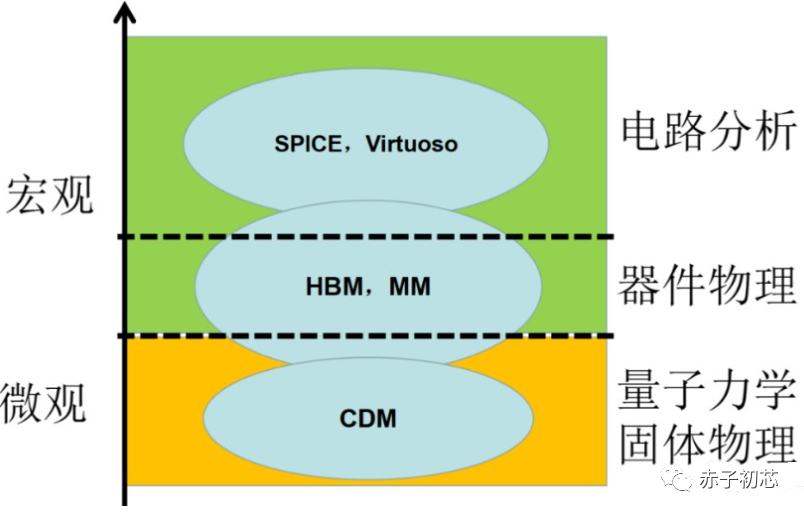

HBM和MM都是由外而内的ESD事件,静电流是由芯片外部灌入内部,所以针对HBM和MM的防护主要集中在IO。而CDM是器件内部向外部放电,脉冲时间短,所以CDM防护的重点是建立低寄生电容的泄放通道,CDM幅值虽然很高,但是其防护电路不需要很大的面积,只需要能及时将积聚在半导体衬底材料内的载流子泄放出去。片外ESD保护器件常见的有陶瓷电容、齐纳二极管、肖特基二极管、MLV(Multi-Layer Varistor,多层变阻器)和TVS (Transient Voltage Suppresser 瞬态电压抑制器)。片上集成ESD 防护电路的难度较大,工艺进步使MOS管的栅极氧化层厚度越来越薄,芯片自身的ESD防护能力降低。湿度是影响静电电荷积累的重要因素,适当增加湿度可降低ESD电压。

HBM测试模式

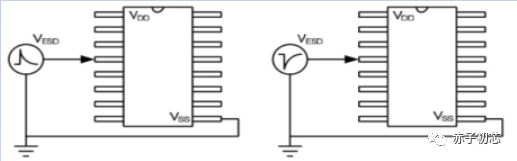

静电的积累可能是正或负电荷,静电放电测试对同一PIN脚而言是具有正、负两种极性。进行ESD测试时,针对I/O PIN与电源和地之间发生ESD的情形,有下列四种组合:

PS mode:VSS引脚接地,正的ESD电压出现在I/O PIN并对VSS脚放电,此时VDD与其它PIN脚浮空。

NS mode:VSS引脚接地,负的ESD电压出现在I/O PIN并对VSS脚放电,此时VDD与其它PIN脚浮空。

PD mode:VDD引脚接地,正的ESD电压出现在I/O PIN并对VDD脚放电,此时VSS与其它PIN脚浮空。

ND mode:VDD引脚接地,负的ESD电压出现在I/O PIN并对VDD脚放电,此时VSS与其它PIN脚浮空。

ESD也有可能发生在任意的I/O引脚之间,若两只PIN脚之间无直接的相关电路,静电放电电流会先经由某部分的电路到VDD或VSS电源线上,再由VDD或VSS电源线到另一引脚流出芯片。

引脚对引脚正向Mode:引脚施加正的ESD电压,其余所有1/0引脚一起接地,VDD和VSS引脚悬空。

引脚对引脚反向Mode:引脚施加负的ESD 电压,其余所有1/0引脚一起接地,VDD和VSS引脚悬空。

ESD失效判断方式

1、绝对漏电流:当IC进行ESD测试后,在其 I/O PIN上加一定电压,漏电电流超过规定值,即可认为ESD失效。

2、相对I-V漂移:当IC进行ESD测试后,其 I/O PIN的I-V曲线漂移超过规定值,即可认为ESD失效。

3、功能判断:当IC进行ESD测试后,其 I/O PIN的功能已经不满足性能规格,即可认为ESD失效。

ESD保护电路要求

1、当ESD 冲击出现时,ESD保护器件能够快速开启,高效泄放冲击大电流,钳位到安全电压。

2、在ESD 冲击下具有一定程度的鲁棒性,确保ESD保护电路自身能够承受外部冲击。

3、当芯片处于正常工作状态时,ESD保护器件处于关闭状态,不影响电路正常功能。

4、ESD保护电路一般在IO pad的周围,需保证较小的IO延迟。

ESD保护电路设计

最经典的电压钳位电路便是单个二极管,其IV特性如图所示,但无论是正向工作的开关、整流二极管,还是反向工作的稳压二极管,单个二极管会有钳位电压Vclamp不稳定,寄生电容大,漏电流大,电路鲁棒性差等缺陷。

图 二极管IV曲线

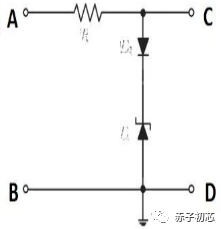

之后又提出了其他钳位电压结构,如图所示,将正向二极管串联反向稳压二极管,该结构能降低部分寄生电容,但是钳位电压受工艺影响较大。图中的电阻是1.5k,HBM仿真时作为人体等效电阻。

图 一种电压钳位结构

ESD

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?