DAC的逻辑选择参考该如何选择呢?直观感受需要满足下面几个点

1)要满足SAR ADC的比较原理,对于单端要满足单端输入信号第一次跟1/2*(Vrefp+Vrefn),第二次跟1/4*(Vrefp+Vrefn)或3/4*(Vrefp+Vrefn)比较,以此类推。

2)要满足SAR ADC的比较原理,对于差分要满足差分输入信号第一次两个互比,第二次跟+/-1/2*(Vrefp-Vrefn)比较,以此类推。Vrefn要为0

3)DAC 浮空电压不能超过比较器输入管耐受电压的最大值

所以我们可以来尝试一下DAC的逻辑选择参考设计

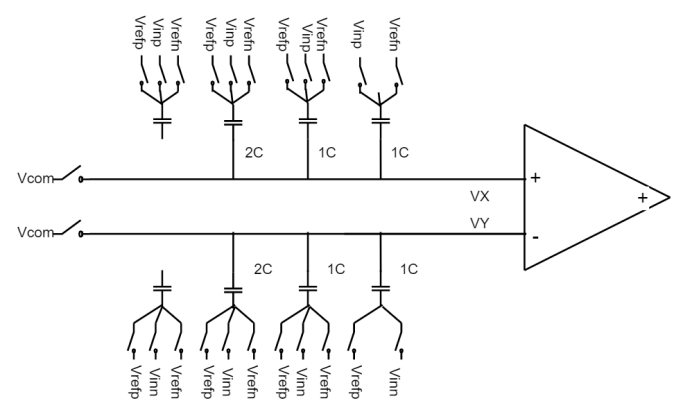

采样阶段:接Vin的开关闭合,接Vcom的开关闭合

采样时刻的总电荷为:(Vinp-Vcom)*4C(1)

(Vinn-Vcom)*4C(2)

转换阶段:

接Vinp的开关断开,上面一排cap最高位接Vrefp,其它位接Vrefn,另外,接Vcom的开关断开,DAC输出浮空为Vx;

接Vinn的开关断开,下面一排cap最高位接Vrefn,其它位接Vrefp,另外,接Vcom的开关断开,DAC输出浮空为Vy;

第一次转换的总电荷为:(Vrefp-Vx)*2C+(Vrefn-Vx)*2C (3)

(Vrefn-Vy)2C+(Vrefp-Vy)2C (4)

根据电荷守恒原理ÿ

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?