SerDes(串行器/解串器)底层硬件的演变以及两种差分信号技术:LVDS(低电压差分信号)和CML(电流模式逻辑)。我们逐步详细解释

1. SerDes底层硬件的早期发展:LVDS与CML

-

LVDS(Low Voltage Differential Signaling):

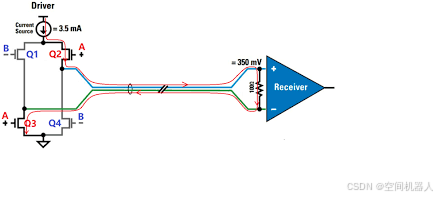

- LVDS是早期用于SerDes信号传输的一种差分信号技术。它的主要特征是以较低电压(通常约为350 mV)的形式在一对信号线中传输差分信号,具有低功耗、低电压摆幅和抗干扰能力强的特点。LVDS技术工作在155 Mbps到1.25 Gbps的速率范围内,适合中高速信号传输。

- LVDS的差分信号传输方式意味着两根线上的信号相位相反,幅度相等,这种结构可以抵抗电磁干扰(EMI),使信号能够在较远的距离上传输,同时保持低噪声特性。这是LVDS在SerDes技术早期被广泛使用的原因之一。

-

CML(Current Mode Logic):

- 随着数据速率的提高,LVDS逐渐不能满足更高带宽的需求,因此CML(电流模式逻辑)成为更高带宽SerDes的首选。CML是一种高频信号传输技术,它通过电流驱动的方式传输信号,能够在600 Mbps到10 Gbps及以上的速率范围内稳定工作。与LVDS相比,CML具有更好的信号完整性,特别是在更高的频率下能够保持较低的噪声和失真。

- 由于CML技术可以支持更高的数据传输速率,因此它逐渐取代LVDS,成为现代SerDes技术中的主流方案,尤其是在需要传输大量数据的应用场景中(如高速数据通信、光纤网络等)。

2. LVDS和CML信号可以互通,但需要电平转换

尽管LVDS和CML是两种不同的差分信号传输技术,它们的基本工作原理相似(都是通过差分

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

108

108

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?