CLB(Configure Logic Block):可编程逻辑单元

CH1. 总述

- 一个CLB包含两个slice,slice类型为 两个slice L 或是 一个slice L和slice M。所有CLB中slice L和slice M的比例约为2:1。

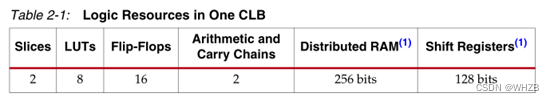

- 一个CLB所含资源如下表所示。每个slice包括:4个LUT、8个存储资源、多路复用器、进位逻辑。

CH2.功能细述

Slice

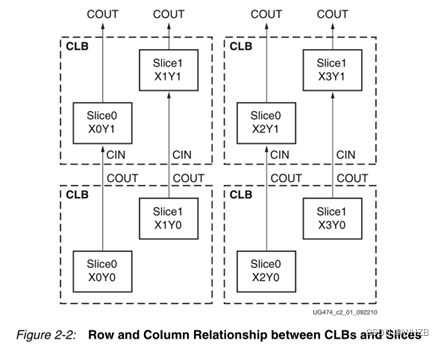

一个CLB中的slice没有直接连接,每个slice各成一列,每个slice都有独立的进位链(Carry chain),如下图所示。

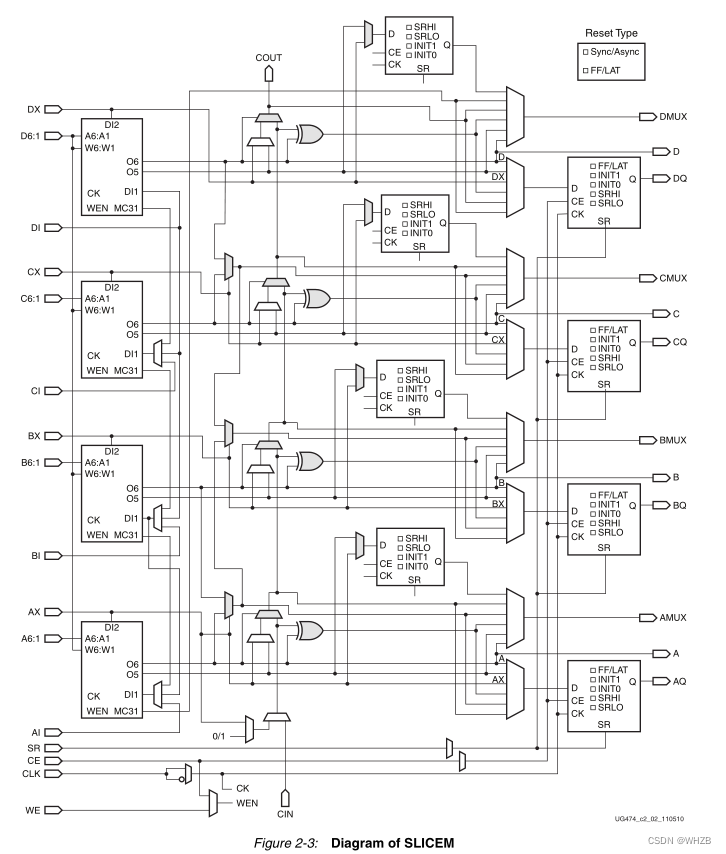

slice M中的LUT可以用作64bit的分布式RAM或是32位移位寄存器(SRL32)或是SRL16,可读可写。SliceL中的LUT不可用作RAM、SRL32和SRL16,只读。

LUT

LUT6由两个LUT5组成,如下图所示。因此,LUT可以配置成LUT6,或是具有单独输出但具有公共地址或逻辑输入的两个LUT5。

每个LUT5由一个触发器(FF, Flip-flops)驱动。每个slice有4个LUT6和8个FF,与上表一个CLB所含资源数一致。

Storage Elements

每个slice有八个存储单元。

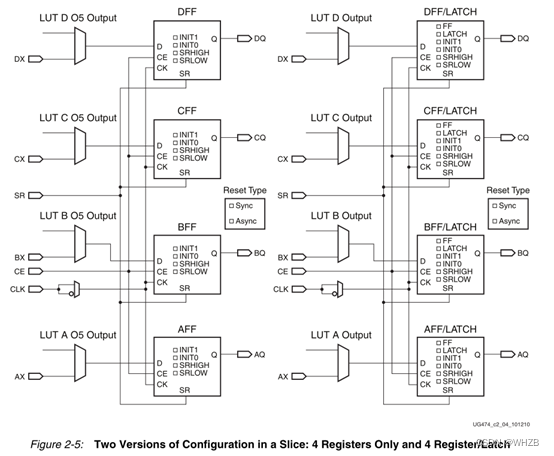

四个可配置成边缘触发D型触发器或电平敏感锁存器。

另外四个附加的存储元件只能配置为边缘触发D型触发器。当四个触发器配置成锁存器时,另外四个不能使用。

控制信号:时钟(CLK)、时钟使能(CE)、置位或复位(SR)。

CE和SR是高电平有效。

SRLOW:当SR有效时同步或异步复位;

SRHIGH:SR有效时同步或异步置位;

INIT0:通电异步复位或全局置/复位;

INIT1:通电异步置位或全局置/复位。

Distributed RAM (Available in SLICEM Only)

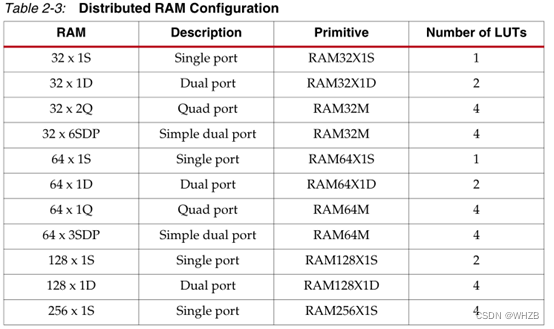

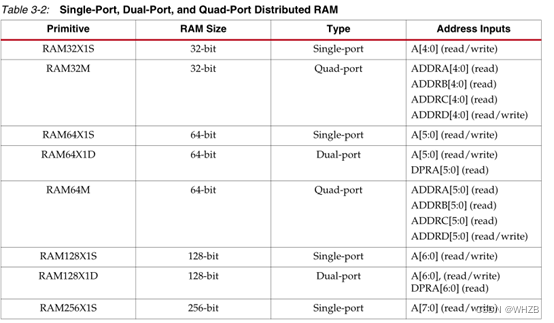

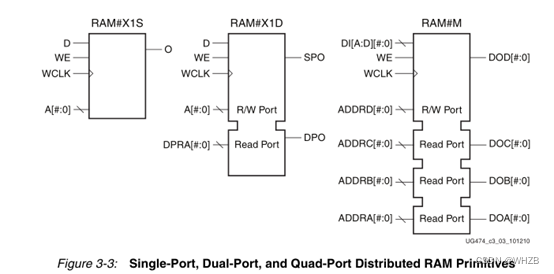

一个sliceM中可配置的RAM类型如下表所示。

分布式RAM同步写入,写入操作需要一个时钟沿,异步读取。

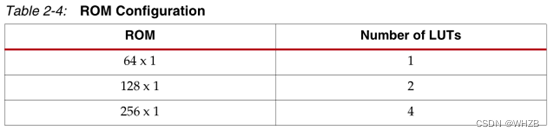

Slice L和Slice M都可以实现64bit ROM,有三种ROM可实现,配置和占用LUT数量如下:

Shift Registers (Available in SLICEM Only)

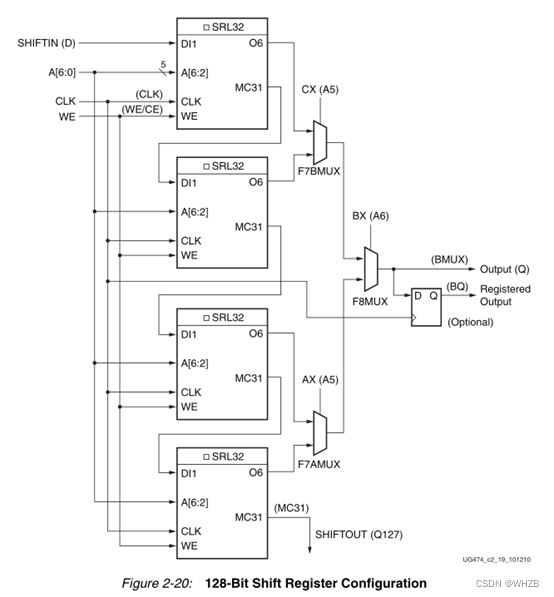

Slice M可以配置成32bit 移位寄存器,且使用slice中的触发器。

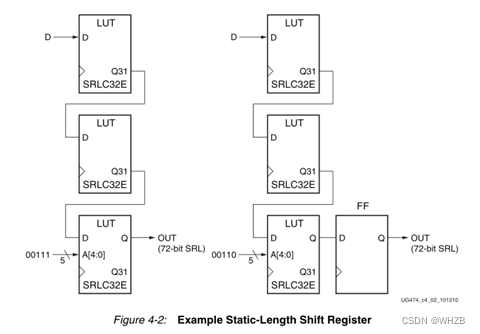

每个LUT可以将串行数据延迟1-32个clk。Slice中4个LUT级联可以产生128个clk延迟,亦可以跨多个slice合并移位寄存器。Slice之间没有直接连接以形成更长的移位寄存器。

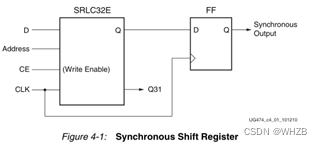

移位操作需要一个时钟边缘;LUT Q输出的动态长度读取操作是异步的;LUT Q输出的静态长度读取操作是同步的;

应用:

-

延迟或延迟补偿 ;

-

同步FIFO和 内容存储器(content addressable memory,CAM)

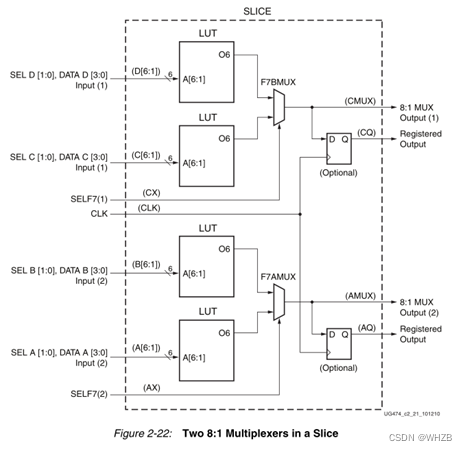

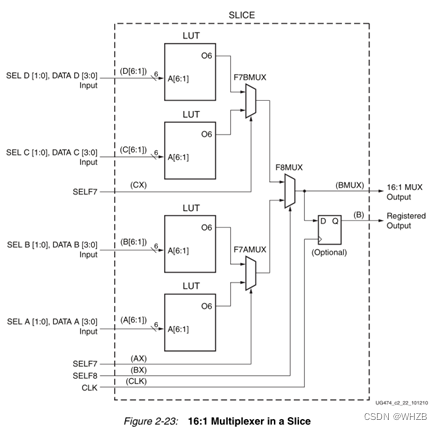

Multiplexers

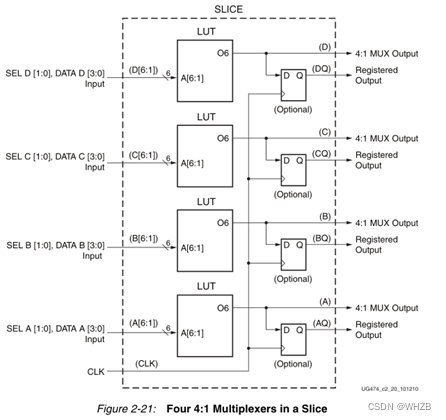

可以在多个slice上创建宽度大于16:1的多路复用器。然而,slice之间没有直接连接来形成这些宽复用器。

4:1多路复用器,使用1个LUT

8:1多路复用器,使用2个LUT

16:1多路复用器,使用4个LUT

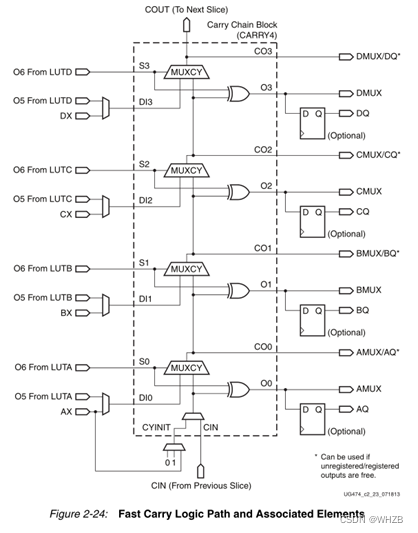

Carry Logic

用于在slice中执行快速算术加减运算。7系列FPGA CLB有两个单独的进位链。

进位链向上运行,每个slice的高度为四位。对于每个位,都有一个进位多路复用器(MUXCY)和一个专用的异或门,用于将操作数与所选进位相加/相减。专用进位路径和进位多路复用器(MUXCY)也可用于级联函数生成器。

CH3.Primitives

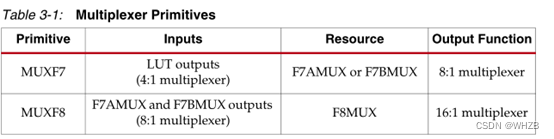

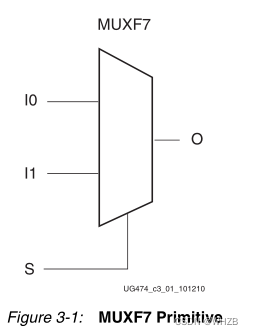

Multiplexer Primitives

多路复用器原语提供每个slice中专用多路复用器的直接实例化,允许构建更广泛的多路复用器。表3-1描述了这两个原语。两个复用器原语的端口信号相同。

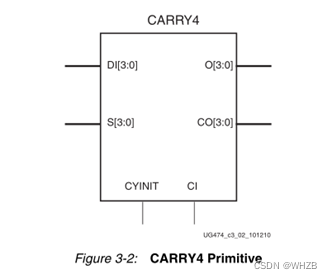

Carry Chain Primitive

可以实现两个4bit数的加减法运算。

Sum Outputs - O[3:0] 求和或减法输出

Carry Outputs - CO[3:0] 每一位的进位输出

Carry In – CI 进位输入

Data Inputs - DI[3:0] 数据输入

Select Inputs - S[3:0] 数据异或输入

Carry Initialize – CYINIT 进位初始化输入用于选择进位链中的第一位。该引脚的值为0(用于加法)、1(用于减法)或AX输入(用于动态第一进位)。

SLICEM Distributed RAM Primitives

Clock – WCLK:用于同步写入的时钟

Enable – WE/WED:写入使能

Address – A[#:0], DPRA[#:0], and ADDRA[#:0] – ADDRD[#:0]:地址

Data In – D, DID[#:0]:写入数据

Data Out – O, SPO, DPO and DOA[#:0] – DOD[#:0]:数据输出

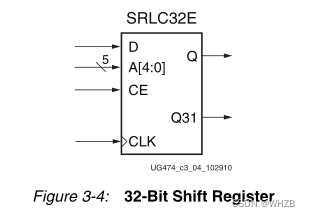

SLICEM SRL Shift Register Primitive

Clock – CLK时钟

Data In – D数据输入

Clock Enable – CE时钟使能

Address – A[4:0]地址

Data In – Q数据输出,由A选择移位的输出

Data Out – Q31 移位32输出

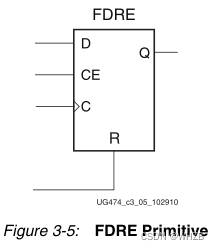

Flip-Flop Primitives

- Data In – D:输入数据.

- Data Out – Q:移位寄存数据输出

- Clock - C:时钟 Clock Enable - CE:时钟使能

- Synchronous Reset -R:当R为高时,所有其他输入被覆盖,数据输出(Q)在活动时钟转换时被驱动为低。

- Synchronous Set – S :当S为高时,所有其他输入被覆盖,并且数据输出(Q)在活动时钟转换上被驱动为高。

- Asynchronous Clear -CLR:当CLR为高时,所有其他输入被覆盖,数据输出(Q)被驱动为低。

- Asynchronous Preset -PRE:当PRE为高时,所有其他输入被覆盖,数据输出(Q)被驱动为高。

CH4 Applications

Synchronous Shift Registers

Static-Length Shift Registers

图4-2显示了一个72位移位寄存器。只有最后一个SRLC32E原语需要将其地址输入绑定到5b’00111。或者,移位寄存器长度可以限制为71位(地址绑定到5b’00110),触发器可以用作最后一个寄存器。(在SRLC32E原语中,移位寄存器长度为地址输入+1)。

使用STARTUPE2原语定义并连接GSR和GTS信号源。此原语允许用户定义这些专用网络的源。GSR和GTS在配置过程中始终处于激活状态,通过STARTUPE2原语将信号连接到GSR和GTS,定义了配置后如何控制GSR和GTS。默认情况下,在启动阶段的选定时钟周期上进行配置后,它们将被禁用,从而启用设备中的触发器和I/O。

参考资料:

xilinx官方文档: UG474 -7 Series FPGAs Configurable Logic Block User Guide

https://blog.csdn.net/wuzhikaidetb/article/details/124642077

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?