嵌入式——MCS-51单片机的硬件结构

1. 硬件结构整体概述

1.1 简图概述

单片机主要由:CPU,存储器,IO接口三者构成

1.2 个人的总结看法

| 单片机结构 | 人体结构 | 详情 |

|---|---|---|

| CPU | 大脑负责思考的部分 | 包括运算器和控制器 |

| 存储器 | 大脑负责记忆的部分 | 包括数据存储器和程序存储器 |

| 时钟与震荡器 | 相当于心脏 | 频率与性能相关 |

| IO接口 | 类似神经反射中的感受器和效应器 | 包括串行和并行接口 |

| 总线 | 人体的神经和血管 | 包括数据总线,地址总线,控制总线 |

1.3 详细结构框图

下面根据这个框图对每个部分的结构进行讲解

2. 中央处理器CPU

CPU内部的结构可以大致分成3个部分:运算器,控制器,和一些通用寄存器

2.1 运算器——进行运算

| 组成部件 | 描述 |

|---|---|

| 算术逻辑单元ALU | 进行算术运算,逻辑运算 |

| 累加器ACC(8位) | 需要ALU处理的数据和运算结果多经过A |

| 寄存器B(8位) | 与A配合执行乘除运算,也可以作为通用寄存器 |

| 程序状态字PSW(8位) | 存放ALU运算过程的标志转台CY,AC,F0,RS1,RS0,OV,F1,P |

2.2 通用寄存器——暂时存放数据(这应该属于存储器部分)

工作寄存器R0-R7(8位)

暂时存储运算数据和中间结果,有四个工作寄存器区,通过PSW.4(RS0)和PSW.3(RS1)来切换,选用

2.3 控制器——对指令进行处理

| 组成部分 | 描述 |

|---|---|

| 时钟电路 | 分内部时钟电路和外部震荡源 |

| 复位电路 | 使电路恢复称起始状态 |

| 指令寄存器 | 存放指令代码 |

| 指令译码器 | 对指令进行译码,译码之后有定时和控制电路发出相应的控制信号 |

| 程序计数器PC(16位) | PC用来存放CPU下一条要执行的指令地址,PC内容送到地址总线,CPU读取指令,PC自动加1,复位时PC=0000H |

| 堆栈指针SP(8位) | MCS-51的堆栈设在片内RAM,用于子程序调用及返回和中断处理断点的保护和返回。 数据入栈出栈时,SP自动加减1,其内容始终为栈顶地址,复位时SP=07H |

| 数据指针DPTR(16位) | 存放片外存储器地址,作为片外存储器的指针,可以分为两个八位寄存器DPH,DPL使用 |

3. 存储器的结构

总体框架

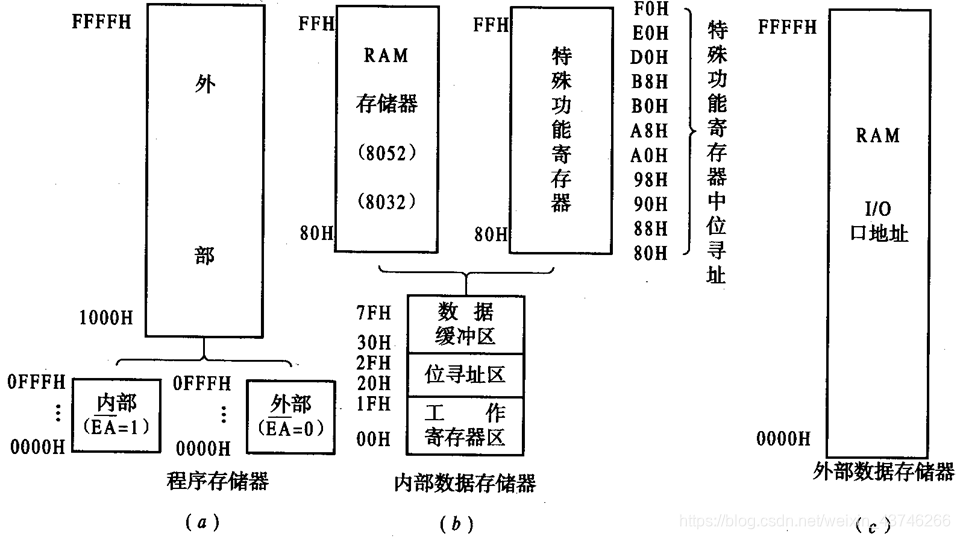

单片机的存储器可以分为三个部分:程序存储器(64KB),内部数据存储器(256B),外部数据存储器(64KB)

(存储器及其大小的理解,以程序存储器为例子,程序存储器就相当于一栋大楼,这栋大楼一共有64K(

2

16

2^{16}

216)个房间,每个房间可以存放一个字节(8个2进制数)的数据,相当于有8个床位(有人是1,没人是0)

3.1 程序存储器

对于8051来说, 程序存储器(ROM)的内部地址为 0000H~0FFFH, 共 4 KB; 外部地址为 1000H ~ FFFFH, 共 60 KB。 当程序计数器由内部 0FFFH执行到外部 1000H 时, 会自动跳转。

按字节存放,64K的地址,存储空间是64KB

也有一些没有内部程序存储器,如8031.

补充说明:ROM(read only menmory),这种存储单元不会因为掉电而消失,ROM有MASKROM.PROM,EPROM,EEPROM,FLASH,当需要需要频繁的重写,就要采用EEPROM,或是FLASH,因为FLASH擦写速度快,所以一般采用FLASH。

3.2 内部数据存储器

从00H到0FFH一共256个字节,低128个字节(00H-7FH)为整整的RAM区,高128字节(80H-FFH)为特殊功能寄存器SFR

RAM区(低128字节)

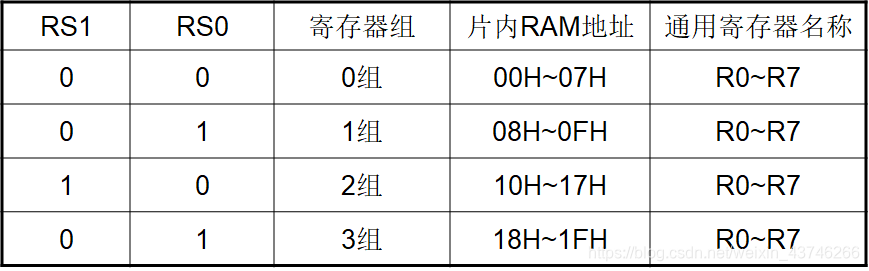

3.2.1 (00H-1FH)通用工作寄存器

在低128个字节RAM中,00H-1FH共32个单元是4个通用工作寄存器区。每一个区有8个通用寄存器R0-R7,地址对应关系如下

3.2.2 (20H-2FH)位寻址区

可以当成一般的开放区使用,也可以通过地址映射表进行位操作

3.2.3 (30H-7FH)开放区

这部分区域“痛快的”开放给用户使用,用户直接对该区域进行写入与读取。

特殊功能寄存器SFR

各个特殊功能寄存器在内存(80H-0FFH)的分布如下,但是要注意,这部分寄存器是分散地分布,但是没有被占用的地址一般不会用作一般开放区,因为这些地址有可能不存在。

PSW程序状态字的说明

| 位符号 | 名称 | 功能 |

|---|---|---|

| CY | 进位标志位 | 最高位向前进位借位时,CY为1 |

| AC | 辅助进位标志位 | 用于十进制调整,低四位向高四位进位借位时,AC为1 |

| F0 | 用户标志位 | 可以用指令置位,复位 |

| RS1、RS0 | 寄存器组选择位 | 选择寄存器组 |

| OV | 溢出标志位 | 带符号加减运算,结果溢出,OV为1,乘积超过255,OV为1,出发无意义,OV为1 |

| / | 无定义 | |

| P | 奇偶标志位 | 累加器A中为奇数,P为1 |

3.3 外部数据存储器

外部数据存储器一般由静态RAM构成,其容量大小由用户根据需要而定, 最大可扩展到 64 KB RAM , 地址是 0000H~0FFFFH。

CPU通过MOVX指令访问外部数据存储器, 用间接寻址方式, R0、R1和 DPTR都可作间接寄存器。

注意, 外部RAM和扩展的I/O接口是统一编址的, 所有的外扩I/O 口都要占用 64 KB中的地址单元。

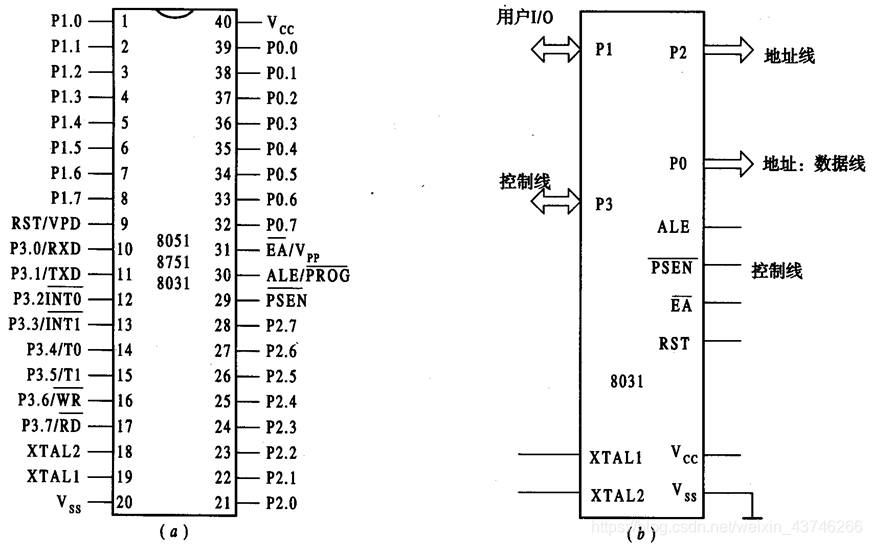

4. 并行IO接口

·MCS-51单片机有4个双向8位并行的IO口;P0-P3

·每一个口都是一个8位的锁存器

·复位后状态都是1

4.1 P0是三态双向口

三态指0,1,高阻态

既可以作为并行IO口,也可以作为数据总线口

当外部拓展了存储器或是IO端口,则只能作数据总线和地址总线低8位

4.2 P1 P2 P3是准双向口

- P1口是专供用户使用的IO口

- P2可以做并行IO口,当有外部拓展时,充当地址总线感8位

- P3还是双功能口,每个口都有第二功能

5.单片机的引脚与功能

5.1 总览

| 引脚 | 功能 |

|---|---|

| 端口线(4*8) | 前面的IO端口介绍 |

| 电源线 | VCC电源线,VSS接地线 |

| 控制线(6条) | 进行一些控制 |

5.2 控制线

| 符号 | 名称 |

|---|---|

| A L E / P R O G ‾ ALE/\overline{PROG} ALE/PROG | 地址锁存允许/编程线 |

| E A ‾ / V P P \overline{EA}/VPP EA/VPP | 允许访问片外存储器/变成电源线 |

| P S E N ‾ \overline{PSEN} PSEN | 片外ROM选通线 |

| R S T / V P D RST/VPD RST/VPD | 复位/备用电源线 |

| X T A L 1 / X T A L 2 XTAL1/XTAL2 XTAL1/XTAL2 | 片内震荡电路输入输出线 |

6. 单片机的基本时序

6.1 机器周期和指令周期

- 振荡周期,也称时钟周期,是指为单排年级提供时钟振荡信号的振荡源的周期

- 状态周期:每个状态周期是时钟周期的两倍,每个状态周期由两个节拍P1,P2组成

- 机器周期:一个机器周期包含6个状态周期,也就是12个时钟周期,在一个机器周期内,单片机可以完成一个独立的操作

- 指令周期:CPU执行一条指令所需要的时间叫做一个指令周期,由一个或是几个机器周期组成

因为重点关注硬件结构,时序暂时不作深入了解

2211

2211

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?