数电3_2——CMOS门电路

1. 概述

- CMOS逻辑门电路是在TTL器件之后,出现的应用比较广泛的数字逻辑器件,在功耗、抗干扰、带负载能力上优于TTl逻辑门,所以超大规模器件几乎都采用CMOS门电路,如存储器ROM、可编程逻辑器件PLD等

- 国产的CMOS器件有CC4000(国际CD4000/MC4000)、高速54HC/74HC系列(国际MC54HC/74HC),此外还有兼容型的74HCT和74BCT系列(BiCMOS)

2. MOS管的开关特性

有关MOS管与三级管,请参看我的另外一篇博客

- 增强型NMOS管:

- 当 v G S < V G S ( T H ) v_{GS}<V_{GS}(TH) vGS<VGS(TH),管子截止, i D = 0 i_{D}=0 iD=0, R O F F > 1 0 9 Ω R_{OFF}>10^{9}Ω ROFF>109Ω

- 当 v G S > V G S ( T H ) v_{GS}>V_{GS}(TH) vGS>VGS(TH),管子导通, i D ∝ V G S 2 i_{D}\propto V^{2}_{GS} iD∝VGS2, R O N < 1 0 3 Ω R_{ON}<10^{3}Ω RON<103Ω

- 增强型PMOS:

- 当 v G S > V G S ( T H ) v_{GS}>V_{GS}(TH) vGS>VGS(TH),管子截止, i D = 0 i_{D}=0 iD=0

- 当 v G S < V G S ( T H ) v_{GS}<V_{GS}(TH) vGS<VGS(TH),管子导通, i D ∝ V G S 2 i_{D}\propto V^{2}_{GS} iD∝VGS2

- 耗尽型NMOS

- 当 v G S < V G S ( O F F ) ( V G S ( O F F ) < 0 ) v_{GS}<V_{GS}(OFF)(V_{GS}(OFF)<0) vGS<VGS(OFF)(VGS(OFF)<0),管子截止, i D = 0 i_{D}=0 iD=0

- 当

v

G

S

>

V

G

S

(

O

F

F

)

v_{GS}>V_{GS}(OFF)

vGS>VGS(OFF),管子导通

备注:因为h耗尽型 v G S = 0 v_{GS}=0 vGS=0时电流 i D ≠ 0 i_{D} \neq 0 iD=0,

- 耗尽型PMOS

- 当 v G S > V G S ( O F F ) ( V G S ( O F F ) > 0 ) v_{GS}>V_{GS}(OFF)(V_{GS}(OFF)>0) vGS>VGS(OFF)(VGS(OFF)>0),管子截止, i D = 0 i_{D}=0 iD=0

- 当 v G S < V G S ( O F F ) v_{GS}<V_{GS}(OFF) vGS<VGS(OFF),管子导通

3. COMS反相器

COMS反相器单路结构是CMOS电路的基本结构形式,是构成复杂CMOS逻辑电路的基本模块智一。

3.1 电路结构

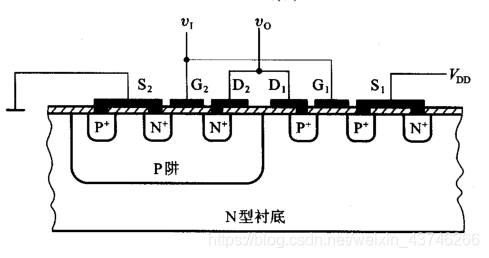

如下图所示:T1为增强型PMOS管,T2为增强型NMO管,它们构成互补对称电路

3.2 工作原理

- 它们的开启电压分别为

V

G

S

(

t

h

)

P

、

V

G

S

(

t

h

)

N

V_{GS(th)P} 、V_{GS(th)N}

VGS(th)P、VGS(th)N ,

且 ∣ V G S ( t h ) P ∣ = V G S ( t h ) N |V_{GS(th)P} |=V_{GS(th)N} ∣VGS(th)P∣=VGS(th)N ,并设 V D D > ∣ V G S ( t h ) P ∣ + V G S ( t h ) N V_{DD} >|V_{GS(th)P} |+V_{GS(th)N} VDD>∣VGS(th)P∣+VGS(th)N, V I L = 0 , V I H = V D D V_{IL} =0,V_{IH} =V_{DD} VIL=0,VIH=VDD - 当

v

I

=

V

I

L

=

0

v_{I} =V_{IL} =0

vI=VIL=0为低电平时,

T1管导通( ∣ V G S P ∣ > ∣ V G S ( t h ) P ∣ |V_{GS_{P}}|>|V_{GS(th)P} | ∣VGSP∣>∣VGS(th)P∣,

T2管截止( V G S N < V G S ( t h ) N V_{GS_{N}}<V_{GS(th)N} VGSN<VGS(th)N),

此时输出高电平 V O H = R o f f R o f f + R o n ∗ V D D ≈ V D D , ( R o f f ≫ R o n ) V_{OH}=\frac{R_{off}}{R_{off}+R_{on}}*V_{DD}\approx V_{DD} , (R_{off}\gg R_{on}) VOH=Roff+RonRoff∗VDD≈VDD,(Roff≫Ron)

[明确导通截止后,按两个电阻串联来看] - 当

v

I

=

V

I

H

=

V

D

D

v_{I} =V_{IH} =V_{DD}

vI=VIH=VDD为高电平时,

T1管截止( ∣ V G S P ∣ < ∣ V G S ( t h ) P ∣ |V_{GS_{P}}|<|V_{GS(th)P} | ∣VGSP∣<∣VGS(th)P∣,

T2管导通( V G S N > V G S ( t h ) N V_{GS_{N}}>V_{GS(th)N} VGSN>VGS(th)N),

此时输出低电平 V O L = R o n R o f f + R o n ∗ V D D ≈ 0 , ( R o f f ≫ R o n ) V_{OL}=\frac{R_{on}}{R_{off}+R_{on}}*V_{DD}\approx 0 , (R_{off}\gg R_{on}) VOL=Roff+RonRon∗VDD≈0,(Roff≫Ron)

备注:(IL :input_low,IH: input_high,OL:output_low…)

3.3 特点

- 无论 v I v_{I} vI是高电平还是低电平,T1和T2管总处于是一个导通一个截止的工作状态,称为互补,这种电路结构CMOS电路(Complementary Metal Oxide Semiconductor)

- 由于静态下无论输入 v I v_{I} vI为低电平还是高电平, T1 和T2 总是有一个截止的,其截止电阻很高,故流过T1 和T2 的静态电流很小,故其静态功耗很小。这是CMOS电路的一大突出优点。

3.4 电压电流特性

3.4.1 电压传输特性

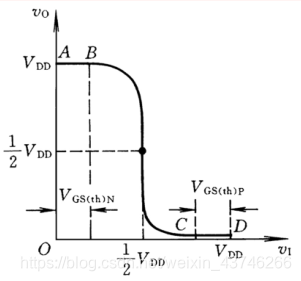

- AB段与CD段如上面所讲,电压的输入与输出相反

- BC段,

v

i

>

V

G

S

(

T

H

)

N

,

∣

V

D

D

−

v

i

∣

>

∣

V

G

S

(

T

H

)

P

∣

v_{i}>V_{GS(TH)N},|V_{DD}-v_{i}|>|V_{GS(TH)P}|

vi>VGS(TH)N,∣VDD−vi∣>∣VGS(TH)P∣,

整理, V G S ( T H ) N < v i < V D D − ∣ V G S ( T H ) P ∣ V_{GS(TH)N}<v_{i}<V_{DD}-|V_{GS(TH)P}| VGS(TH)N<vi<VDD−∣VGS(TH)P∣,

T1 ,T2 同时导通,如果 v i = 1 2 V D D , v o = 1 2 V D D v_{i}=\frac{1}{2}V_{DD},v_{o}=\frac{1}{2}V_{DD} vi=21VDD,vo=21VDD

3.4.2 电流传输特性

- AB,CD段的露出电流都非常小,毕竟原来的电流就很小

- BC:因为T1与T2都导通了,电阻相对较小,特别是

v

i

=

1

2

V

D

D

,

v

o

=

1

2

V

D

D

v_{i}=\frac{1}{2}V_{DD},v_{o}=\frac{1}{2}V_{DD}

vi=21VDD,vo=21VDD时,漏出电流最大。

使用时,输入电压不应长时间工作在这段,以防止由于功耗过大而电路损坏。

3.5 输入噪声容限

从CMOS反相器的电压传输特性克制,在输入电压 v i v_{i} vi偏离正常的高低电平时,输出电压并不会马上改变,允许输入电压有一定的变化范围

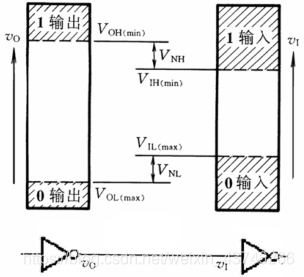

- 输入端噪声容限:是指在保证输出高、低电平基本不变(不超过规定范围)时,允许输入信号高、低电平的波动范围

- 计算方法: 输入噪声容限分为输入高电平噪声容限

V

N

H

V_{NH}

VNH 和输入低电平噪声容限

V

N

L

V_{NL}

VNL 。下图给出计算输入噪声容限的方法:

V N H = V O H ( m i n ) − V I H ( m i n ) V_{NH}=V_{OH(min)}-V_{IH(min)} VNH=VOH(min)−VIH(min)

V N L = V O L ( m a x ) − V I L ( m a x ) V_{NL}=V_{OL(max)}-V_{IL(max)} VNL=VOL(max)−VIL(max)

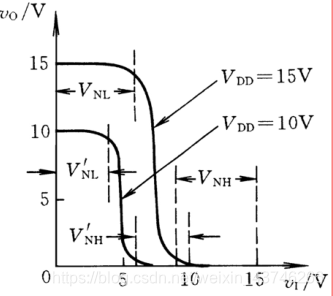

- 输入噪声容限与电源电压

V

D

D

V_{DD}

VDD有关,当

V

D

D

V_{DD}

VDD增加时,电压传输特性右移——可以通过提高

V

D

D

V_{DD}

VDD提高噪声容限

3.6 CMOS反相器的静态特性

3.6.1 输入特性

- 输入特性:从CMOS反相器输入端看其输入电压与电流的关系

- 由于MOS管的栅极和衬底之间存在SiO 2 为介质的输入电容,而绝缘介质又很薄,非常容易被击穿,所以对CMOS电路,必须采取保护措施

- CMOS反相器的常用两种保护电路:

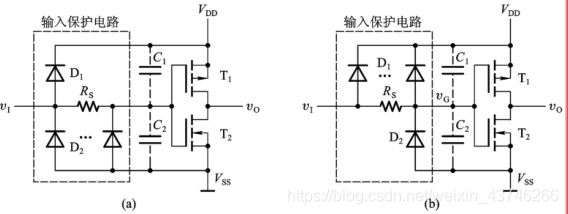

- CMOS反相器保护电路:图(a)为74HC系列的输入保护电路。图(b)是4000系列的输入保护电路[

其实我也不知道这两个系列是什么]

以图(a)为例子,

D 1 D_{1} D1 和 D 2 D_{2} D2都是双极型二极管 ,正向导通压降为 V D F = 0.5 V ~ 0.7 V V_{DF} =0.5V~0.7V VDF=0.5V~0.7V,反向击穿电压约为 30 V 30V 30V, D 2 D_{2} D2 为分布式二极管, 可以通过较大的电流, R S R_{S} RS 的值一般在 1.5 2.5 K Ω 1.5~2.5KΩ 1.5 2.5KΩ之间。 C 1 C_{1} C1 和 C 2 C_{2} C2 为 T 1 T_{1} T1 和 T 2 T_{2} T2 的栅极等效电容(等效电容是一种等效,不是真实存在)

a. 当 v i > V D D + V D F v_{i}>V_{DD}+V_{DF} vi>VDD+VDF时,二极管 D 1 D_{1} D1导通,将 v G v_{G} vG的电压钳制在 V D D + V D F V_{DD}+V_{DF} VDD+VDF,这样就能保证 C 2 C_{2} C2(下面的等效电容)的电压不超过 V D D + V D F V_{DD}+V_{DF} VDD+VDF

b. 当 v i < − V D F v_{i}<-V_{DF} vi<−VDF时,二极管 D 2 D_{2} D2导通, v G v_{G} vG的电压钳制在 − V D F -V_{DF} −VDF,将保证 C 1 C_{1} C1(上面的等效电容)上的电压不超过 V D D + V D F V_{DD}+V_{DF} VDD+VDF - 电流曲线

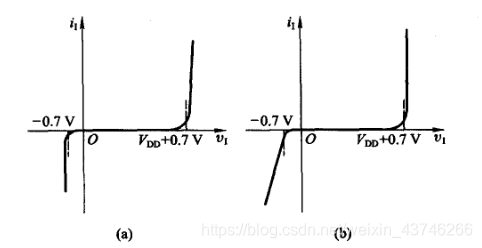

因为保护电路的存在,在 − V D F < v i < V D D + V D F -V_{DF}<v_{i}<V_{DD}+V_{DF} −VDF<vi<VDD+VDF时, I i ≈ 0 I_{i}\approx 0 Ii≈0,当 v i v_{i} vi$超过范围时(二极管导通),电流迅速增大,绝对值由电压和电路内阻决定

3.6.2 输出特性

输出特性为从反相器输出端看输出电压和输出电流的关系,包括输出为低电平输出特性和输出为高电平输出特性

低电平输出特性

- 在输入为高电平,即 v I = V I H = V D D v_{I} =V_{IH} =V_{DD} vI=VIH=VDD 时,此时 T 1 T_{1} T1 截止(看成一个定值电阻 R L R_{L} RL), T 2 T_{2} T2导通,此时输出为低电平。

- 如下图所示,电流从负载注入

T

2

T_{2}

T2 ,输出电压

V

O

L

V_{OL}

VOL 随电流增加而提高。[此时,

V

O

L

V_{OL}

VOL就是

v

D

S

2

v_{DS2}

vDS2,

I

O

L

I_{OL}

IOL就是

i

D

2

i_{D2}

iD2]。

所以输出特性曲线实际上就是T2的漏极特性曲线,从曲线上可以看到,由于T2的导通内阻与 v G S 2 v_{GS2} vGS2的大小有关, v G S 2 v_{GS2} vGS2越大,内阻越小,同样的 I O L I_{OL} IOL值下, V D D V_{DD} VDD越大, v G S 2 v_{GS2} vGS2越小, V O L V_{OL} VOL也越低

高电平输出特性

- 在输入为低电平,即 v I = V I L = 0 v_{I} =V_{IL} =0 vI=VIL=0 时,此时 T 2 T_{2} T2导通, T 2 T_{2} T2 截止(看成一个定值电阻 R L R_{L} RL),此时输出为高电平。

- 如下图所示,电流从T1管流出到负载【电流方向和图中所假设方向相反】,输出电压

V

O

H

=

V

D

D

−

I

O

H

R

O

N

1

V_{OH}=V_{DD}-I_{OH}R_{ON1}

VOH=VDD−IOHRON1(

R

O

N

1

R_{ON1}

RON1为T1的导通电阻)

- 随着负载电流的增加(注意,因为方向相反,所以为负值,实际上电流的绝对值减小),T1的导通压降加大, V O H V_{OH} VOH下降。

- 又因为MOS管的内阻与 v G S v_{GS} vGS有关,同样的 I O H I_{OH} IOH下, V D D V_{DD} VDD越高,则T1导通的 v G S v_{GS} vGS越负,导通内阻越小, V O H V_{OH} VOH也下降的越少(相对于 V D D V_{DD} VDD)。

3.7 CMOS反相器的动态特性

3.7.1 传输延迟时间

由于MOS管的寄生电容和负载电容的存在,使得输出电压的变化滞后输入电压的变化,将输出电压变化迟后输入电压变化的时间成为传输延迟时间

- t P H L t_{PHL} tPHL:输出由高电平跳变为低电平时的传输延迟时间

- t P L H t_{PLH} tPLH:输出由低电平跳变为高电平时的传输延迟时间

- t p d t_{pd} tpd:平均传输延迟时间, t p d t_{pd} tpd= ( t P H L + t P L H ) / 2 (t_{PHL}+t_{PLH})/2 (tPHL+tPLH)/2

COMS电路 t P H L = t P L H t_{PHL}=t_{PLH} tPHL=tPLH

3.7.2 交流噪声容限

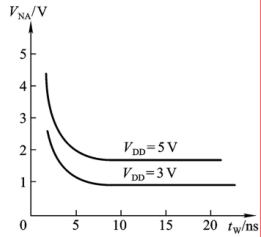

- 交流噪声容限是在窄脉冲作用下,输入电压允许变化的范围,下图是输入为不同宽度窄脉冲时CMOS反相器的交流噪声容限曲线。

即 V N A = f ( t w ) V_{NA} =f(t w ) VNA=f(tw),它反映CMOS反相器的动态抗干扰能力。其中 t w t_{w} tw 是脉冲宽度, t w t_{w} tw越大,容限越小

- 由于电路中存在着开关时间和分布电容的充放电过程,因而门电路输出状态的改变,直接与输入脉冲信号的幅度和宽度有关:

当输入脉冲信号的宽度接近于门电路传输延迟时间的情况下,则需要较大的输入脉冲幅度才能使电路的输出发生变化。也就是说门电路对窄脉冲的噪声容限要高于直流噪声容限[直流相当于 t w t_{w} tw无限大]

3.7.3 动态功耗

当CMOS反相器从一种稳定工作状态突然转变到另一种稳定状态过程,将产生附加的功耗,称为动态功耗。

它包括

- 对负载电容充放电的功耗

P

C

=

C

L

F

V

D

D

2

P_{C}=C_{L}FV_{DD}^{2}

PC=CLFVDD2

(其中 C L C _{L} CL是负载电容, f f f是输入信号的频率, V D D V_{DD} VDD 是漏极电源电压) - 在

V

G

S

(

t

h

)

N

<

V

I

<

V

D

D

−

∣

V

G

S

(

t

h

)

P

∣

V_{GS(th)N} < V_{I} <V_{DD} -|V_{GS(th)P} |

VGS(th)N<VI<VDD−∣VGS(th)P∣情况下两个管子同时导通时的功耗

P

T

=

V

D

D

I

T

A

V

=

C

P

D

F

V

D

D

2

P_{T}=V_{DD}I_{TAV}=C_{PD}FV_{DD}^{2}

PT=VDDITAV=CPDFVDD2

( C P D C_{PD} CPD是功耗电容,厂家给出 - 总功耗等于静态功耗和动态功耗之和,即

P

T

O

T

=

P

D

+

P

S

=

P

S

+

P

C

+

P

T

P_{TOT} =P_{D} +P_{S} =P_{S} +P_{C} +P_{T}

PTOT=PD+PS=PS+PC+PT 。

其中静态功耗P S 由于稳定时无论输入是高还是低电平,总有一个管子截止,故静态功耗很小,

故在计算总功耗时,一般只计算动态功耗

4. 其他逻辑功能的CMOS电路

CMOS反相器就相当于一个非门,输出与输入相反

4.1 CMOS与非门——上并下串

如图所示,

T

1

T_{1}

T1 、

T

3

T_{3}

T3 为两个并联的PMOS,

T

2

T_{2}

T2 、

T

4

T_{4}

T4 为两个串联的NMOS

- A , B A,B A,B有一个为“0”时, T 2 , T 4 T2,T4 T2,T4至少有一个截止, T 1 , T 3 T1,T3 T1,T3至少有一个导通,此时 Y = 1 Y=1 Y=1

- A , B A,B A,B同时为“1”时, T 2 , T 4 T2,T4 T2,T4同时导通, T 1 , T 3 T1,T3 T1,T3同时截至,此时 Y = 0 Y=0 Y=0

所以: Y = ( A B ) ′ Y = (AB)' Y=(AB)′

4.2 CMOS或非门——上串下并

如图所示,

T

1

、

T

3

T 1 、T 3

T1、T3 为两个串联的PMOS,

T

2

、

T

4

T 2 、T 4

T2、T4 为两个

并联的NMOS

- A 、 B A、B A、B有一个为“1”时, T 2 、 T 4 T 2 、T 4 T2、T4 至少有一个导通, T 1 、 T 3 T 1 、 T 3 T1、T3至少有一个截止,故输出为低电平, Y = 0 Y=0 Y=0

-

A

、

B

A、B

A、B同时为“0”时,

T

2

、

T

4

T 2 、 T 4

T2、T4同时截止,

T

1

、

T

3

T 1 、 T 3

T1、T3 同时导通,故输出为高电平,

Y

=

1

Y=1

Y=1

所以: Y = ( A + B ) ′ Y=(A+B)' Y=(A+B)′

4.3 带缓冲级的CMOS门电路

4.3.1 上述电路存在的问题

以与非门为例

- 输出电阻受输入状态的影响

- 输出的高低电平受输入端数目的影响:

输入端数目愈多,输出为低电平时串联的导通电阻越多,低电平 V O L V_{OL} VOL 越高;输出为高电平时,并联电阻也多,输出高电平 V O H V_{OH} VOH也提高 - 输入状态不同对电压传输特性有影响:

- 使 T 2 、 T 4 T 2 、T 4 T2、T4 达到开启电压时,输入电压 v I v_{I} vI不同

4.3.2 改进的电路

电路结构:反相器+或非门+反相器

带缓冲级的CMOS门电路其输出电阻、输出高低电平均不受输入端状态的影响,电压传输特性更陡

后记:精力有限,先整理到这里,硬件知识还需要再补充,基本的CMOS门电路能看懂了,缓冲之类的还需要再加把劲

1052

1052

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?