时序电路的传输延时

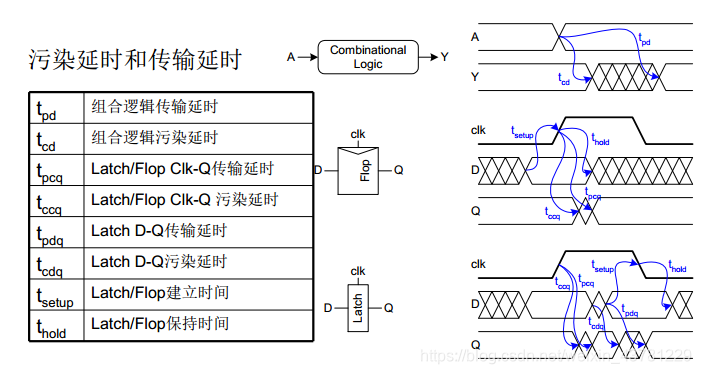

1. 下图是时序电路的一些基本延时参数

2. 触发器时序电路所要满足的条件

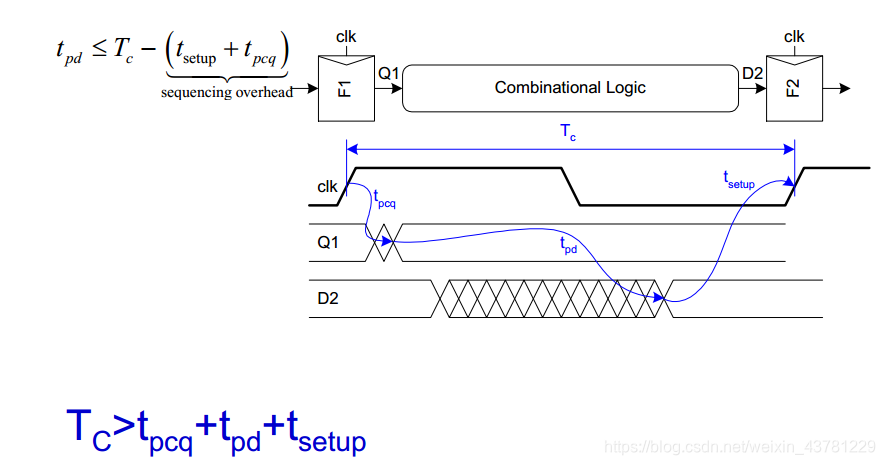

2.1 组合逻辑电路所要满足的最大延时

在理想情况下,整个时钟周期都可以用来在组合逻辑中进行计算,但是,触发器的时序开销将减少这一计算时间。如果组合逻辑的延时太大,那么接收元件因没有充分的建立时间而将采样错误的数值,这称为建立时间失效(setup time failure)或最大延时失效(max-delay failure)。它可以通过重新设计逻辑使逻辑速度加快或加长时钟周期来解决。下图显示了假设时钟为无偏斜的理想时钟时,在一条路径上从一个触发器至下一个触发器的最大延时时序约束。这条路径从触发F1的时钟上升沿开始。数据必须在下一个时钟上升沿之前传播到触发器F1的输出端Q1并通过组合逻辑到达D2,最后稳定在F2中。时钟所满足的条件如下图,最大逻辑延时tpd如下如:

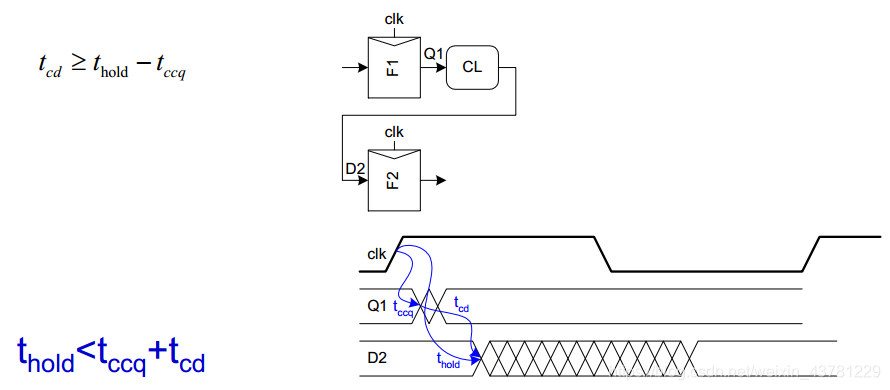

2.2 组合逻辑电路所要满足的最小延时

在理想情况下,时序元件可以前后直接连接,不需要在它们之间插入组合逻辑仍能正确工作。例如,一条流水线可以采用前后直接连接的寄存器按顺序逐级向前传送一条指令的操作码而不去修改它。但是如果寄存器的保持时间很大而污染延时很小,那么数据有可能错误的在同一时钟沿连续传播通过两个时序元件,从而破坏了系统应有的状态。这称为竞争条件(race condition)、保持时间失效(hold-time failure)或最小延时失效(min-delay failure)。它只能通过重新设计逻辑而不同通过减慢时钟来实现。因此,设计者在避免这类失效时应非常谨慎,因为修改设计和重新制造芯片的成本极高,且非常耗时。

下图显示了一个时钟无偏斜的理想时钟时,在一条路径上从一个触发器至下一个触发器的最小延时时序约束。这条路径从F1的时钟上升沿开始,在经过F1的clk-to-Q污染延时后,Q1的数据可以开始变化,再经过一段逻辑的污染延时后,数据到达D2处。但这个变化了的数据必须在该时钟沿的保持时间thold之后才能到达D2,以免它破坏F2的内容,因此我们可以求出最小的逻辑污染延时tcd如下所示:

如果通过触发器的污染延时很小,就必须在两个触发器之间插入缓冲器增加延时!

如果触发器的污染延时大于保持时间,就可以放心的背靠背使用触发器。

扫描链的使用就是个背靠背触发器的例子。

257

257

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?