PCIe总线介绍

2020年12月28日14:09:06

1. 辅助信号线

1.1 PERST#信号

-

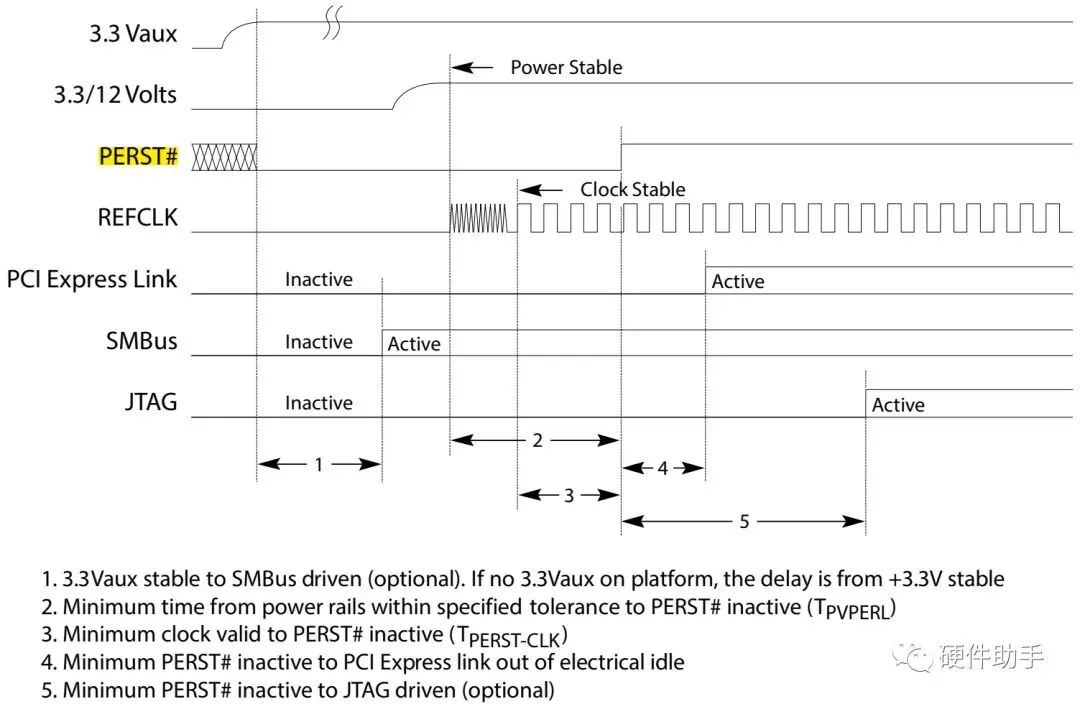

该信号为全局复位信号,由处理器系统提供,处理器系统需要为PCIe插槽和PCIe设备提供该复位信号;

-

PCIe设备使用该信号复位内部逻辑。当该信号有效时,PCIe设备将进行复位操作。PCIe总线定义了多种复位方式,其中Cold Reset和Warm Reset这两种复位方式的实现与该信号有关。

-

为了支持热插拔,在原理图设计时,在该引脚和GND之间接一个1000pF的电容,热插拔时能进行复位。

当一个PCIe设备的Vcc电源上电后,处理器系统将置该设备的PERST#信号为有效,此时将引发PCIe设备的复位方式,这种方式属于Fundamental Reset。PCIe设备进行Clod Reset时,所有使用Vcc进行供电的寄存器和PCIe端口逻辑将无条件进入初始状态。但是使用这种方式依然无法复位使用Vaux(备用电源)供电的寄存器和逻辑,这些寄存器和逻辑只能在处理器完全掉电时彻底复位。

1.2 REFCLK+和REFCLK-信号

在一个处理器系统中,可能含有许多PCIe设备,这些设备可以作为Add-In card与PCIe插槽连接,也可以作为内置模块,与处理器系统提供的PCIe链路直接相连,而不需要经过PCIe插槽。PCIe设备与PCIe插槽都具有REFCLK+和REFCLK-信号,其中PCIe插槽使用这组信号与处理器系统同步。

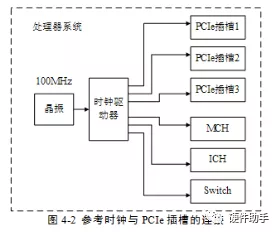

在一个处理器系统中,通常采用专用逻辑向PCIe插槽提供REFCLK+和REFCLK-信号。其中100MHz的时钟源由晶振提供,并经过一个“一推多”的差分时钟驱动器生成多个同相位的时钟源,与PCIe插槽一一对应连接。

PCIe的REFCLK+/-使用的是LPHCSL电平

PCIe插槽需要使用参考时钟,其频率范围为100MHz±300ppm,单端摆幅为0~0.7V。处理器系统需要为每一个PCIe插槽、MCH、ICH和Switch提供参考时钟。而且要求在一个处理器系统中,时钟驱动器产生的参考时钟信号到每一个PCIe插槽(MCH、ICH和Swith)的距离差在15英寸之内。通常信号的传播速度接近光速,约为6 in/ns,由此可见,不同PCIe插槽间REFCLK+和REFCLK-信号的传送延时差最大约为2.5ns

当PCIe设备作为Add-In卡连接在PCIe插槽时,可以直接使用PCIe插槽提供的REFCLK+和REFCLK-信号,也可以使用独立的参考时钟,只要这个参考时钟在100MHz±300ppm范围内即可。内置的PCIe设备与Add-In卡在处理REFCLK+和REFCLK-信号时使用的方法类似,但是PCIe设备可以使用独立的参考时钟,而不使用REFCLK+和REFCLK-信号。

在PCIe设备配置空间的Link Control Register中,含有一个“Common Clock Configuration”位。当该位为1时,表示该设备与PCIe链路的对端设备使用“同相位”的参考时钟;如果为0,表示该设备与PCIe链路的对端设备使用的参考时钟是异步的。

在PCIe设备中,“Common Clock Configuration”位的缺省值为0,此时PCIe设备使用的参考时钟与对端设备没有任何联系,PCIe链路两端设备使用的参考时钟可以异步设置。这个异步时钟设置方法对于使用PCIe链路进行远程连接时尤为重要

1.3 WAKE#信号

当PCIe设备进入休眠状态,主电源已经停止供电时,PCIe设备使用该信号向处理器系统提交唤醒请求,使处理器系统重新为该PCIe设备提供主电源Vcc。在PCIe总线中,WAKE#信号是可选的,因此使用WAKE#信号唤醒PCIe设备的机制也是可选的。值得注意的是产生该信号的硬件逻辑必须使用辅助电源Vaux供电

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

253

253

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?