前言

之前上课的时候留的一个作业,找一篇相关文章分析,先把文章大致分析发出来,下一节对文章内容进行仿真。

文章原文:M. Almada-Gutierrez, F. Sandoval-Ibarra and R. Sanchez-Fraga, "Integrated NMOS Differential Amplifier," 2022 IEEE Latin American Electron Devices Conference (LAEDC), Cancun, Mexico, 2022, pp. 1-4, doi: 10.1109/LAEDC54796.2022.9908177.

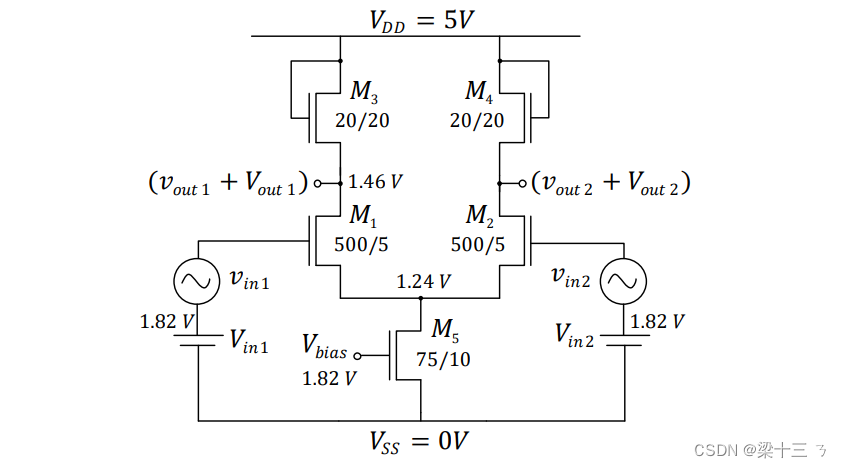

集成 NMOS 差分放大器

文章首先分析NMOS电路的工作原理及主要问题。电路采用NMOS技术,最小沟道长度5um。采用差分对作为输入级。

为了使差分对发挥适当的性能,每人晶体管的工作点必须保证它们都工作在饱和区,首先进行直流分析:为使M2管工作在饱和区,需使M2漏源电压大于栅源电压减去阈值电压:

另外,一旦电路偏置,输出节点的直流保持恒定

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3463

3463

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?