一、实验目的

1.学习设计二极管连接的MOS做负载的放大器,根据仿真现象使用理论对其分析。

2.学习设计全差动电流源作负载的差动放大器,根据仿真现象使用理论对其分析。

3.学习设计共源共栅全差动放大器,根据仿真现象使用理论对其分析。

4.学习运放参数测试的各种电路,了解其测试原理(CMRR,PSRR,GBW,噪声)。

5.熟悉IC514仿真环境,学会使用Calculator,Results Browser对参数进行运算和显示。

二、实验环境

集成电路设计实验室;Red Hat Enterprise linux5、Cadence IC Design Tools 5.10.41

三、实验原理

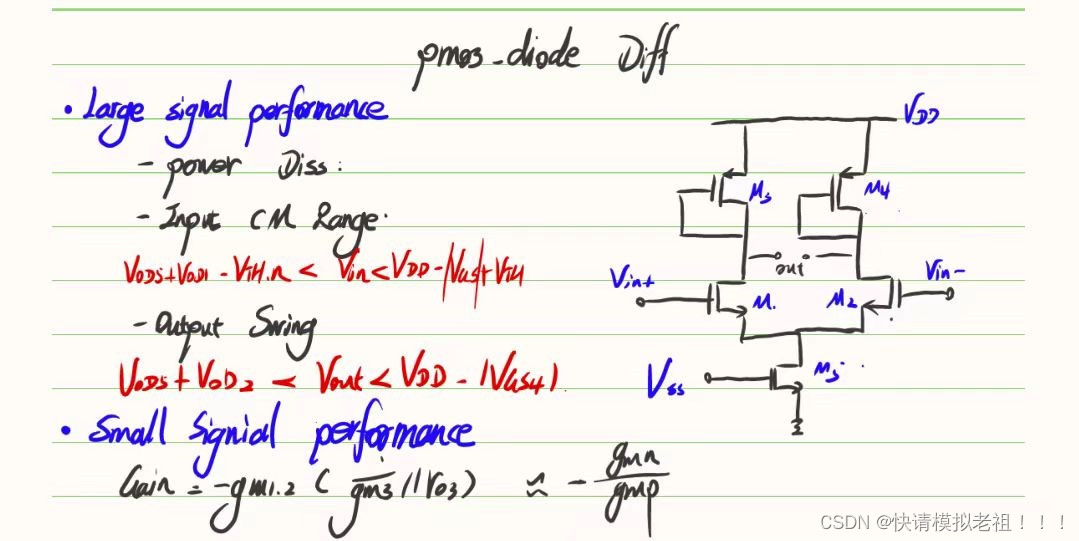

1. 二极管连接的MOS做负载的差动对电路详解

图1二极管连接的MOS做负载的差动对电路详解

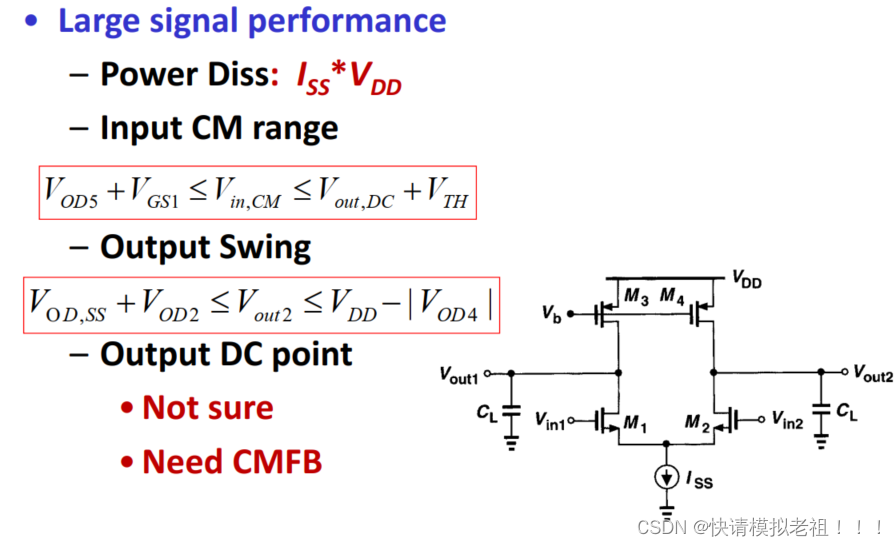

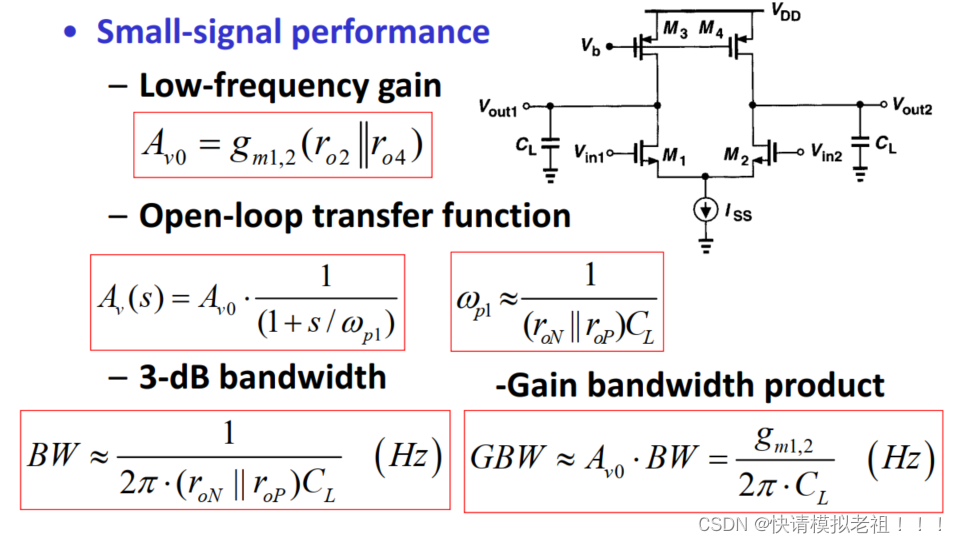

2. 全差动电流源作负载的差动对电路详解

图2全差动电流源作负载的差动对大信号分析

图3全差动电流源作负载的差动对小信号分析

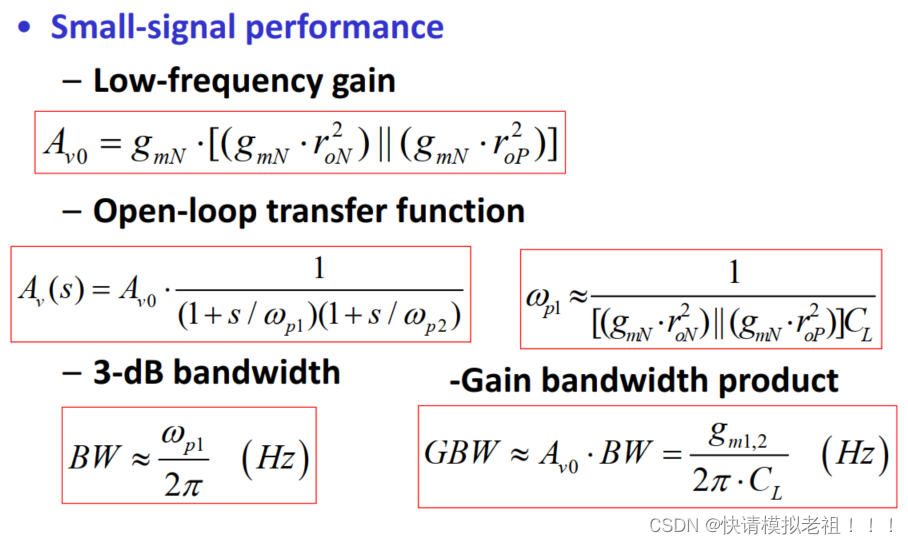

3. 共源共栅全差动放大器电路详解

图4共源共栅全差动放大器大信号分析

图5共源共栅全差动放大器小信号分析

四、实验步骤

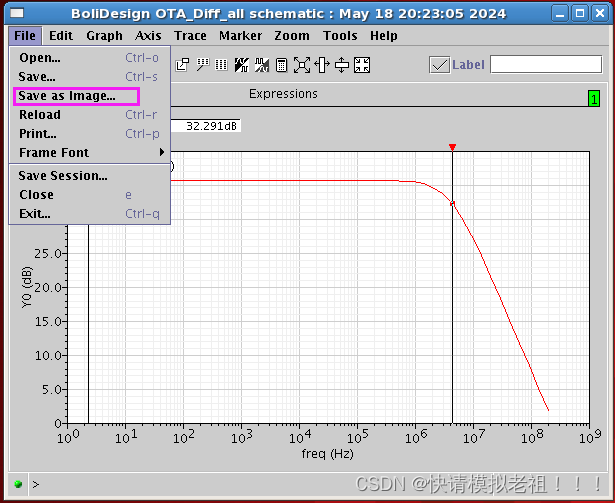

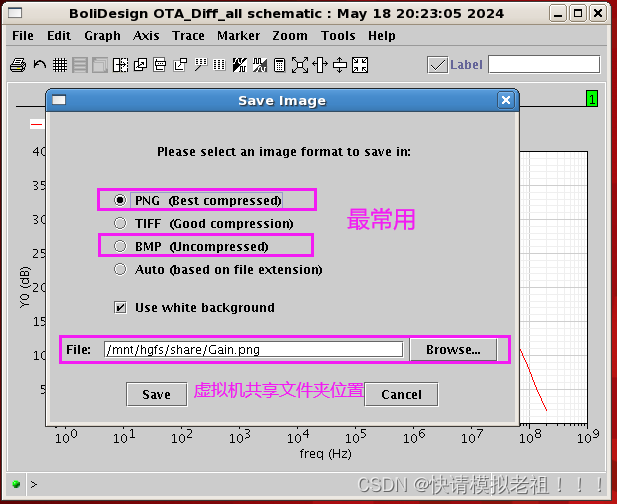

0. 仿真图形的导出

在科研工作中,正确无失真的得到实验结果是十分必要的,所以在实验的开始,展示如何保存Candece 中仿真得到的各种图标。

以全差动电流镜负载放大器的Gain幅频特性曲线做演示:

|

图6 对关键数据做标记 |

图7 导出图片 |

|

图8 选择导出类型 |

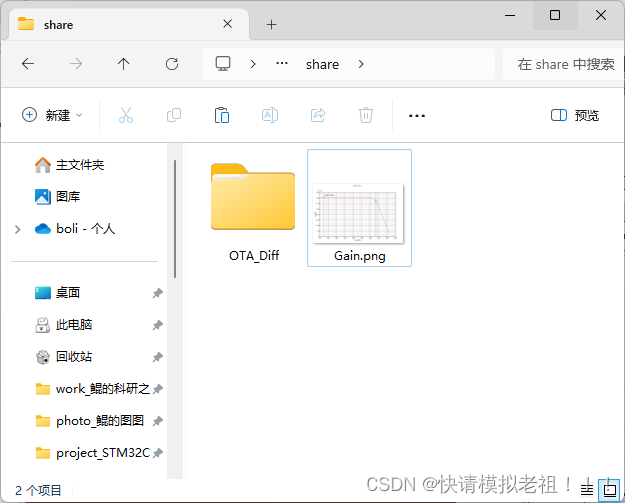

图9 在windows共享文件夹下查看 |

|

图10 最终仿真结果 | PNG格式:无损压缩,支持透明度,但文件较大。 TIFF格式:无损压缩,支持多通道,适用于印刷,不适合网络,文件大。 BMP格式:无损压缩,适用于Windows系统,文件大,不适用于网络。 |

【备注】:从此次试验后,我的报告严格按照此方法插入实验结果。

1.【实验一】二极管连接的MOS做负载的差动对电路

a.原理图搭建

|

图11 原理图搭建 |

图12 仿真环境配置 |

|

图13 查看每个管子的工作状态 |

图14 仿真结果如下 |

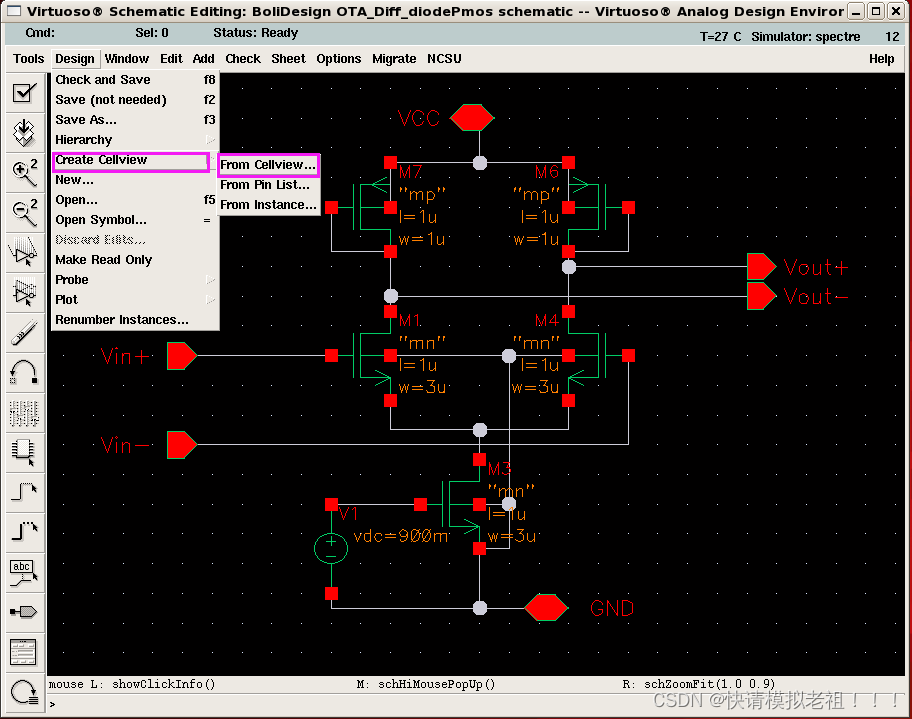

b.生成symbol

|

图15 给原理图添加端口 |

图16 打开symbol生成界面 |

|

图17 绘制symbol | |

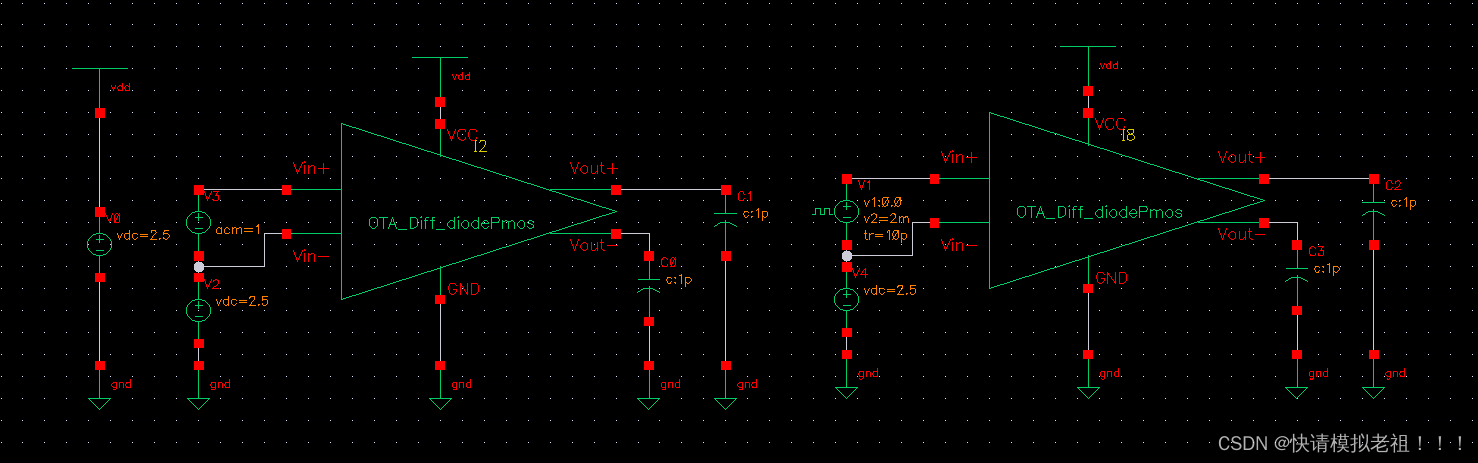

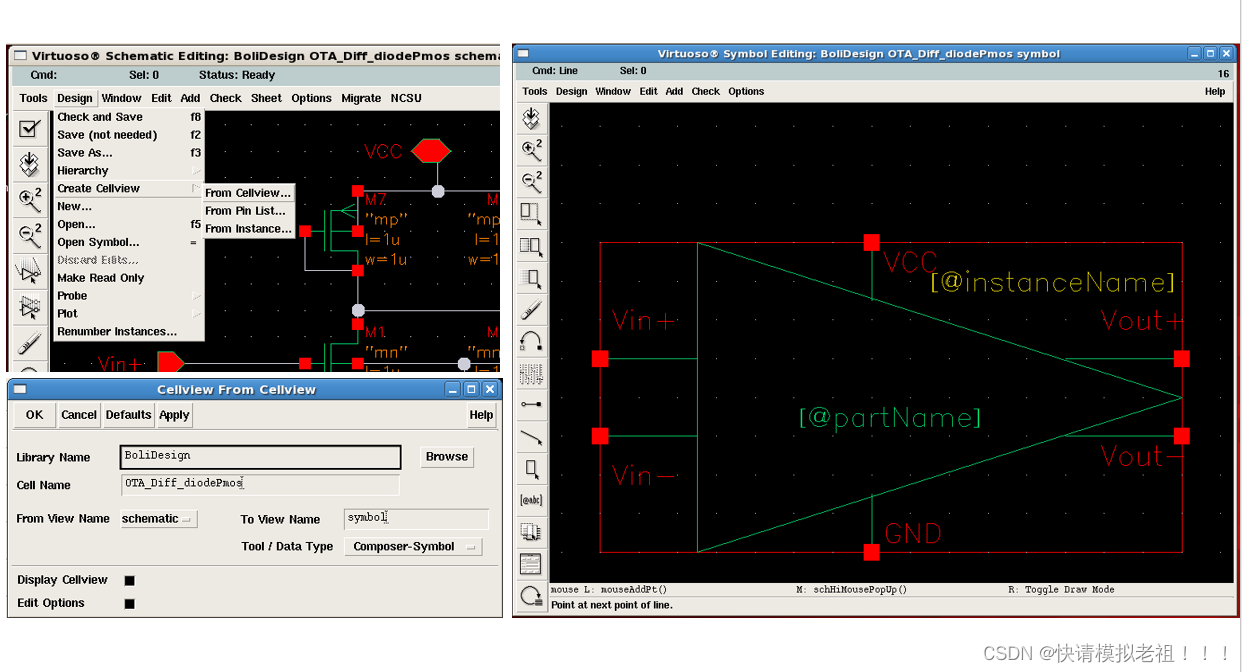

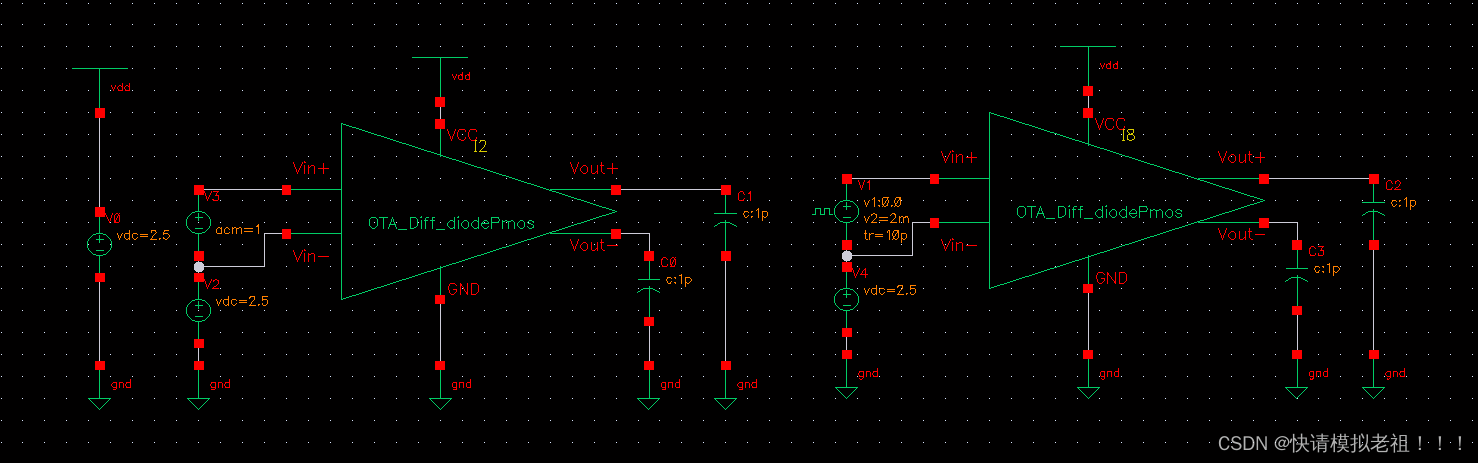

c.搭建仿真平台,仿真Gain,Bandwith,Set Time,CMRR,PSRR

|

图18 导入symbol |

图19 总仿真环境搭建与测量项一览 |

|

图20 总测试原理图一览 | |

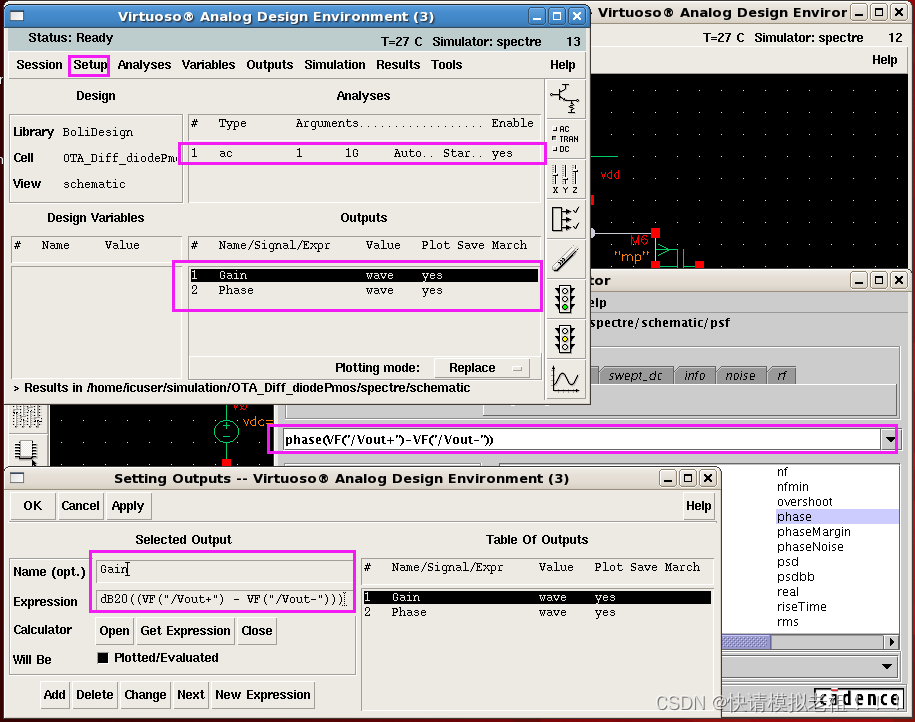

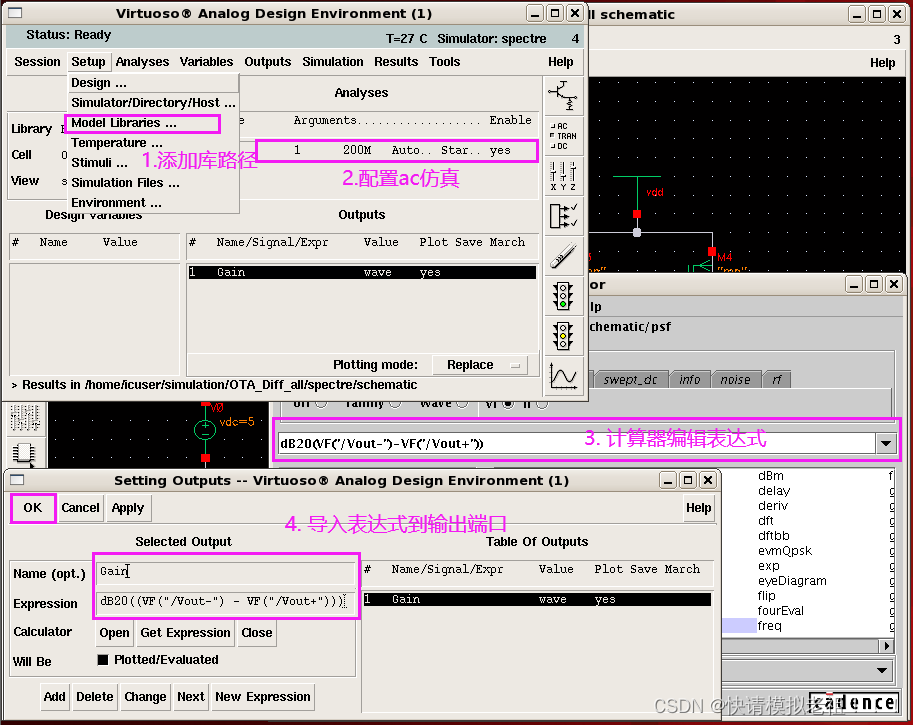

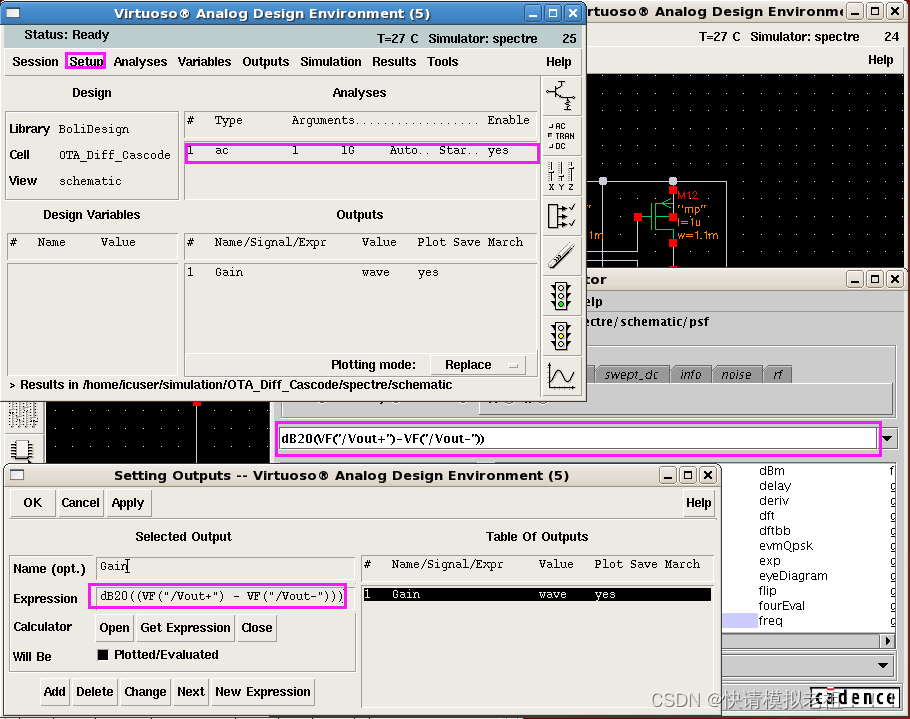

2.【实验二】全差动电流源作负载

a.原理图搭建

|

图21 如图搭建原理图 |

图22 仿真环境配置 |

|

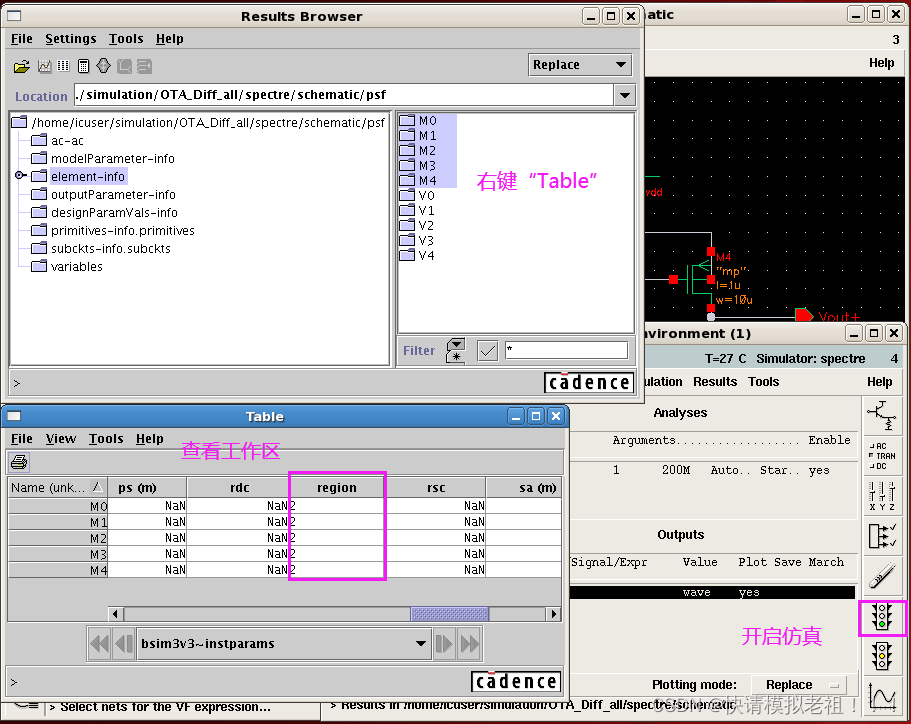

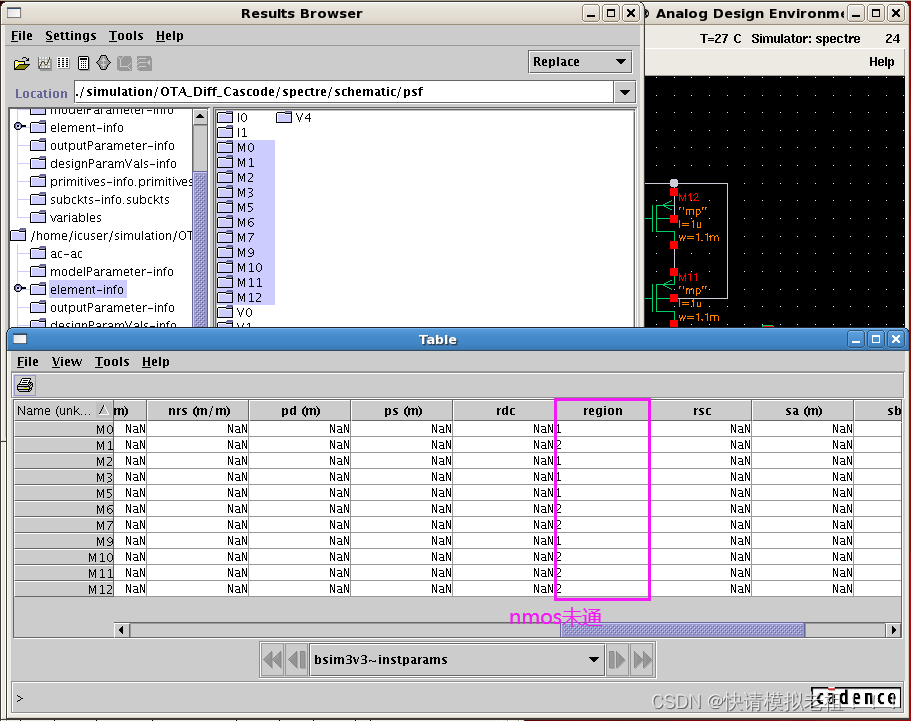

图23 查看放大器工作区无误 |

图24 仿真结果如下 |

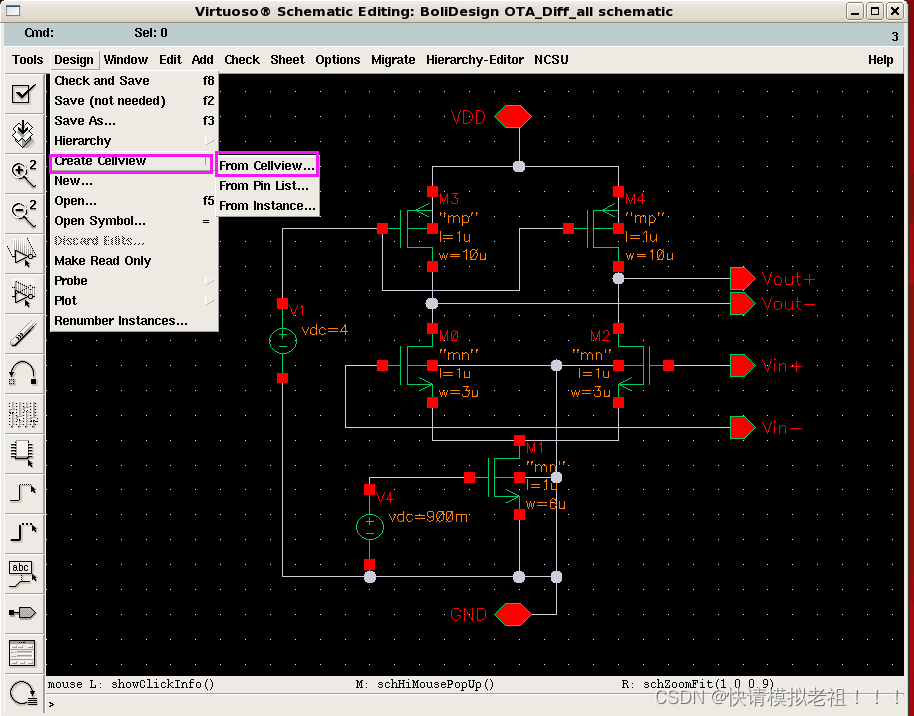

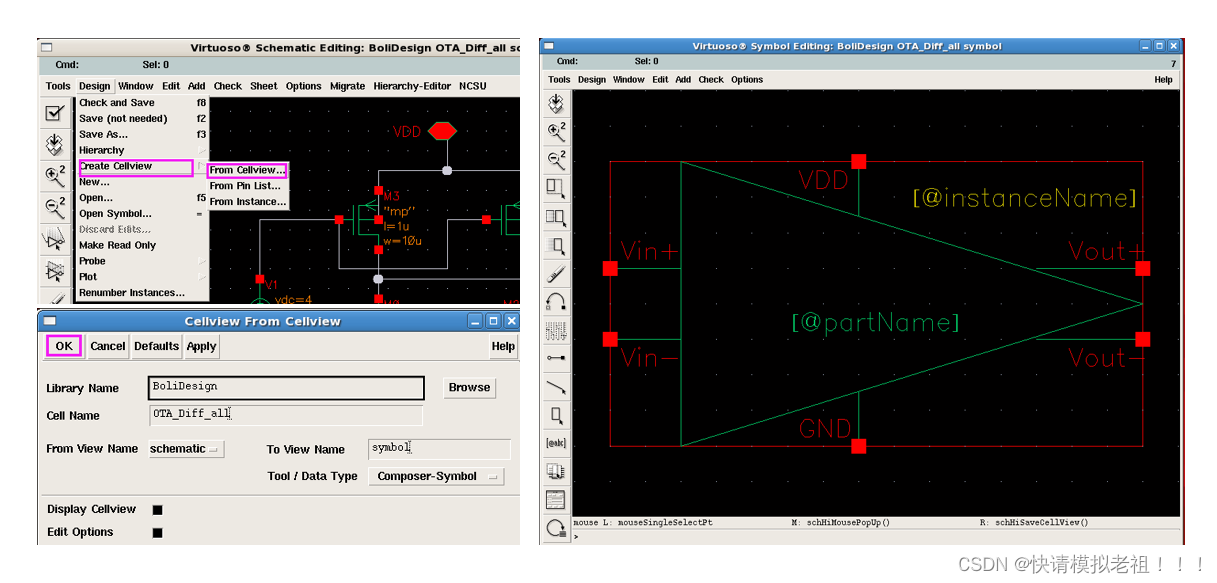

b.生成symbol

|

图25 给原理图添加端口 |

图26 打开symbol生成界面 |

|

图27 绘制symbol | |

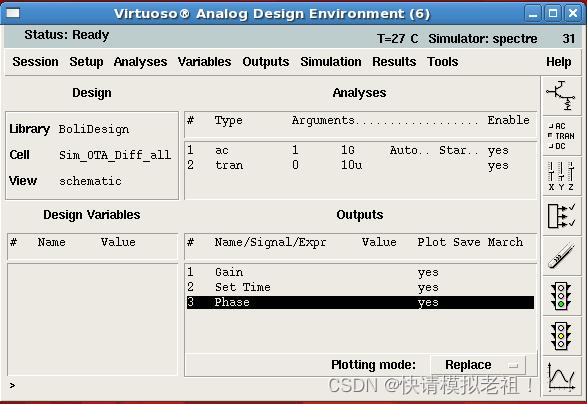

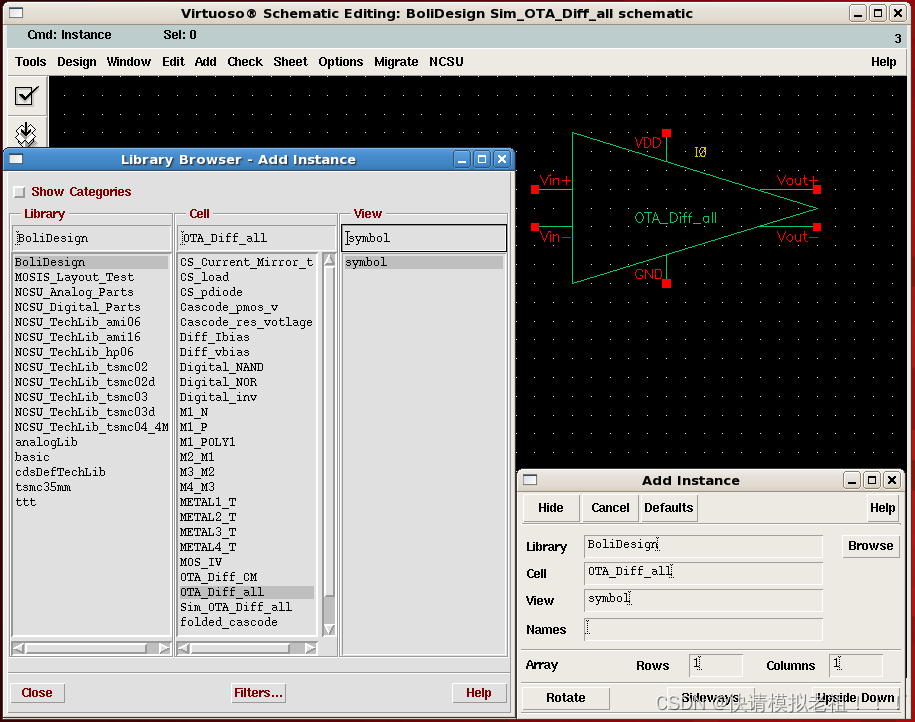

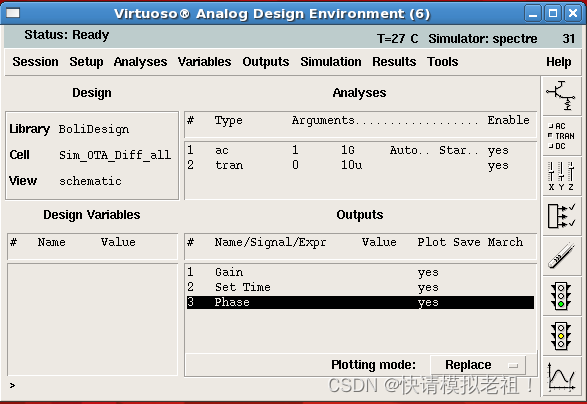

c.搭建仿真平台,仿真Gain,Set Time,CMRR,PSRR

|

图28 导入symbol |

图29 总仿真环境搭建与测量项一览 |

|

图30 总测试原理图一览 | |

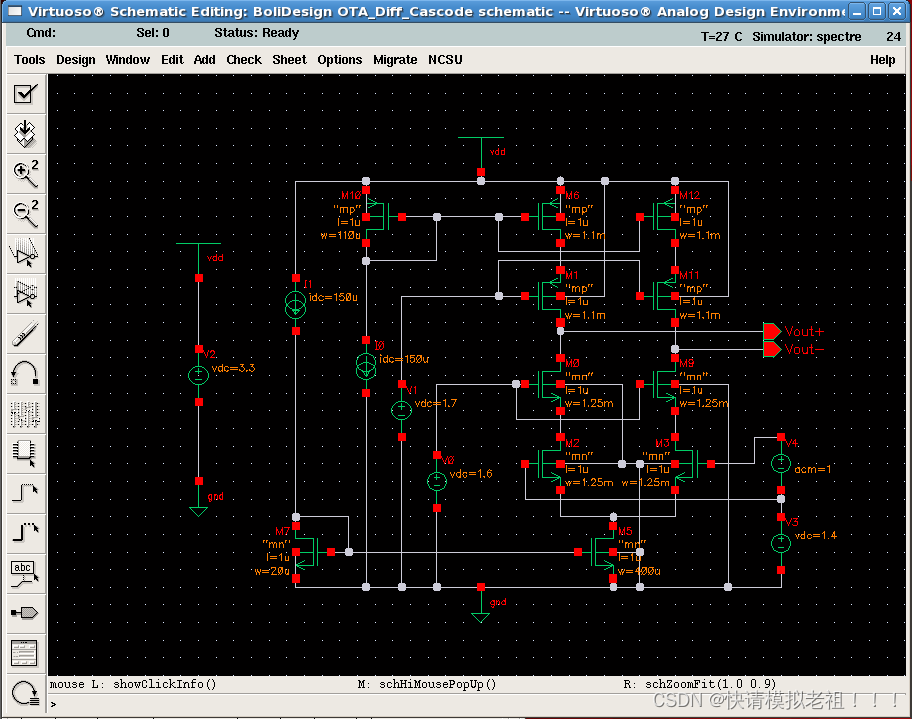

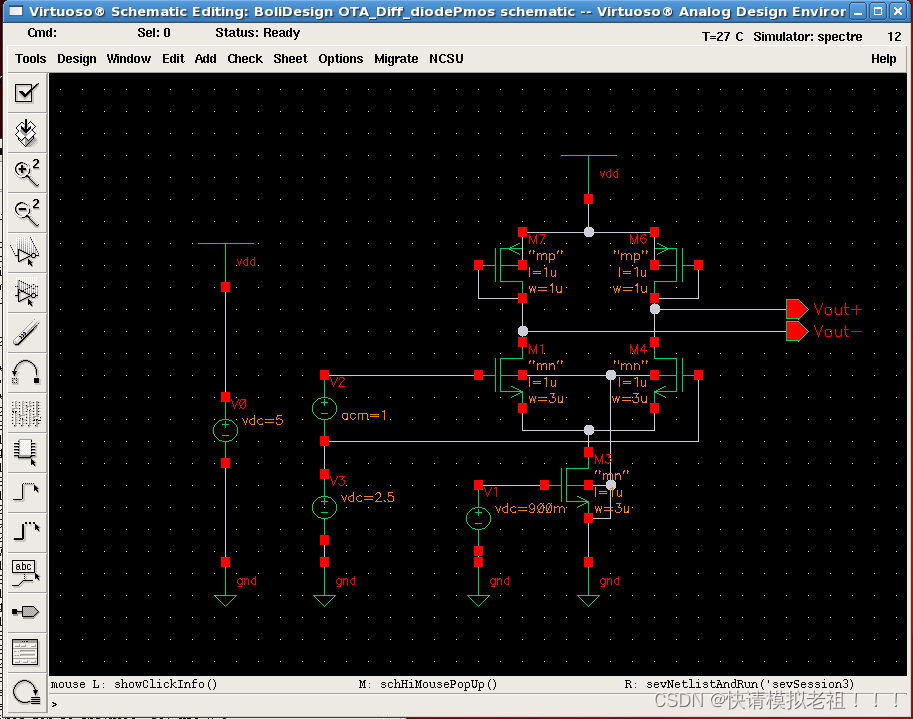

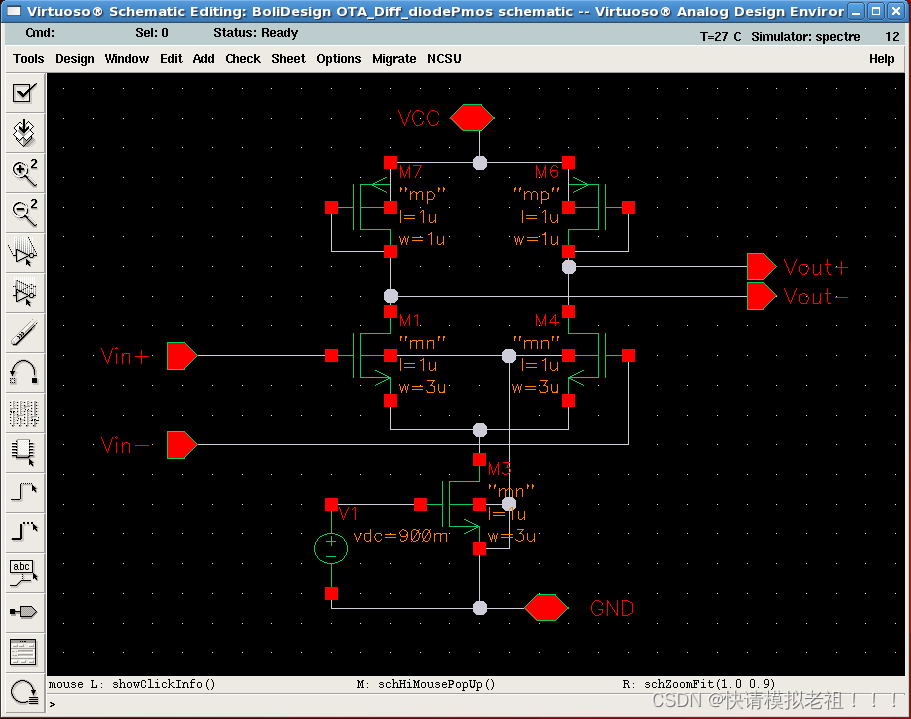

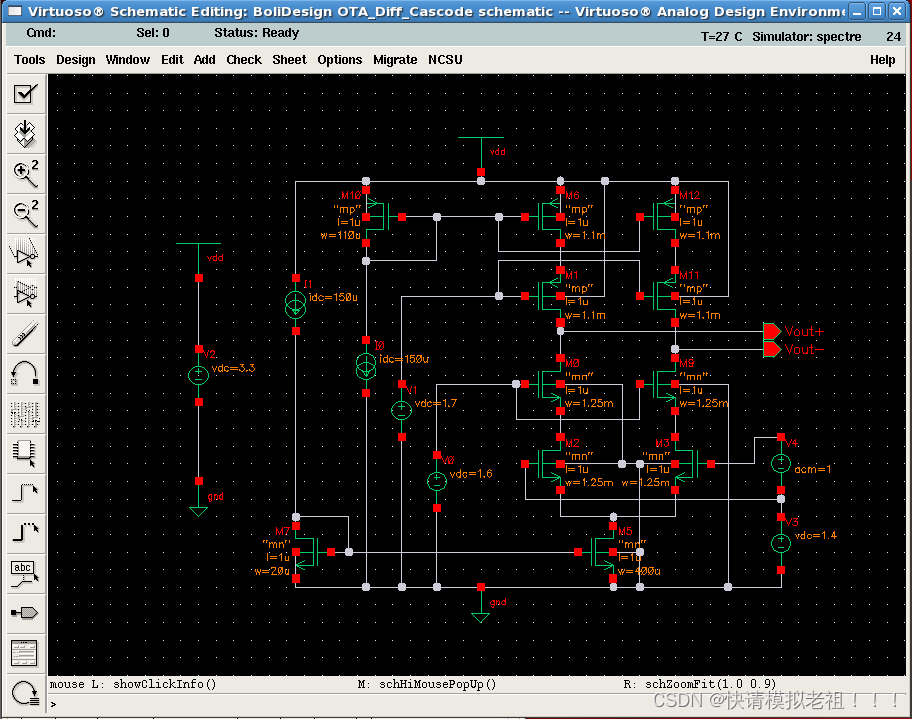

3.【实验三】共源共栅全差动放大器

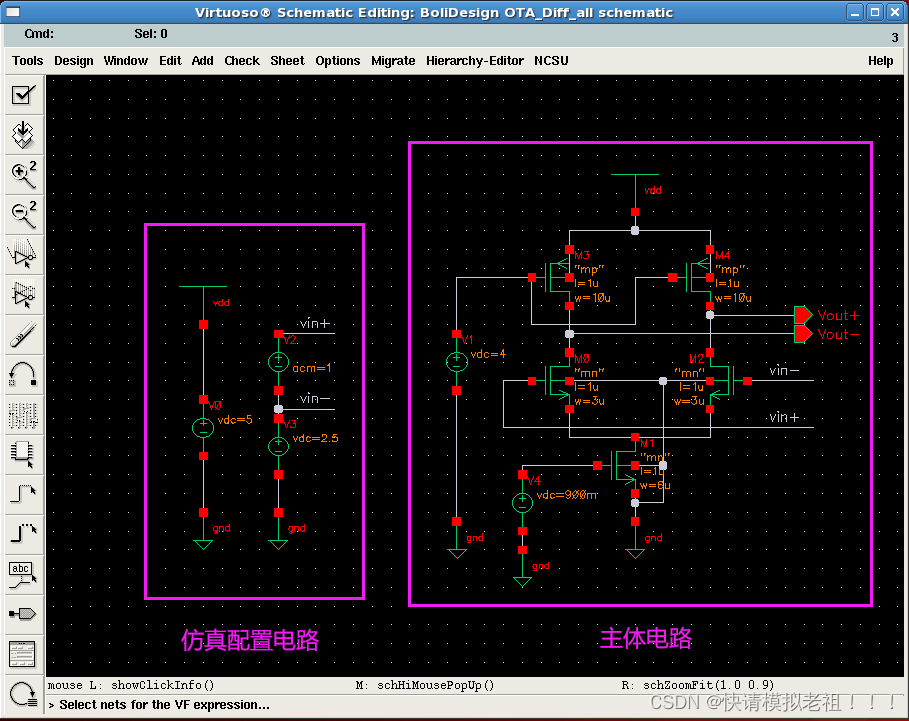

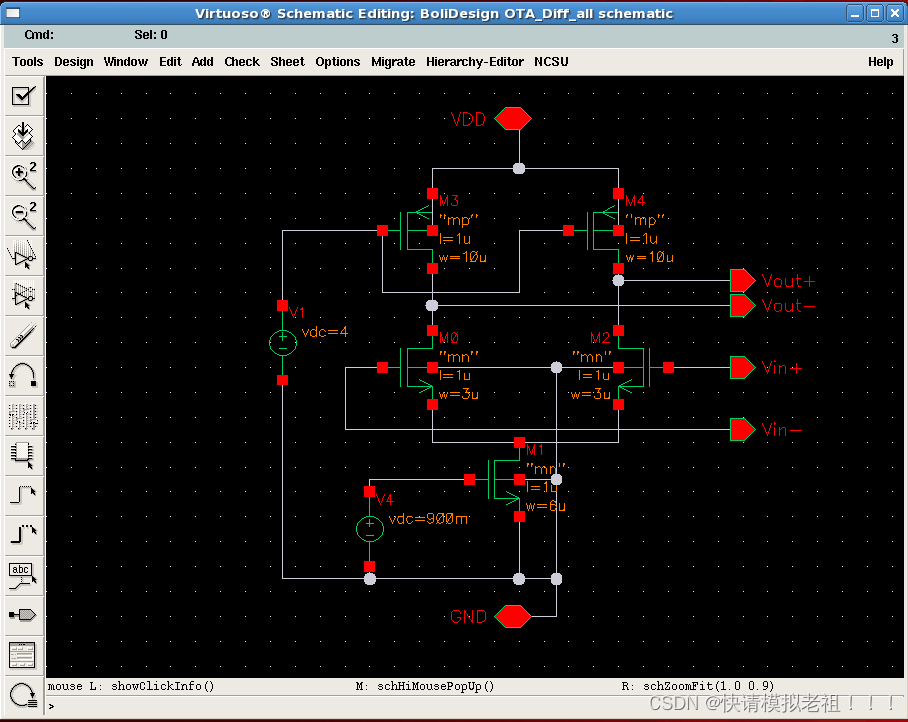

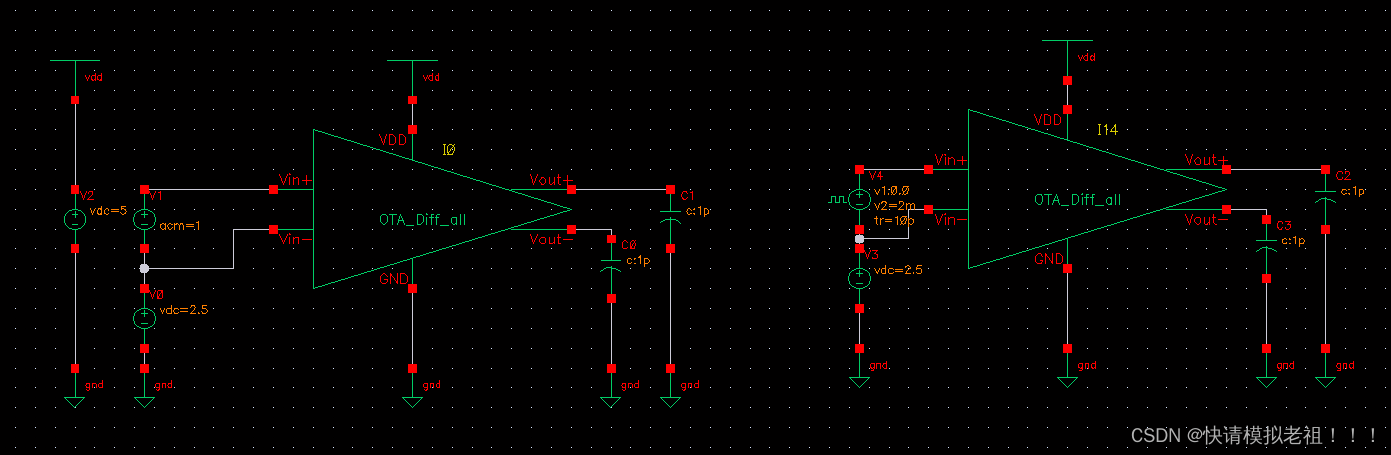

a.原理图搭建

|

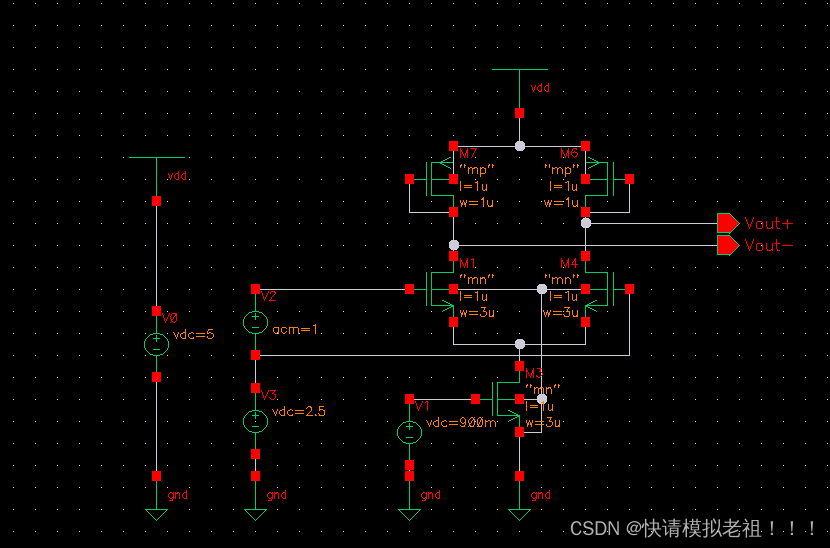

图31 如图搭建原理图 |

图32 仿真环境配置 |

|

图33 查看放大器工作区无误 |

b.生成symbol

c.搭建仿真平台,仿真Gain,Bandwidth,Set Time,CMRR,PSRR

五、仿真结果及分析

1.【实验一】二极管连接的MOS做负载的差动对电路

a. schematic

图34 二极管连接的MOS做负载的差动对原理图

图35 测试原理图

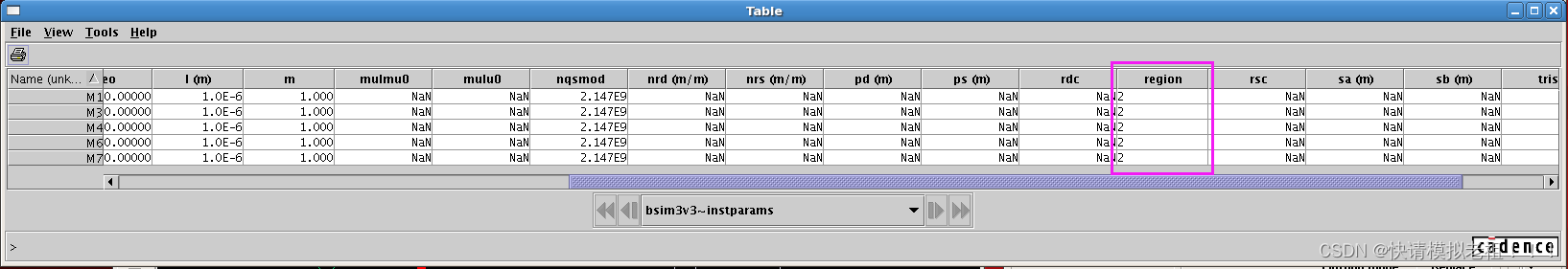

b.各管子工作区

图36 工作区状态

可见,所有MOS管均处在饱和区,偏置配置正常。

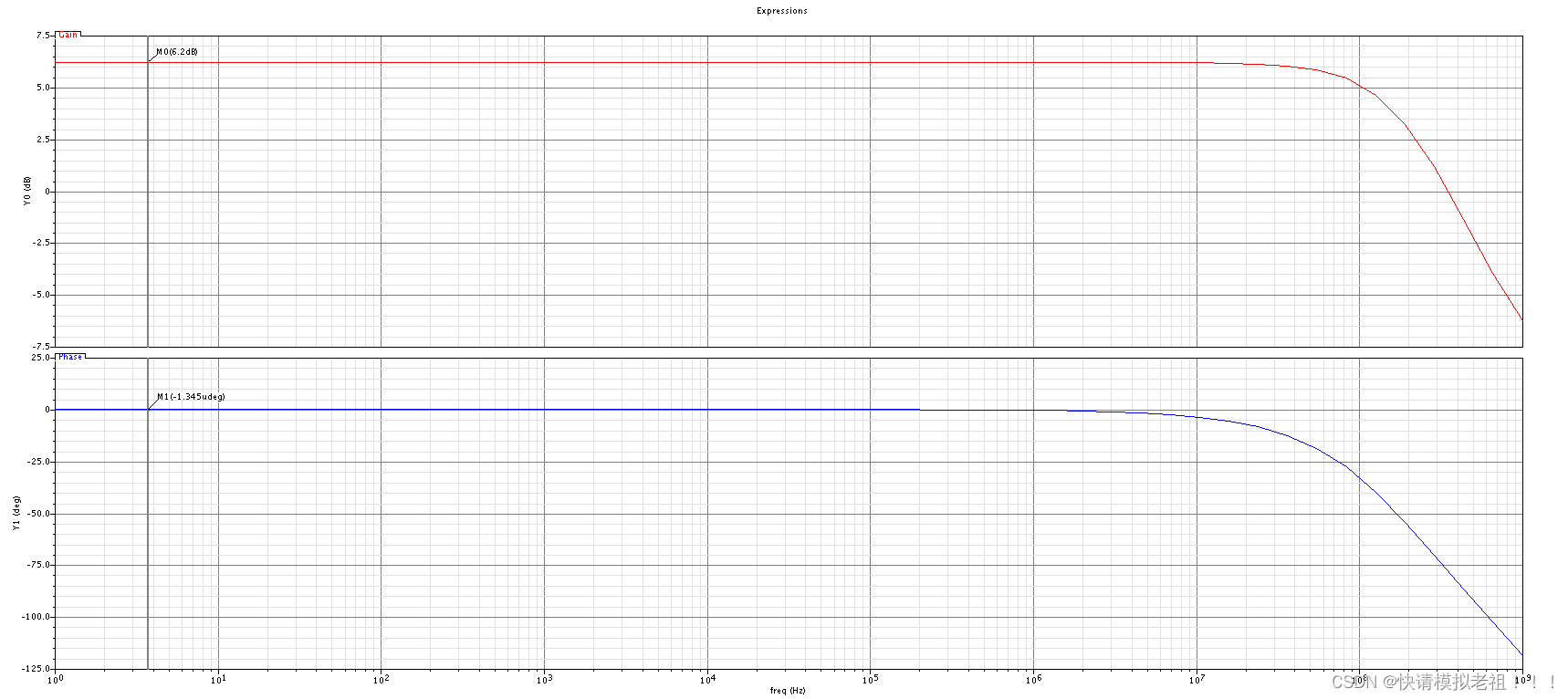

c. Gain & Bandwidth

图37 Gain & Phase

可见,此电路增益为6.2dB,未实现放大功能,但所有MOS均处于放大状态,这是由于PMOS二极管连接大大降低了电路的输出电阻,导致增益下降,此结构不作为运放的主放大电路。由于电路两个极点都是低阻抗节点,考虑到负载电容的影响,电路主极点肯定很小。

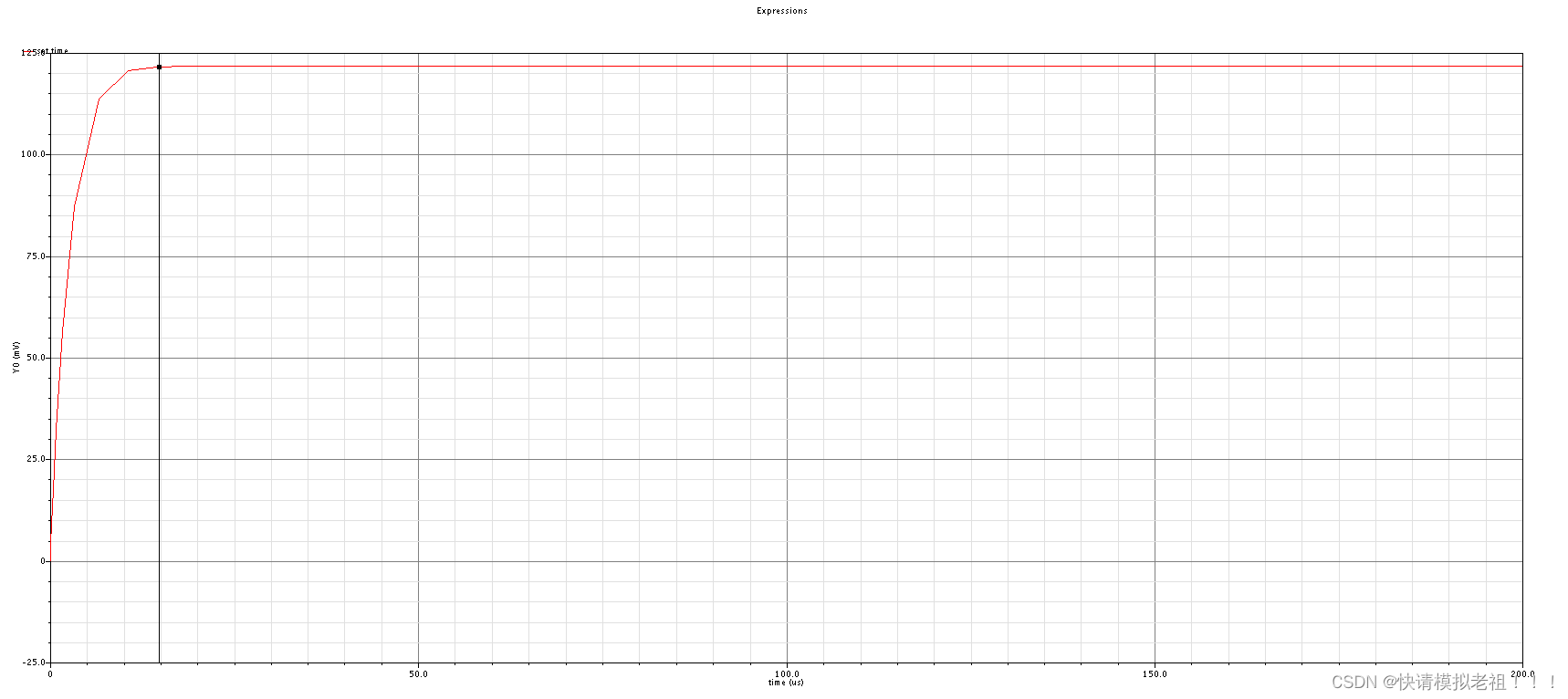

d. Set Time

图38 Set Time

可见,此运放的建立时间为0.4us。

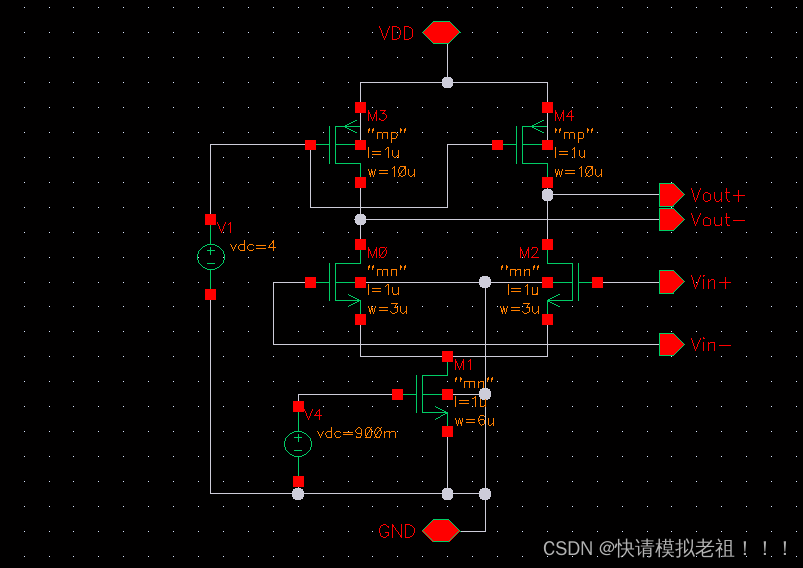

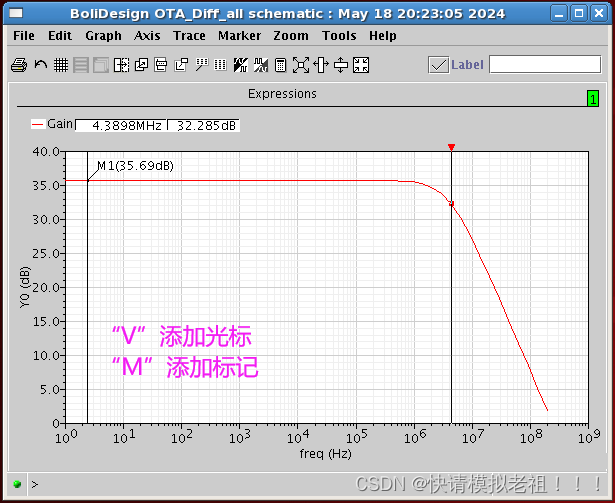

2.【实验二】全差动电流源作负载

a. schematic

图39全差动电流源作负载原理图

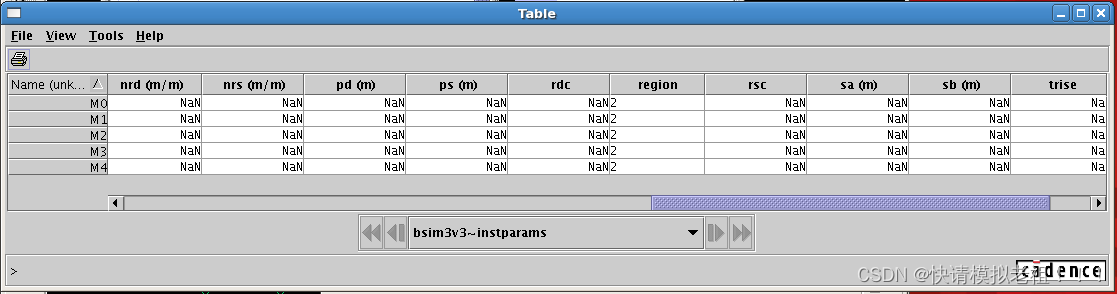

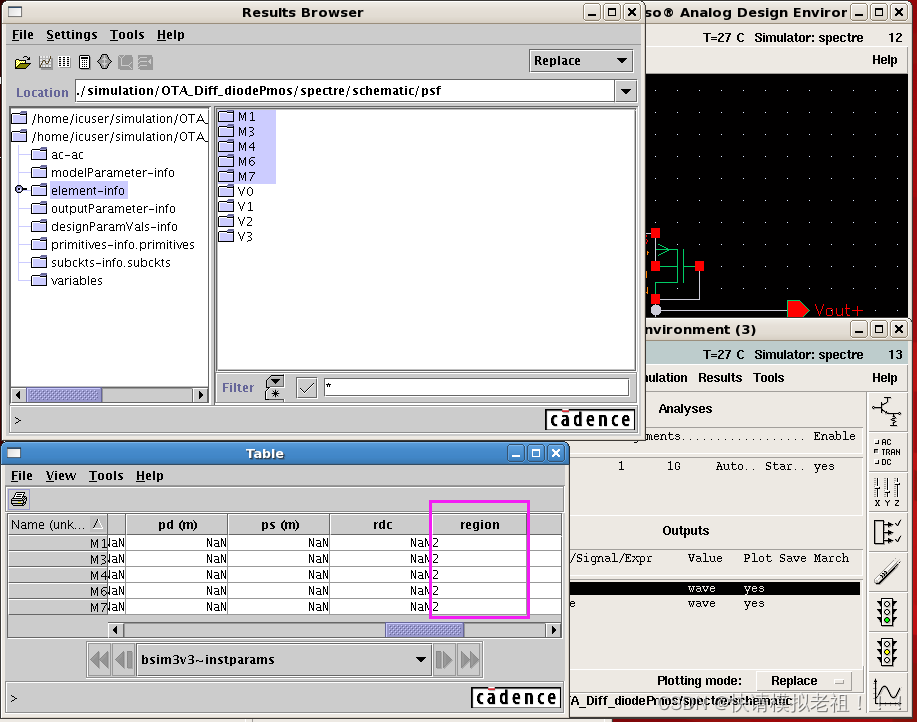

b.各管子工作区

图40 工作区状态

可见,所有MOS管均处在饱和区,偏置配置正常。

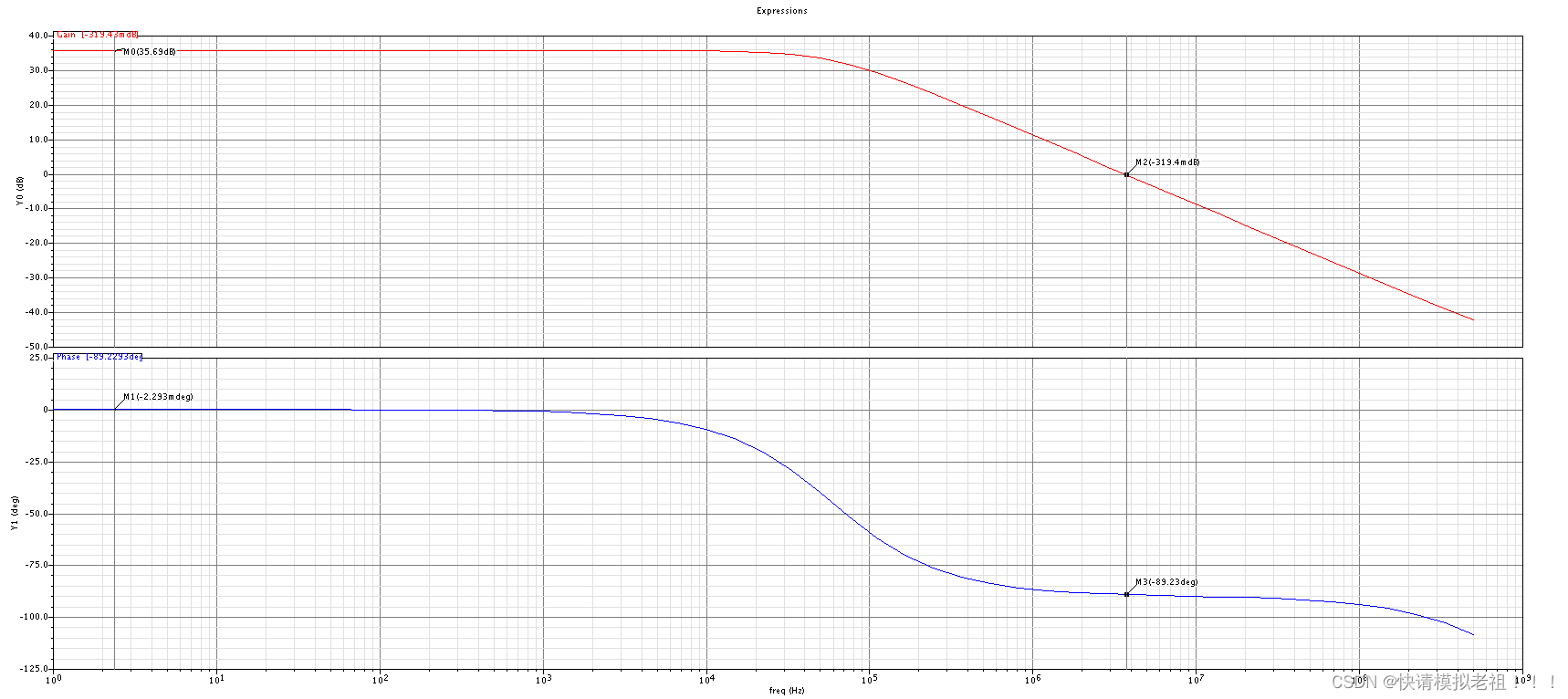

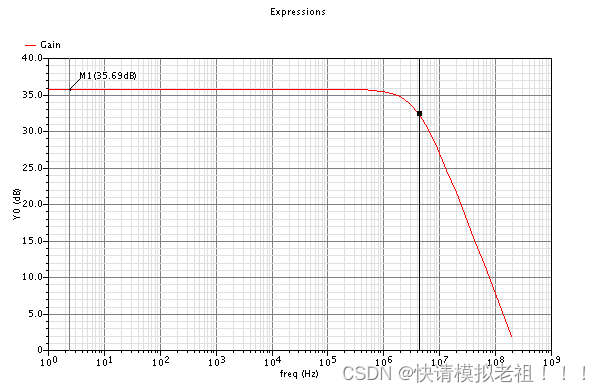

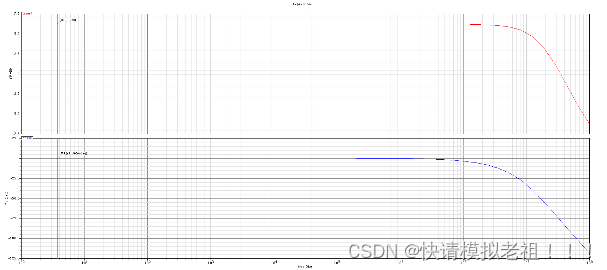

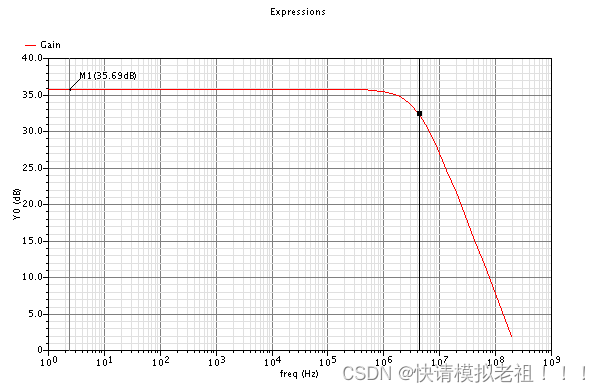

c. Gain & Bandwidth

图41 Gain & Phase

如图所示,该电路的增益为35.69dB。0dB时相位为-90,相位裕度90度,妥妥的单极点系统,输出阻抗为r01||r02,输出为高阻抗节点。

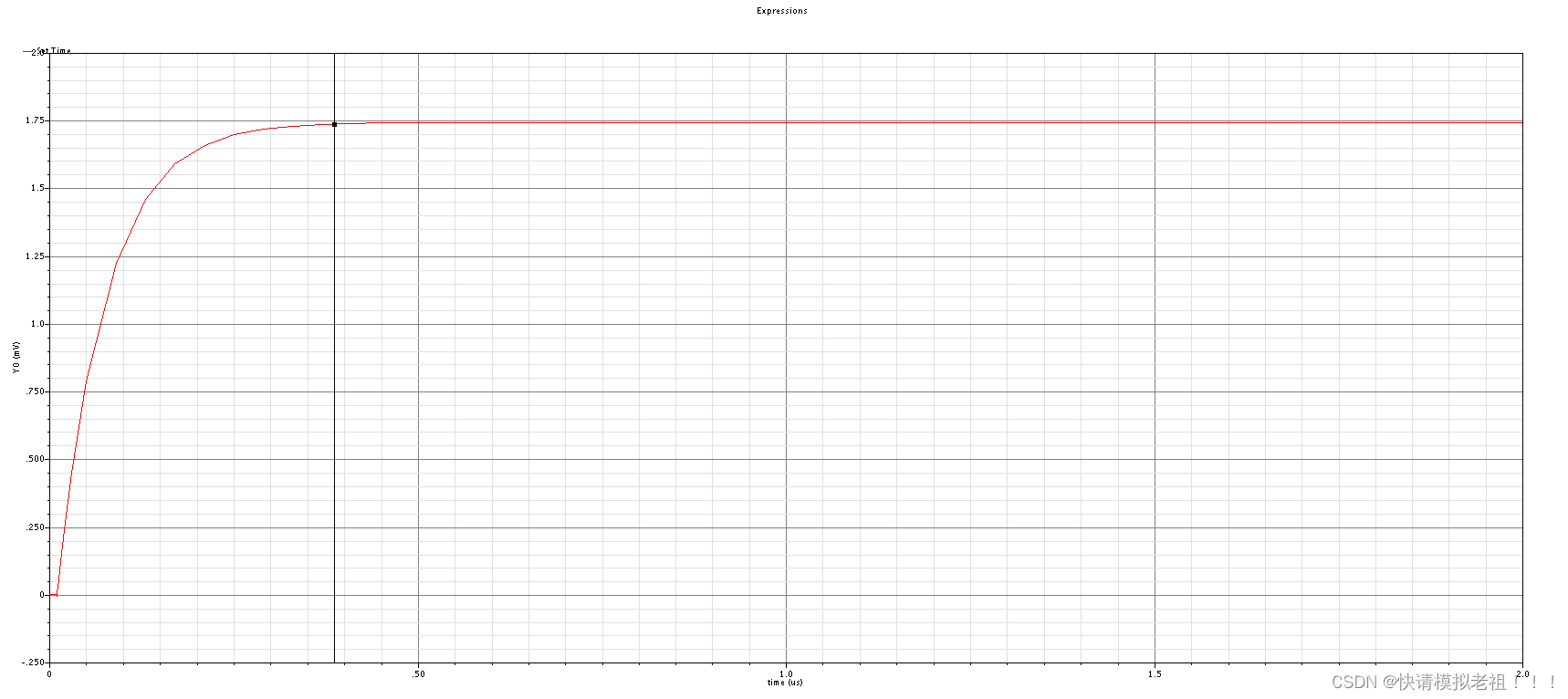

d. Set Time

图42 Set Time

可见,此电路的建立时间为15us。SR太小了,几乎是不能用。

3.【实验三】共源共栅全差动放大器

a. schematic

图43 Set Time

【备注】:额……没调出来。

六、心得体会

本次实验主要分为三个小实验,第一个实验是二极管连接的MOS做负载的差动对;第二个实验是全差动电流镜做负载的差动对;第三个实验是共源共栅的全差动放大器。实验步骤主要有搭建电路,调工作点确保每个管子处于饱和状态,对电路进行封装,使用封装好的模型搭建测试电路,得到增益,相位裕度,建立时间。

本次实验存在问题如下:

- 第一次对双输入双输出的电路进行测试,对于一些参数如CMRR,PSRR等参数的测量存在疑惑。

- 每个电路可以分为主放大器,负载,尾电流,偏执电路。当负载为电流源时,不清楚电路总电流由哪个决定。后来想明白了,电流由负载电流镜决定,尾电流确保两个差动输入放大器偏置正常,电路的增益可以调节放大管的宽长比或阈值电压适当增大。

- 一般的设计思路应该是根据电路功耗对每条路分配电流,根据GBW,输出摆幅,输出工作点确定电路的过驱动电压,然后由电流和过驱动电压算出每一条路的宽长比,验证增益,求解偏置电压范围。如果增益不够,增大栅长,保持宽敞比不变。我们的实验缺少一些必要的设计指标,比如增益多少,带宽多少。实验中我大多都是自己设置指标,导致有的指标表要求过高,对于这个电路很难满足,所以退而求其次,让管子饱和即可。

- 本周大多在搞集创相关的东西,所以时间上不是很充裕,后面我会在调第三个实验,争取有所收获。

再次感谢王老师的讲授,希望自己不负韶华。

、

、

819

819

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?