一、实验目的

1.学习电流镜做负载的差分对电路的电气特性,根据仿真现象使用理论对其分析 。

2.将做匹配的五管单元与未匹配的五管单元进行比较,了解两个电路的优劣,学会更具具体问题进行相应的设计。

3.学习运放参数测试的各种电路,了解其测试原理(CMRR,PSRR,GBW,噪声)。

4.熟悉IC514仿真环境,使用计算器对参数进行运算和显示。

二、实验环境

集成电路设计实验室;Red Hat Enterprise linux5、Cadence IC Design Tools 5.10.41

三、实验原理

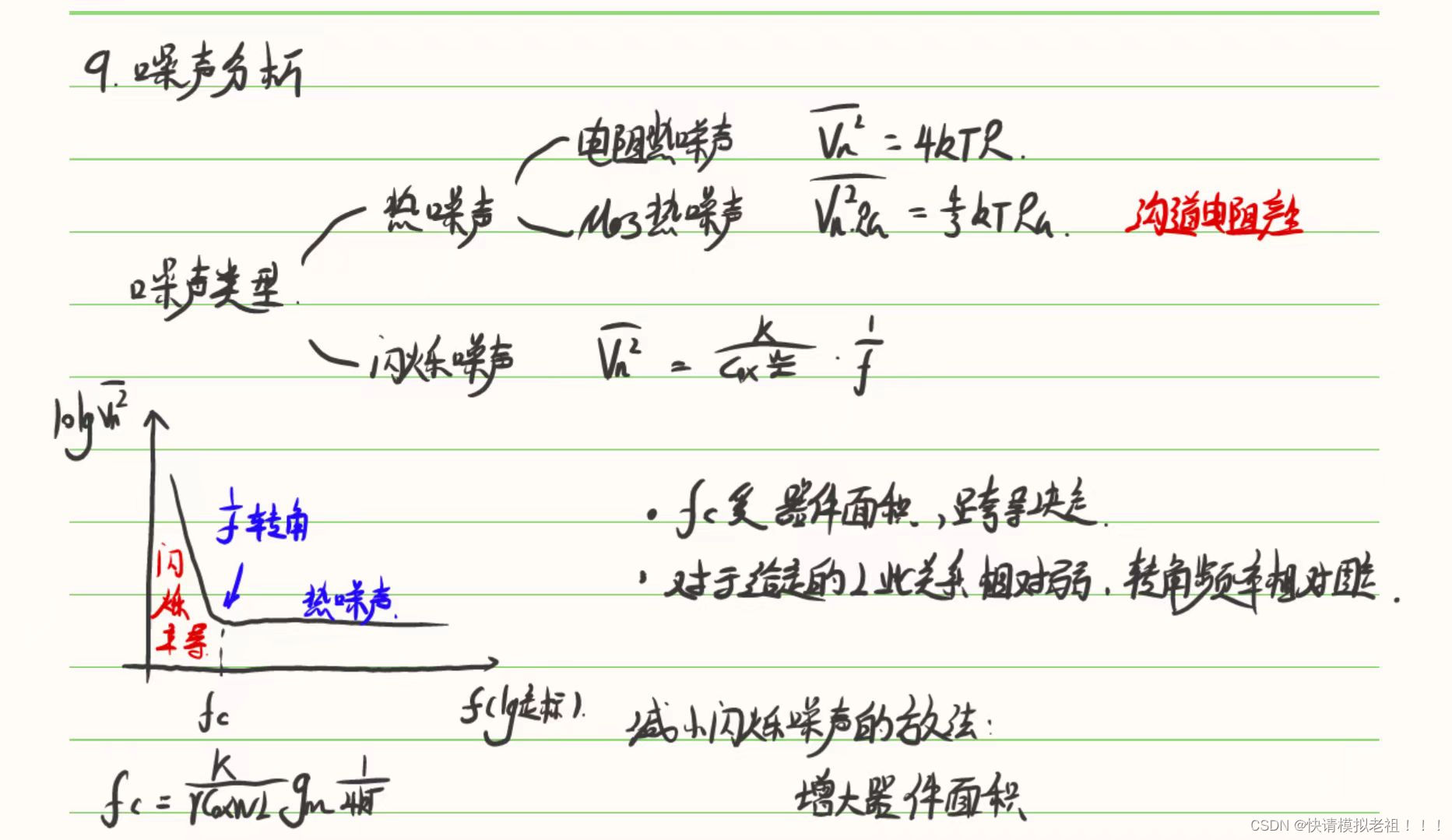

1. 噪声分析梗概

图1 噪声分析笔记

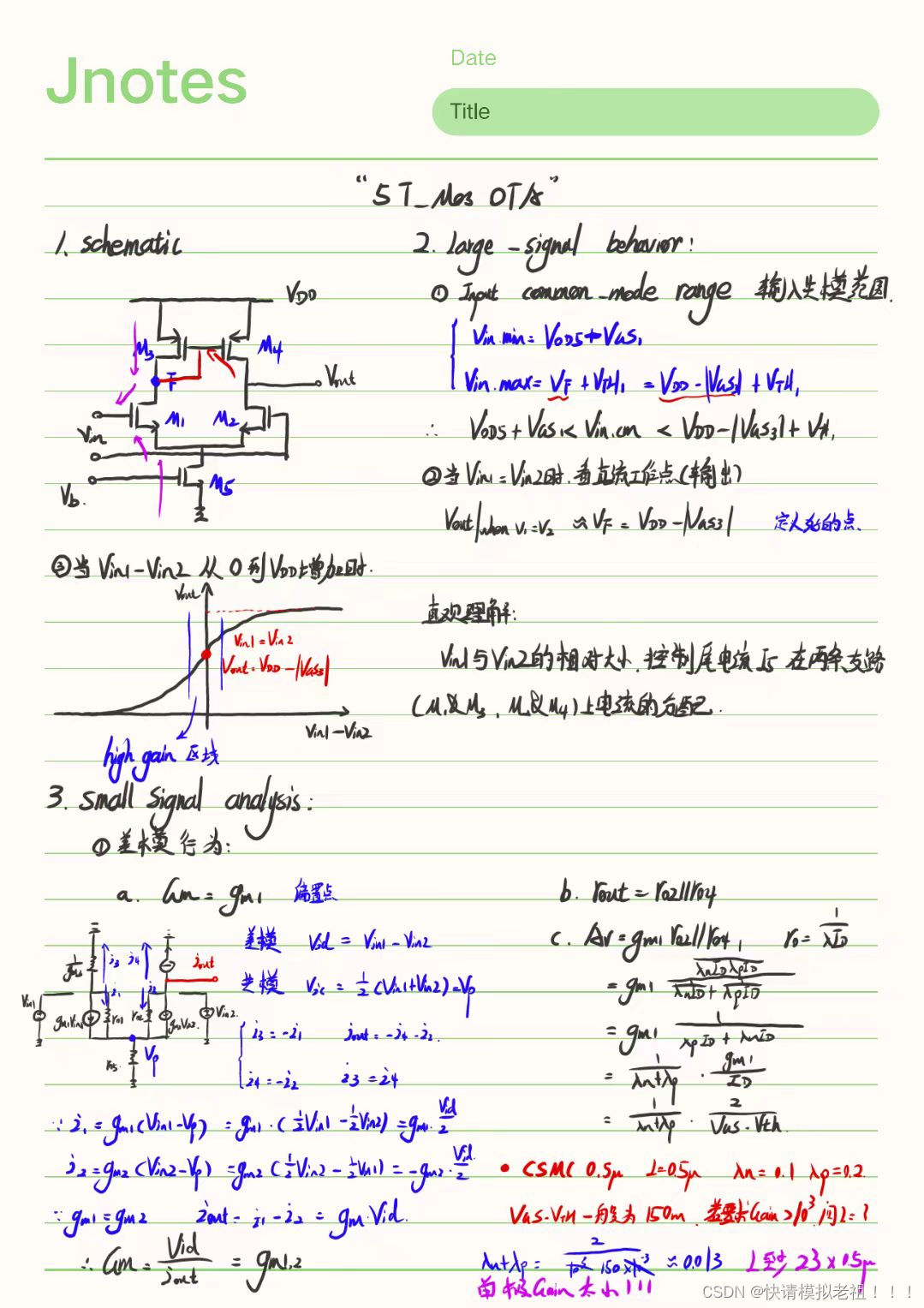

2. 五管单元电路详解

图2 五管单元电路笔记

3. CM响应,CMRR以及CMRR测试电路

图3 CM响应,CMRR以及CMRR测试电路笔记

4. 运放开环增益与带宽测试电路,负反馈引入对幅频特性曲线的影响

图4 运放开环增益与带宽测试电路,负反馈引入对幅频特性曲线的影响笔记

5. 运放PSRR测试电路解析

图5运放PSRR测试电路笔记

四、实验步骤

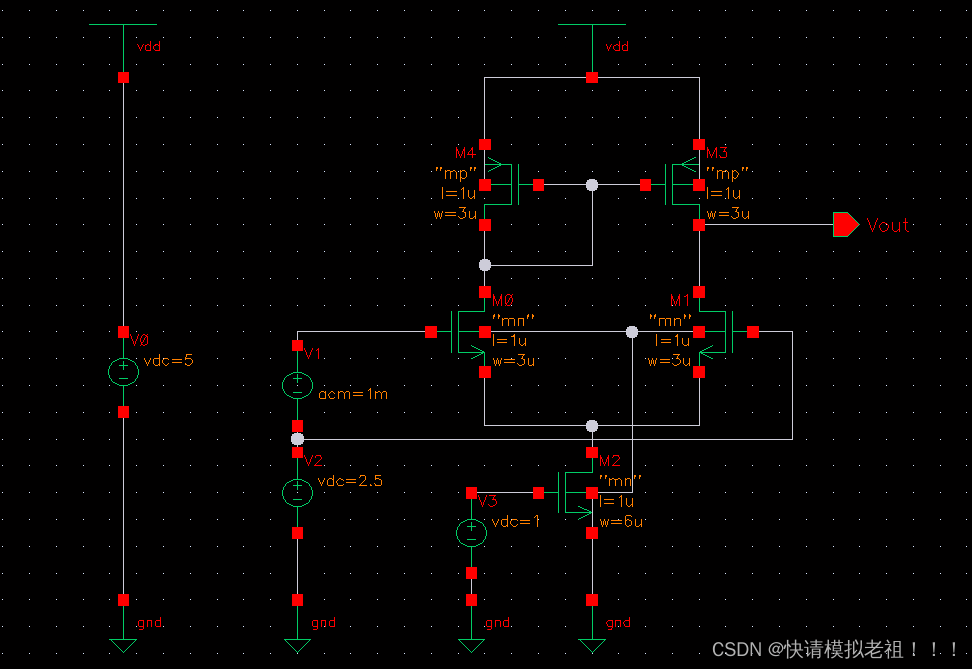

1.【实验一】电压偏置的5TMOS放大器(已做匹配)

a. 开环增益与带宽测试

|

图6 绘制开环增益测试电路图 |

图7 配置仿真环境 |

|

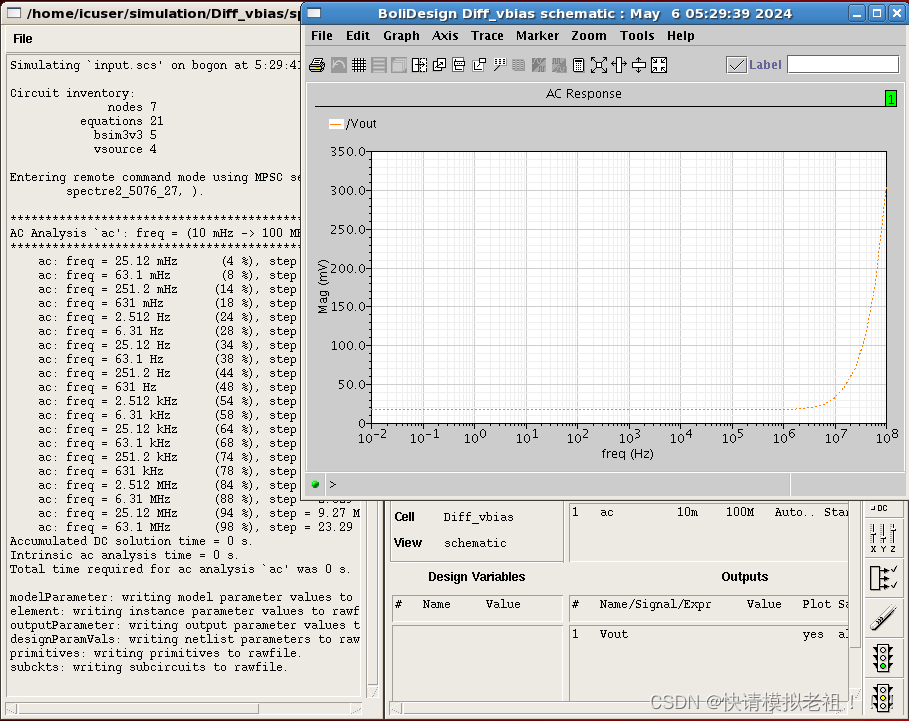

图8 开启仿真,查看仿真结果 |

图9 依次添加波形测量项 |

b. 噪声分析

|

图10 噪声法分析测试电路图 |

图11 配置仿真参数 |

|

图12 查看仿真结果 |

图13 依次添加测量项 |

c. CMRR测试

|

图14 CMRR测试电路图 |

图15 配置仿真参数 |

|

图16 查看仿真结果 |

图17 依次添加测量项 |

d. PSRR测试

|

图18 PSRR测试电路图 |

图19 配置仿真参数 |

|

图20 查看仿真结果 |

图21 查看仿真结果 |

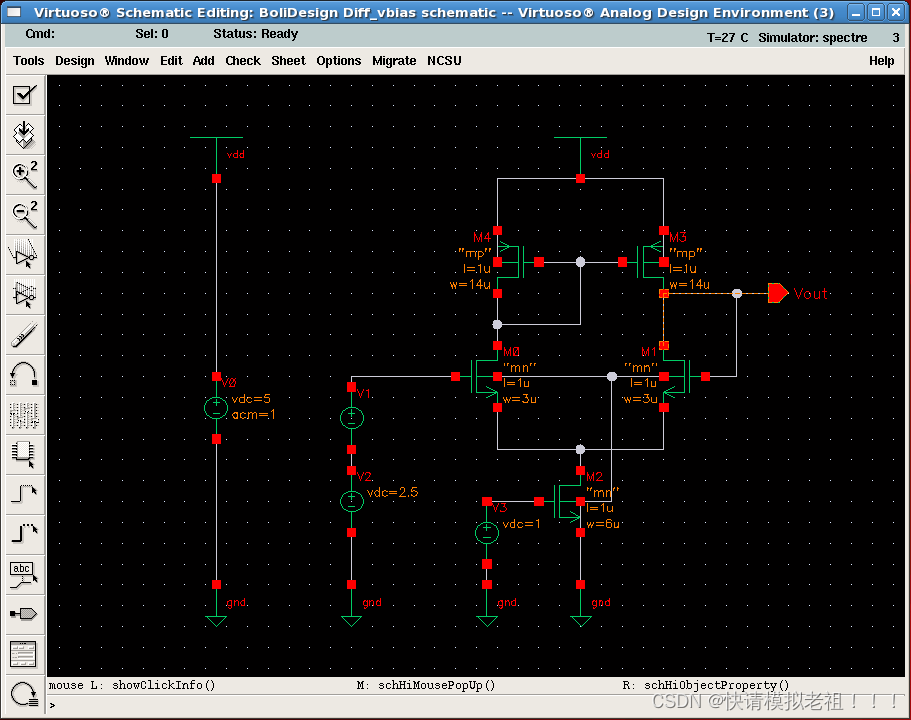

2.【实验二】电压偏置的5TMOS放大器(未做匹配)

0. 将原理图参数修改为下图,实验步骤和实验一一致。

图22电压偏置的5TMOS放大器(未做匹配)原理图

a. 开环增益与带宽测试

b. 噪声分析

c. CMRR测试

d. PSRR测试

3.【实验三】电流偏置的5TMOS放大器

0. 将原理图参数修改为下图,实验步骤和实验一一致。

图23电流偏置的5TMOS放大器原理图

a. 开环增益与带宽测试

b. 噪声分析

c. CMRR测试

d. PSRR测试

五、仿真结果及分析

1.【实验一】电压偏置的5TMOS放大器(已做匹配)

0. schematic

图24 电压偏置的5TMOS放大器(已做匹配)原理图

a. 开环增益与带宽测试

图25电压偏置的5TMOS放大器各管工作状态展示

|

图26 开环增益与带宽测试原理图 |

图27 开环增益与带宽测试结果 |

由图25可知,所有的MOS FET均工作在饱和区。在原理部分讨论的测试电路下,设置Vac=1m。由图27可知,放大了47.14倍,-3dB带宽在6.5M处。

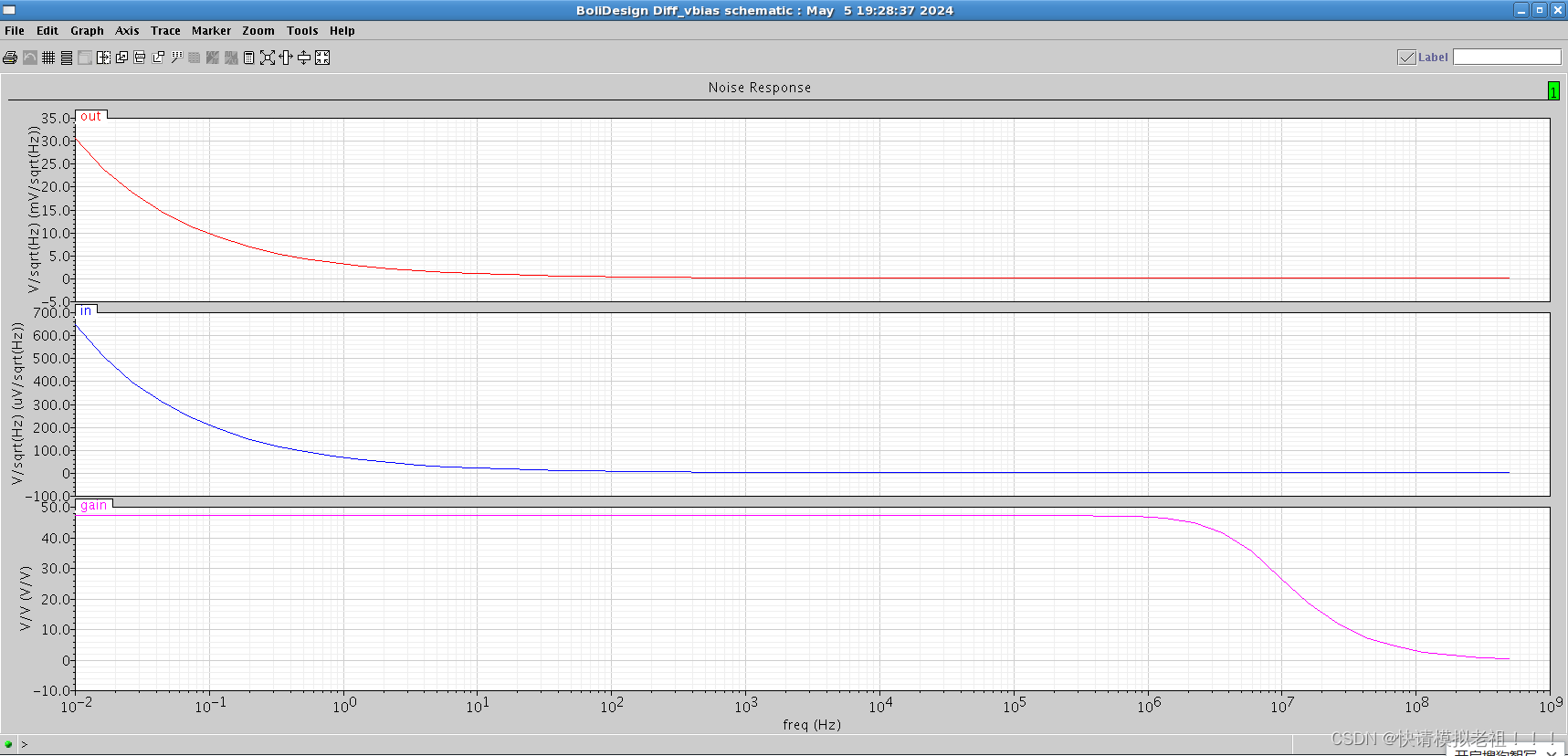

b. 噪声分析

|

图28 噪声测试原理图 |

图29 噪声分析结果 |

之前原理部分的讨论,低频处大的噪声干扰主要为闪烁噪声,过转角频率后是热噪声主导。

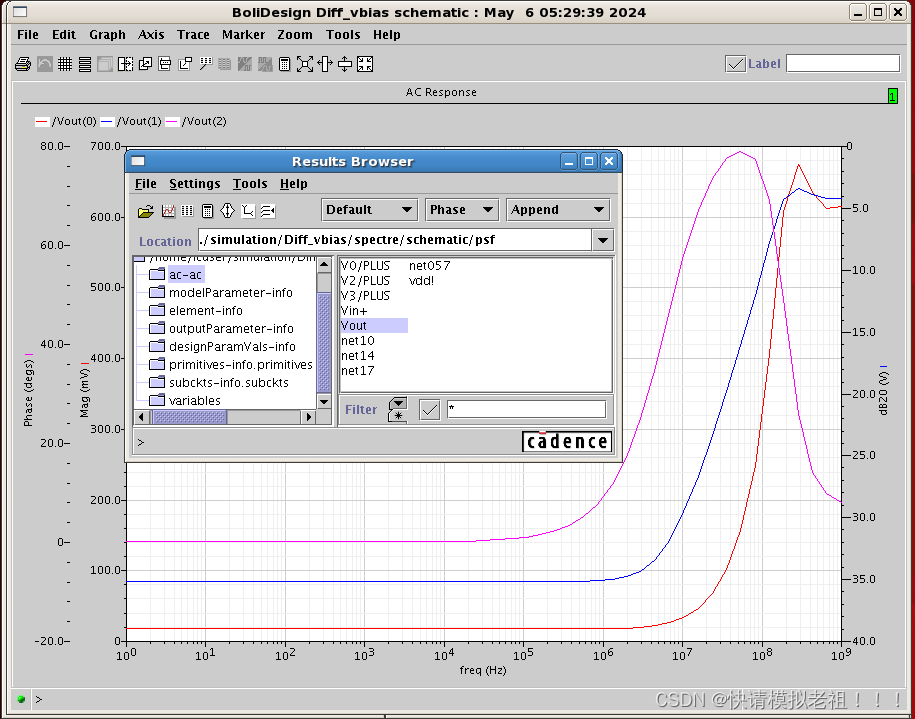

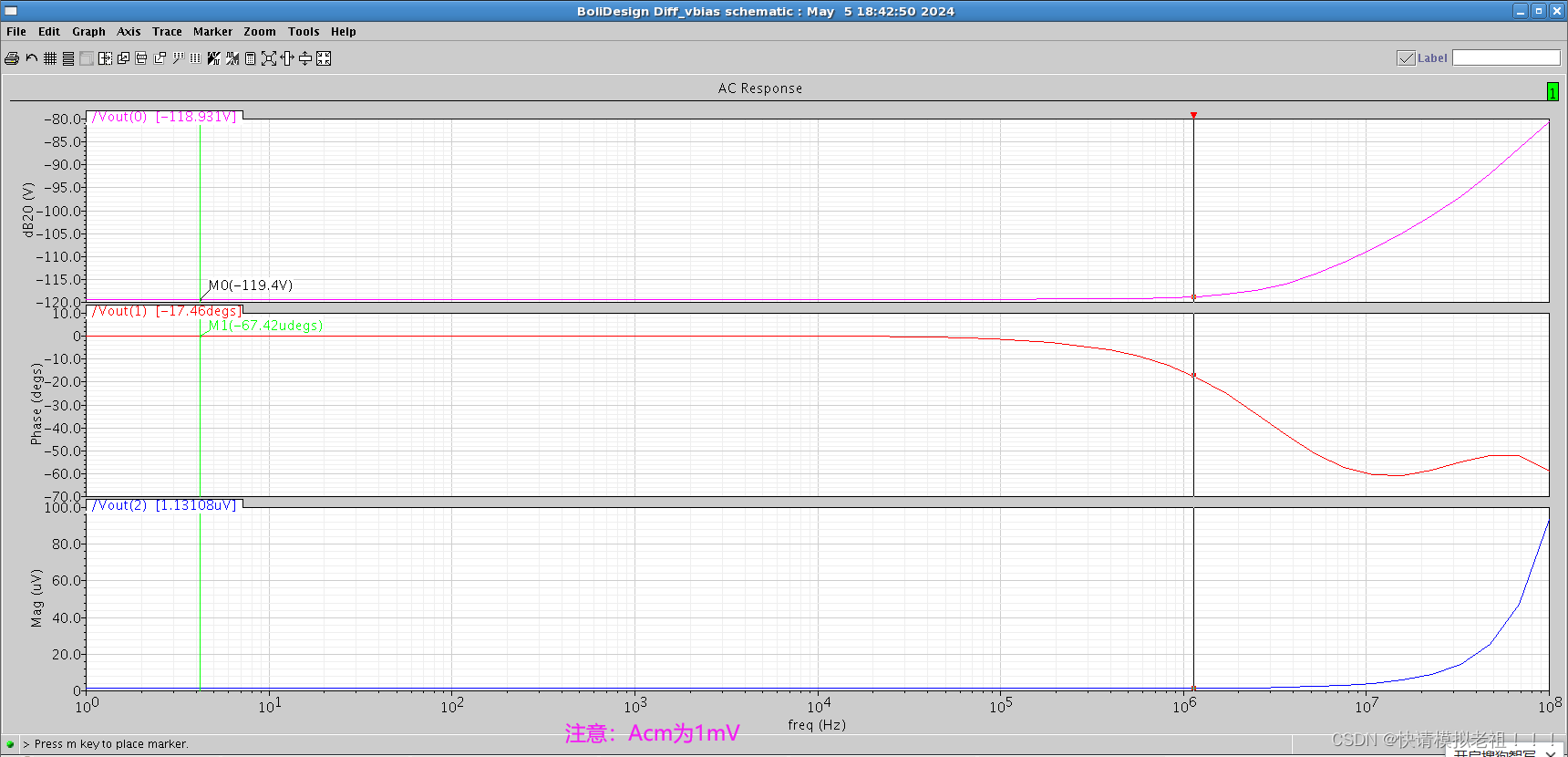

c. CMRR测试

|

图30 CMRR测试原理图 |

图31 CMRR测试结果 |

按照原理部分的分析,设置Vacm为1m,此时1/CMRR=20lg(1.13m)= -58.9dB。则CMRR为 58.9dB。

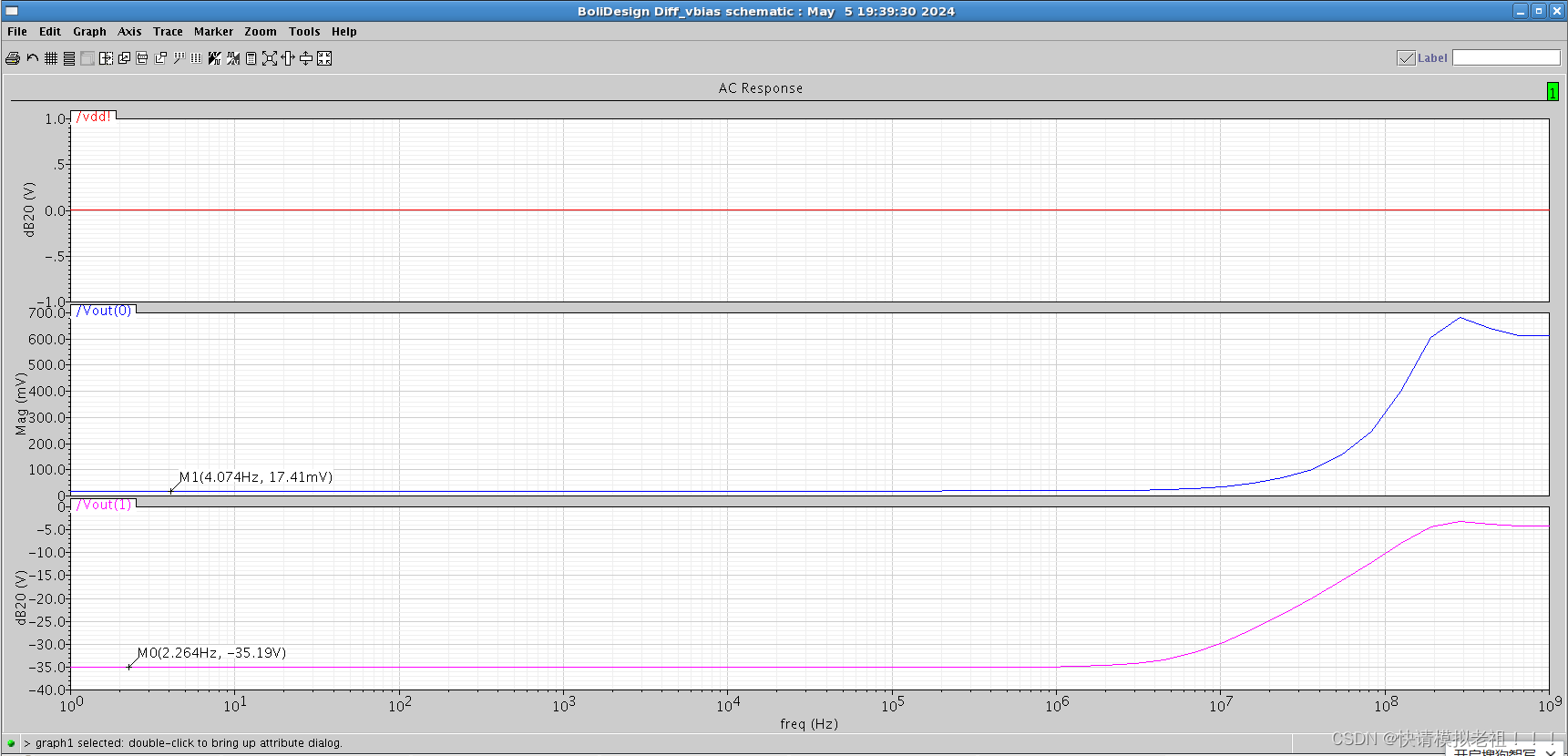

d. PSRR测试

|

图32 PSRR测试原理图 |

图33 PSRR测试结果 |

按照原理部分的分析,设置vdd(ac)为1V,此时1/CMRR=20lg(Vout)= -35.19dB。则CMRR为 35.19dB。

2.【实验二】电压偏置的5TMOS放大器(未做匹配)

0. schematic

图34 电压偏置的5TMOS放大器(未做匹配)原理图

a. 开环增益与带宽测试

图35 电压偏置的5TMOS放大器(未做匹配)各管工作状态展示

|

图36 开环增益与带宽测试原理图 |

图37 开环增益与带宽测试结果 |

由图35可知,所有的MOS FET均工作在饱和区。在原理部分讨论的测试电路下,设置Vac=1m。由图37可知,放大了46.5倍,-3dB带宽在13.6M处。由于此时PMOS尺寸减小约4.6倍,导致寄生电容减小,所以带宽增加。

b. 噪声分析

|

图38 噪声测试电路原理图 |

图39 噪声分析测试结果 |

之前原理部分的讨论,低频处大的噪声干扰主要为闪烁噪声,过转角频率后是热噪声主导。

c. CMRR测试

|

图40 CMRR测量原理图 |

图41 CMRR测量结果 |

按照原理部分的分析,设置Vacm为1,此时1/CMRR=20lg(Vout)= -53.123dB。则CMRR为 53.123dB。

d. PSRR测试

|

图42 PSRR测量原理图 |

图43 PSRR测量结果 |

按照原理部分的分析,设置vdd(ac)为1V,此时1/CMRR=20lg(Vout)= -23.48dB。则CMRR为 23.48dB。

3.【实验三】电流偏置的5TMOS放大器

0. schematic

图44 电流偏置的5TMOS放大器原理图

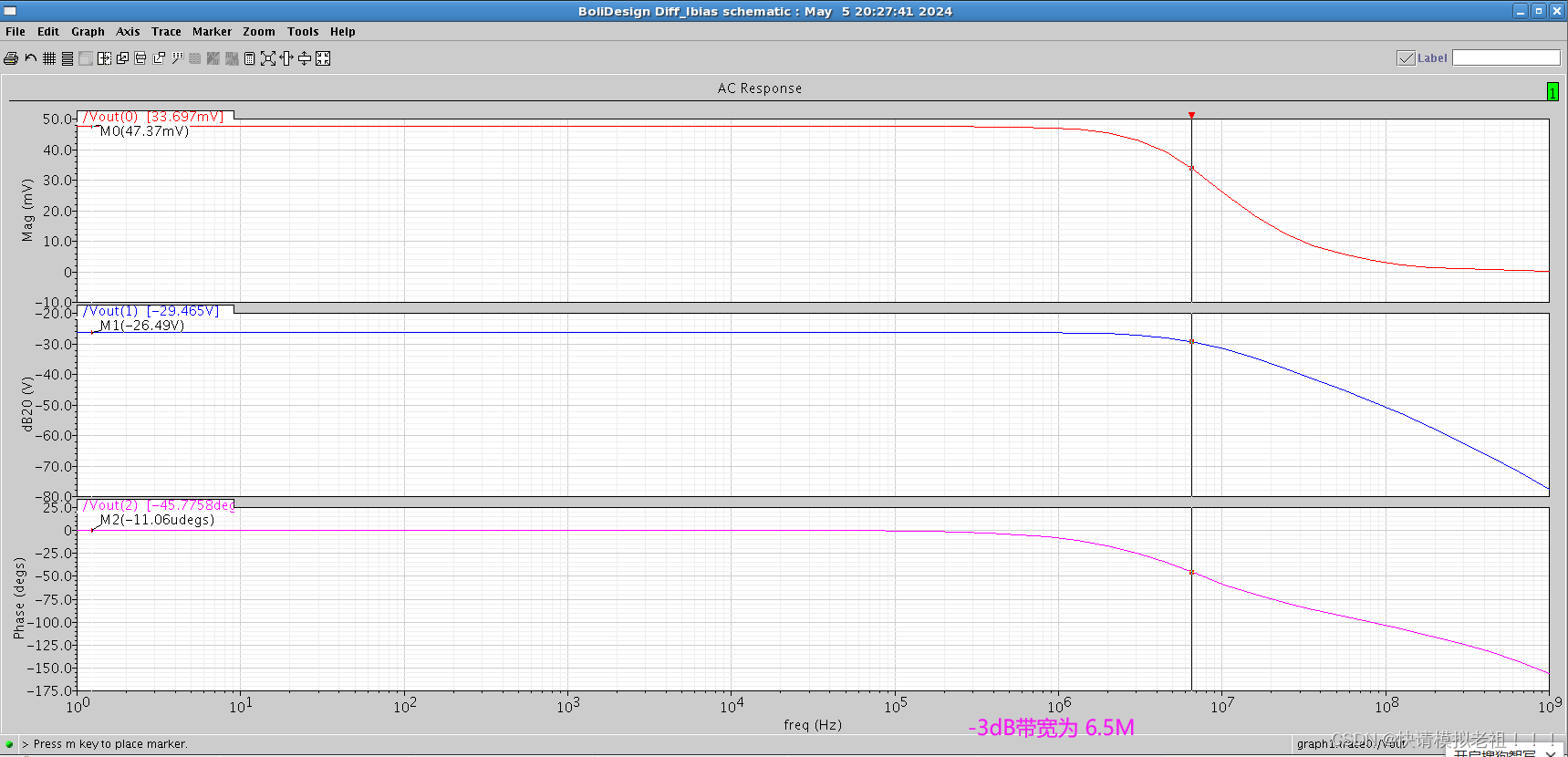

a. 开环增益与带宽测试

图45 电流偏置的5TMOS放大器各管工作状态

|

图46 开环增益与带宽测试原理图 |

图47开环增益与带宽测试结果 |

由图45可知,所有的MOS FET均工作在饱和区。在原理部分讨论的测试电路下,设置Vac=1m。由图47可知,放大了33.697倍,-3dB带宽在6.5M处。

b. 噪声分析

|

图48 噪声测试电路原理图 |

图49 噪声测试电路测试结果 |

之前原理部分的讨论,低频处大的噪声干扰主要为闪烁噪声,过转角频率后是热噪声主导。

c. CMRR测试

|

图50 CMRR测量原理图 |

图51 CMRR测量结果 |

按照原理部分的分析,设置Vacm为1m,此时1/CMRR=20lg(1.058m)= -59.5dB。则CMRR为 59.5dB。

d. PSRR测试

|

图52 PSRR测量原理图 |

图53 PSRR测量原理图 |

按照原理部分的分析,设置vdd(ac)为1V,此时1/CMRR=20lg(Vout)= -35.22dB。则CMRR为 35.22dB。

4.【总结】做匹配与不做匹配的各参数对比

| 电路|测量项 | 增益/ dB | 带宽/MHz | 噪声 | CMRR/dB | PSRR/dB |

| Wp=14u;Wn=3u;L=1u | 47.14 | 6.50 | 59.50 | 35.19 | |

| Wp=3u;Wn=3u;L=1u | 46.50 | 13.60 | 53.12 | 23.48 | |

| 电流偏置(匹配) | 39.14 | 6.50 | 58.90 | 35.22 |

表中电流偏置和电压偏置数据(除增益外)存在微小差异,增益的差别在于偏置电流10uA,小于偏置电压为1V时的尾电流。经后期验证后,得到尾电流一致时,增益一致。

表第二项带宽很大的原因在于pmos尺寸相较其他两个大大减小,使得寄生电容减小,带宽增大。匹配的好处在于增大了共模抑制比和电源抑制。换算为线性坐标系,以CMRR为例,匹配的干扰衰减944倍,不匹配的干扰衰减446倍,足以见匹配的重要性,虽然损失了部分贷款,但是可以通过相位补偿等技术弥补。

六、心得体会

本次实验是第一次使用差动对放大器进行仿真,相较于之前各种放大器,它突出的特点就是不能使用常规的方法去表征其性能。所以我花了大量的时间去探究其原理以及为何要设计这样具体的电路去得到他的各项参数,如CMRR,PSRR等。所以在原理部分总结了这几天看的书,说是五管单元,其实已经是运放的核心部分了,下面我来梳理一下本次实验的收获:

1. 通过修改PMOS的栅宽,探究匹配与不匹配对运放PSRR,CMRR的影响。

2. 在做电压和电流对尾电流偏置的对比时,出现增益差别很大。根据现象-猜想-设计方案验证,这样的思考过程使我受益匪浅。

3. 在原理部分有一小段说L对增益的影响,其实这是设计的一项重要指标,对于增益确定有重要意义。

4. 运放各参数测量电路:

使用我在IC618上的二阶运放对GBW,Gain,CMRR,PSRR,Slew Rate,Output Swing 等参数做测量,进一步加深影响。列举一些成果:

图54 带密勒补偿的二阶运放参数测试电路图

|

图55 带密勒补偿的二阶运放CMRR测试结果 |

图56 带密勒补偿的二阶运PSRR测试结果 |

|

图57 带密勒补偿的二阶运放SR测试结果 |

图58 密勒补偿的二阶运放输出摆幅测试结果 |

5. 看书和笔记总结,不同观点的整合以及设计脉络梳理,这很重要!

再次感谢王老师的循循善诱,希望自己在模拟的世界走的更远!

9229

9229

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?