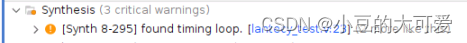

问题:在综合和布线的时候都如下错误

在综合过程中就已经报错,但是只提示报错的文件,没有具体到哪一行,哪一个寄存器出现了错误;

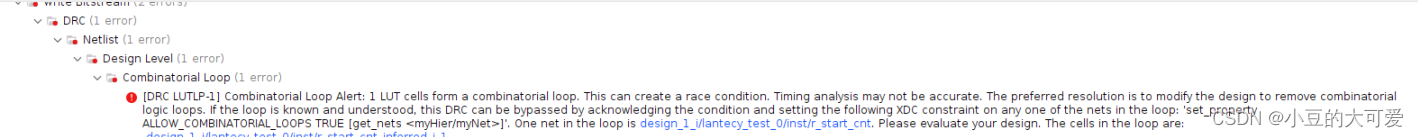

随即在布线的过程中,报错r_start_cnt该寄存器存在问题

仔细看出错的寄存器对应的逻辑代码:

always @(clk) begin

if(r_start_cnt == 1'd1 && !r_fast_flag && pos_adc3_valid)

r_start_cnt <= 1'd0;

else if(r_start_cnt == 1'd1 && r_fast_flag

文章讲述了在综合和布线过程中遇到的错误,源于一个always块中输出寄存器r_start_cnt被误用为输入,导致循环逻辑。通过修改代码,移除输出作为输入的结构,解决了错误并确保了综合布线的成功。

文章讲述了在综合和布线过程中遇到的错误,源于一个always块中输出寄存器r_start_cnt被误用为输入,导致循环逻辑。通过修改代码,移除输出作为输入的结构,解决了错误并确保了综合布线的成功。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

546

546

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?