前言

本文为我自己的学习笔记,属于Cadence Virtuoso系列的进阶部分,采用的软件版本是Cadence Virtuoso IC617。其他文章请点击上方,看我制作的Cadence Virtuoso专栏内容。

本文研究的是使用带隙基准产生一个与温度无关的电压基准,用于后面研究的电路。

带隙基准

在实际电路的应用中,一个与温度无关的基准是必不可少的,怎样产生一个与温度无关的量?

理论原理

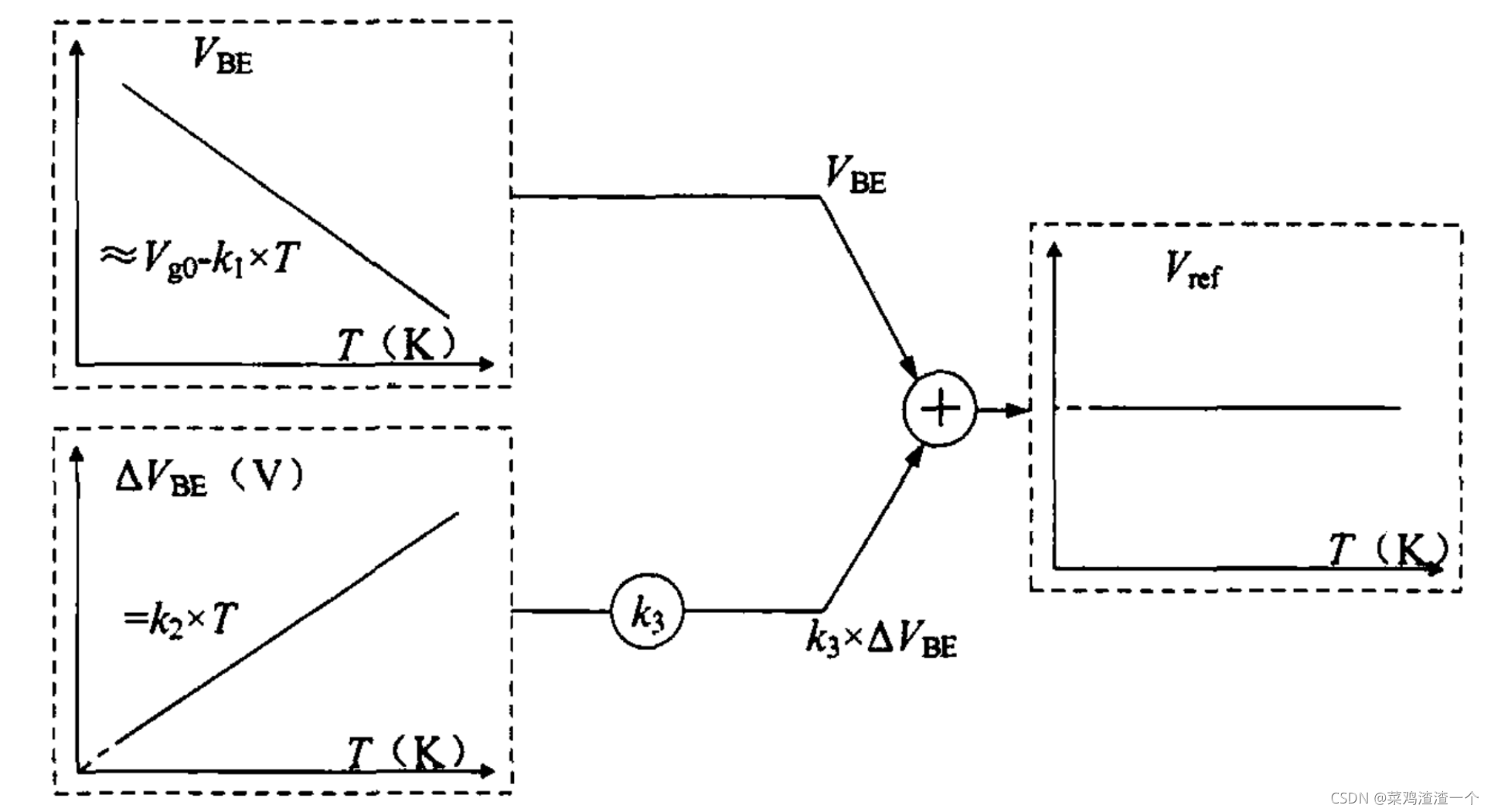

在常见的电子元件中,单一的元件要么是正温度系数,要么是负温度系数,所以,单独使用一种电子元件是无法产生恒定输出的,我们需要做一些改变。

如果一个正温度系数的值与一个负温度系数的值相加,同时给它们一个特定的权重,那么我们就得到了一个零温度系数的值。

电路原理

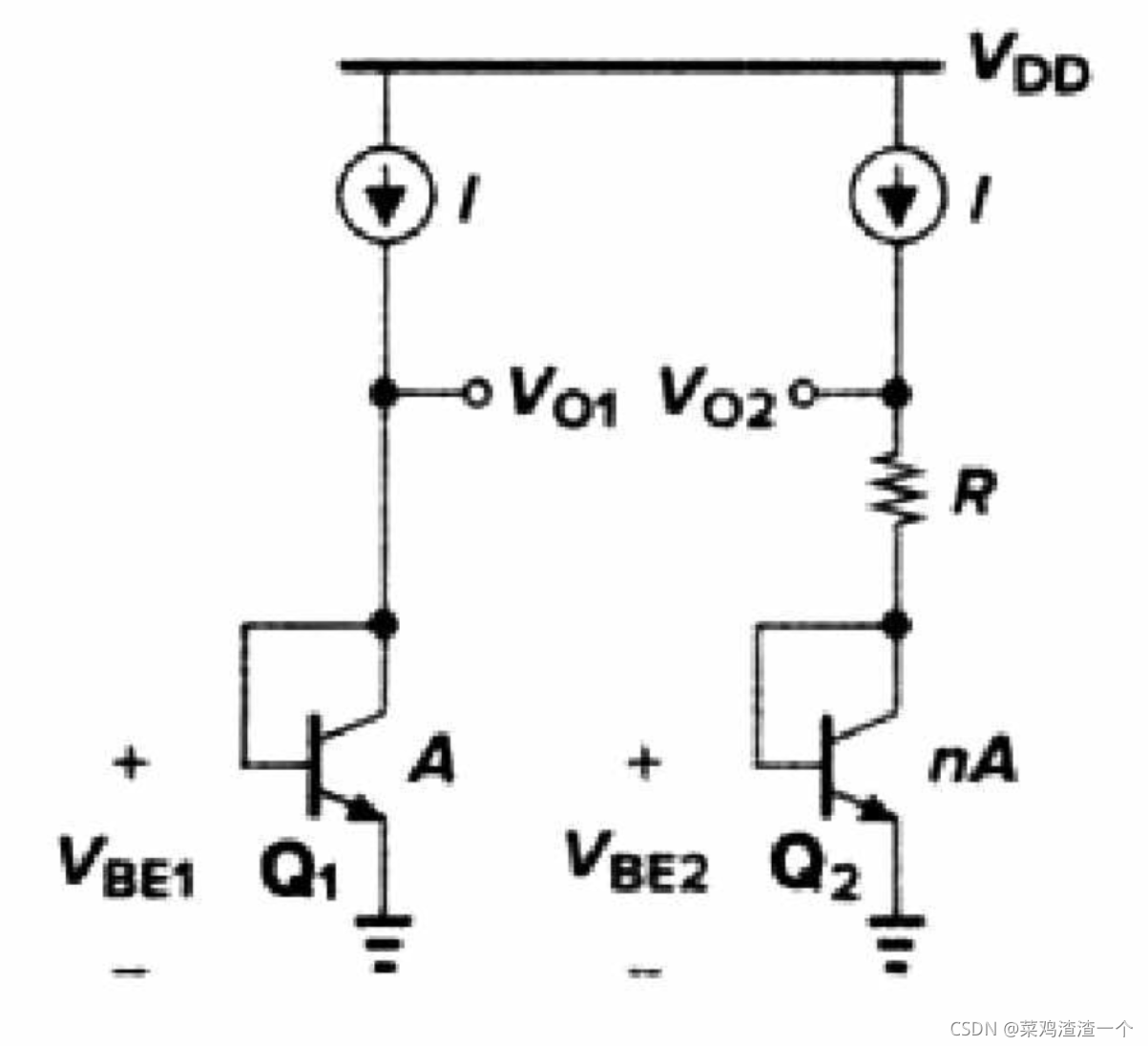

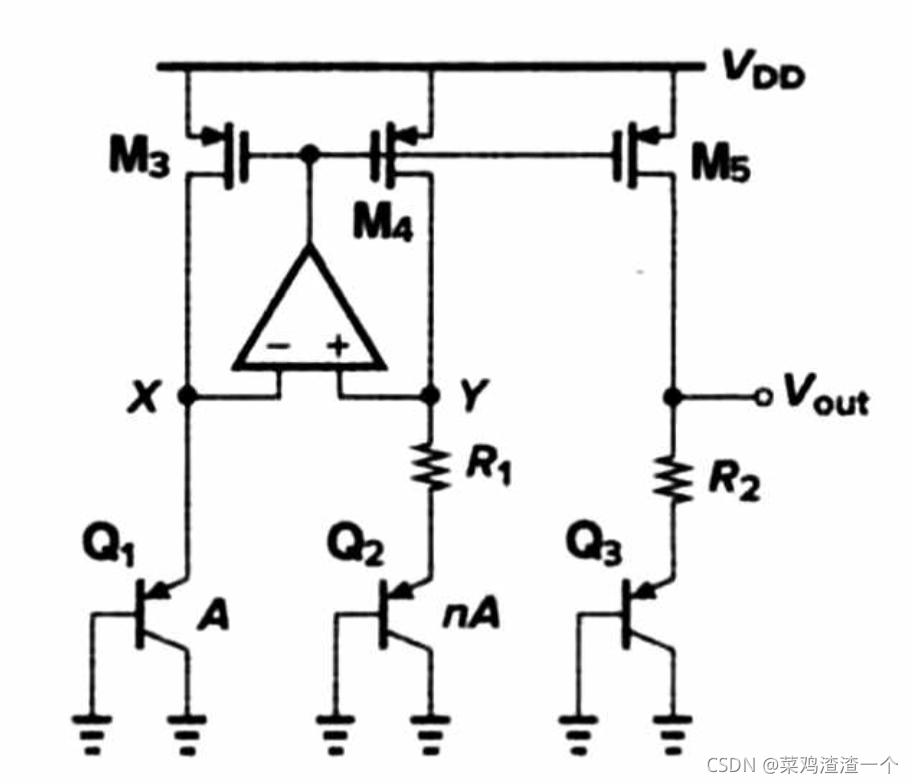

早在上个世纪60年代,有研究者就发现,双极型晶体管的温度系数较好,呈现负温度系数。同时,若给两个双极性晶体管施加不同的电流,它们的电压差值就与绝对温度成正比,呈现正温度系数。利用这两者,就可以产生零温度系数的输出。

两者之间的运算,可以由一个运算放大器实现,这样性能较好,同时,用电流镜来实现电流的复制。

衡量电路的温度性能的参数为温漂,单位为ppm/℃,数量级为10e-6,由以下公式获得。其中,ppm小于20代表电路可用,ppm小于10代表电路性能较好。

V

m

a

x

−

V

m

i

n

V

a

v

g

(

T

m

a

x

−

T

m

i

n

)

×

1

0

6

p

p

m

/

℃

{V_{max}-V_{min} \over V_{avg}(T_{max}-T_{min})}×10^6 \enspace ppm/℃

Vavg(Tmax−Tmin)Vmax−Vmin×106ppm/℃

设计过程

选用SMIC 0.18um工艺。一开始,先要选定PNP三极管的数量。为了版图设计方便,我们一般设计Q1:Q2:Q3的数值为1:7:1,也就是调整晶体管对应的Multiplier数值。这样我们就可以得到一个3*3的PNP三极管阵列版图,其中,Q1将被放置于最中间。

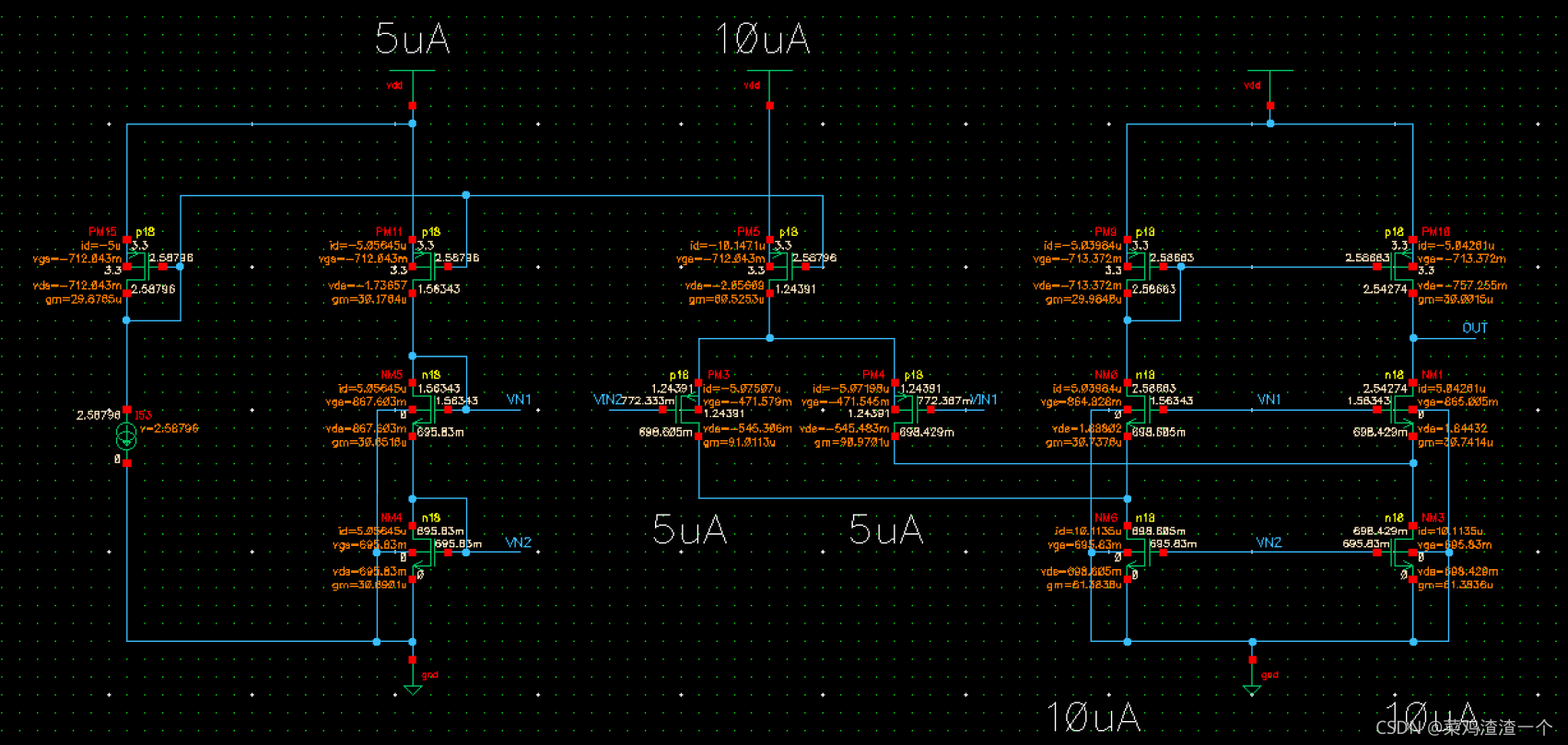

其次,结合功耗需求,确定每条支路的电流。这里我选择每条支路的电流都是10uA。

运放设计

同时,对于运放的选择也有讲究。高增益能提高基准源的精度和电源电压抑制性能,高带宽能提高基准源工作频率的范围,高速的运放可以快速处理串扰使得输出稳定。

但是我们知道,运放的设计其实是一个折中的过程,提高性能所付出的代价就是芯片面积的增加和功耗的增加,我们不希望出现,设计出一个性能较好的基准源但是功耗高达几毫瓦。

在上面提到的几项运放指标中,对于带隙基准源来说,最重要的是运放的增益,我们只需要增加一些输入晶体管的面积(主要是增加栅长L),而不需要增加太多功耗,就能得到一个高增益的运放,这样还是比较划算的。

使用了一个折叠共源共栅运放,其中输入管的gm/id=18,其它晶体管的gm/id=6。电流镜的栅长L=4um。设计的Av约为58dB,在4.8pF的负载下,GBW=3MHz。其他的就不再赘述设计过程了。

确定P-MOS尺寸

原理图中有三个P-MOS,它们所在支路的电流被设计成一样的10uA,所以它们的尺寸可以设计成相等的。通过gm/id设计方法,同时减小噪声干扰,取gm/id=6,抑制沟道长度调制效应,取L=2um,由对应的id/W数值直接得出W。取值结果如下。

| P-MOS | |

|---|---|

| W | 5.57u |

| L | 2u |

| Multiplier | 1 |

确定R1

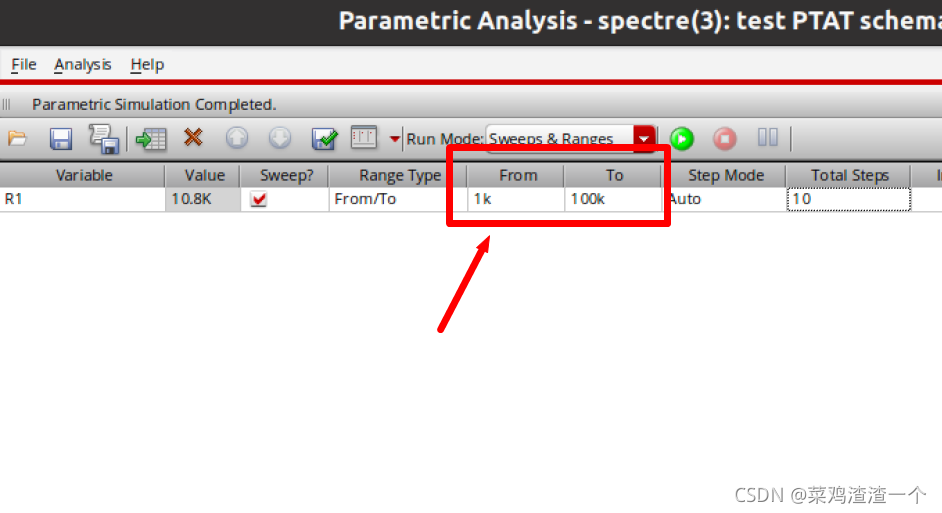

R1主要决定支路的电流,我们的目标是设计支路电流为10uA。选择参数扫描,扫描R1的范围为1K到100K,取10个点。

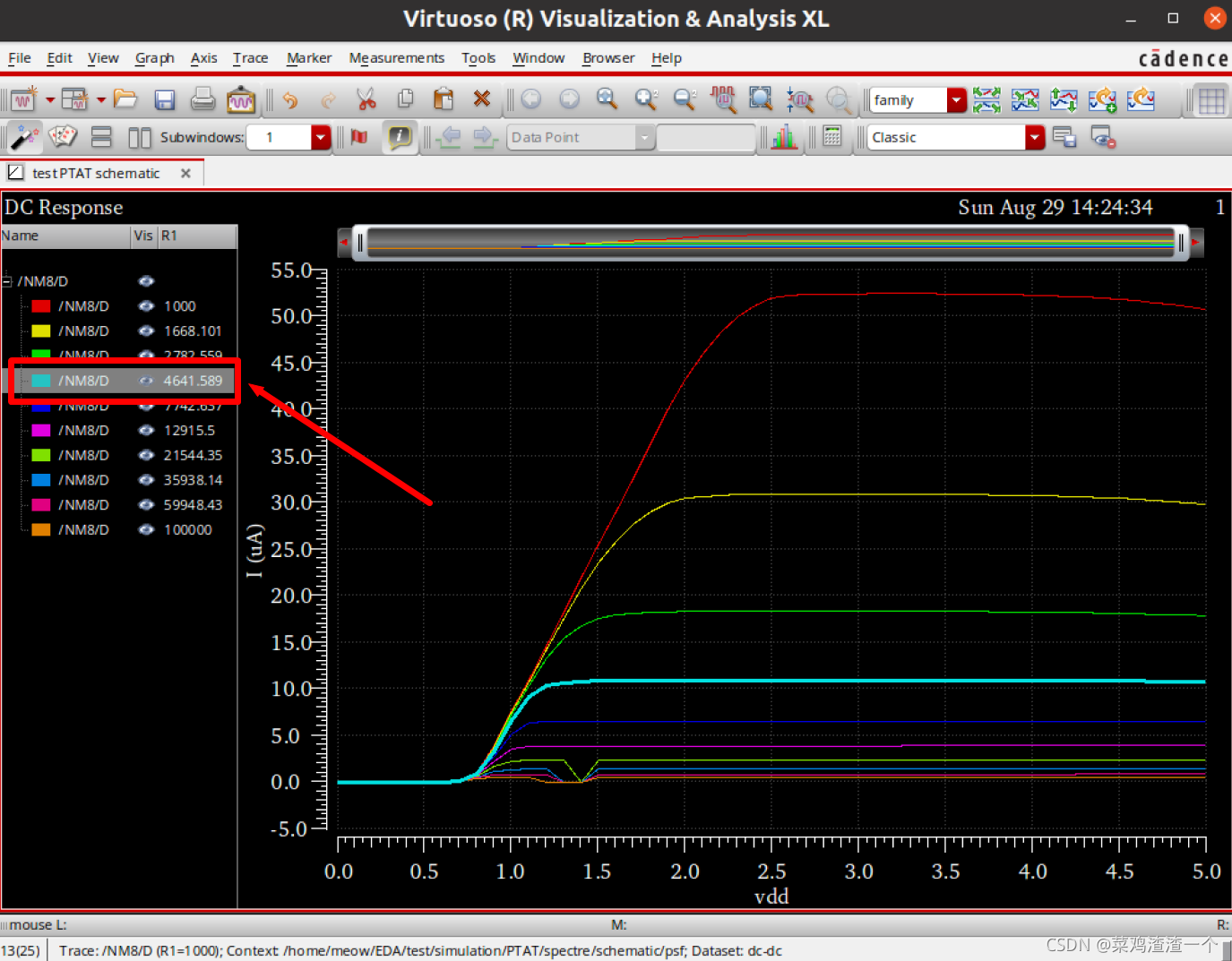

得到输出电流和R1电阻的关系,这里我们确定R1的范围在4.6K附近。

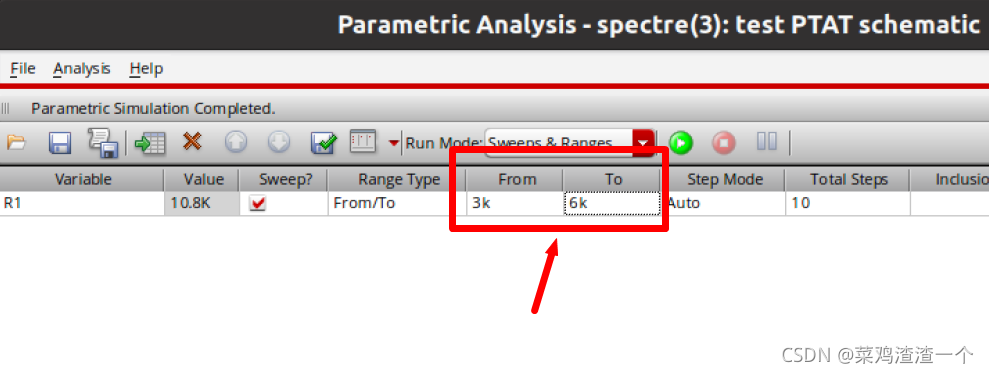

修改扫描范围为3K到6K,逐次逼近。

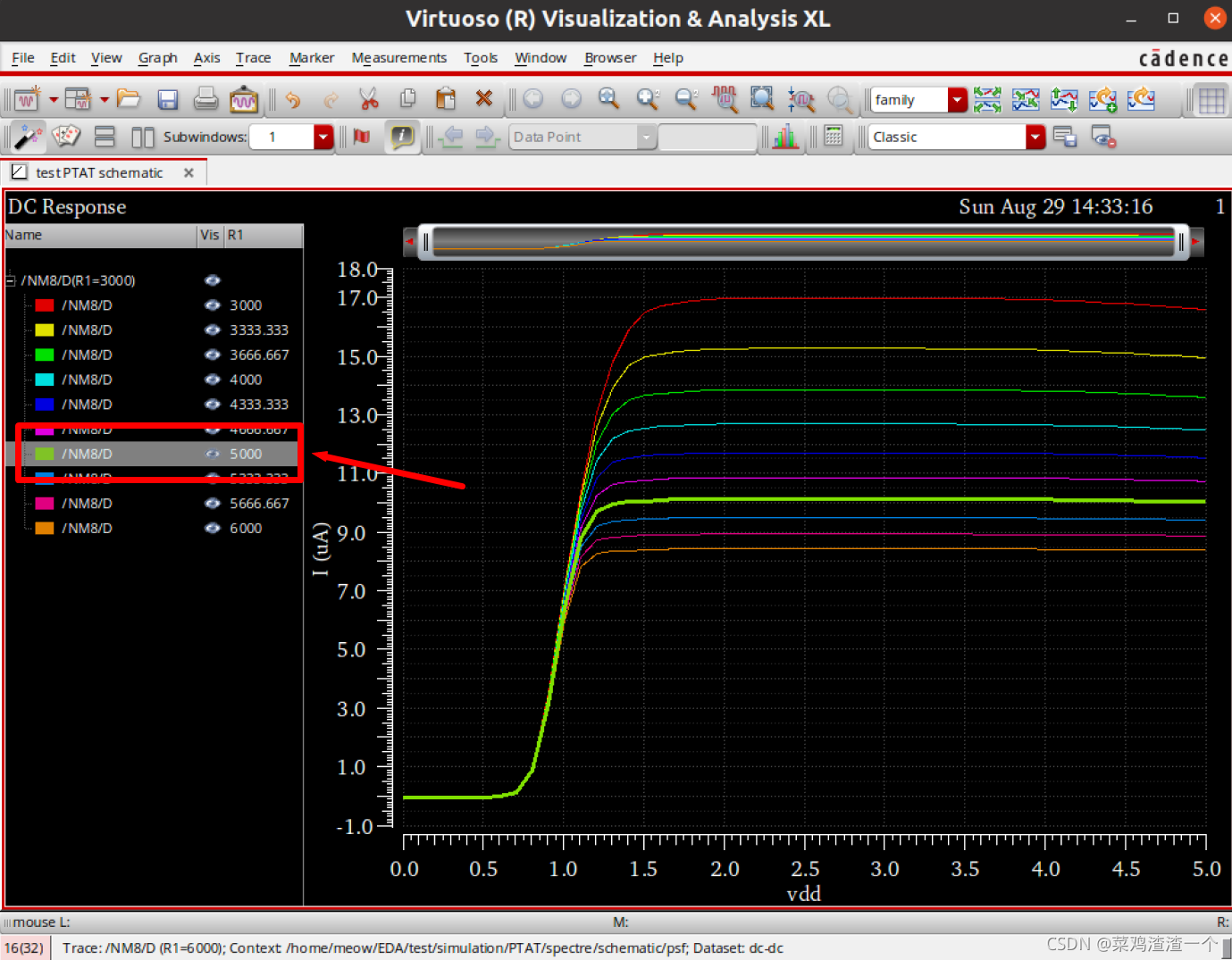

范围大概是5K附近。不停重复以上步骤,最终得到,当支路电流为10uA时,R1=5.056K。

确定R2

电阻R2主要确定电路的温度系数,因为这个时候输出电压是肯定不随电源电压变化了的,就不再扫描了,感兴趣的可以自己验证一下。

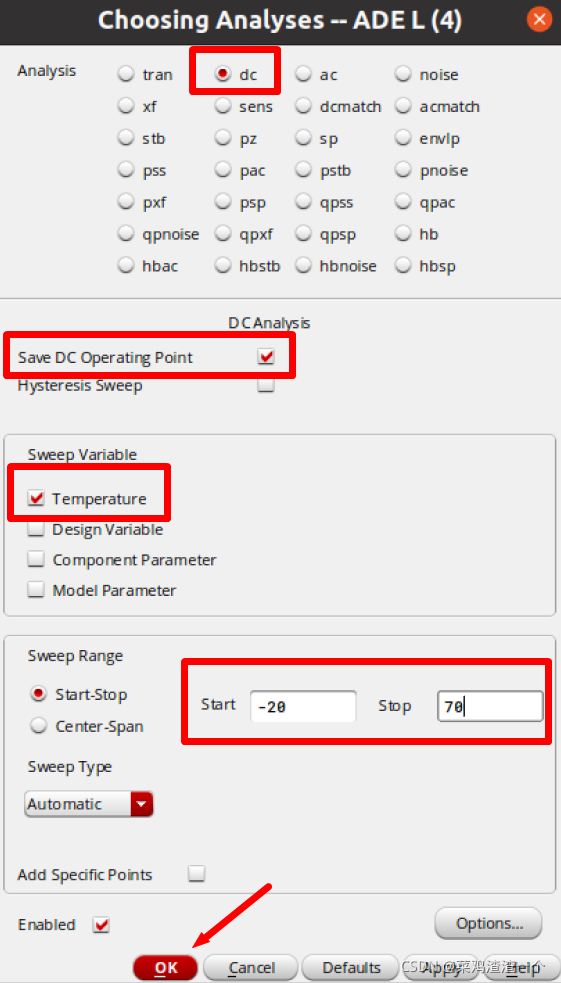

将扫描设置成DC扫描,扫描值为温度。

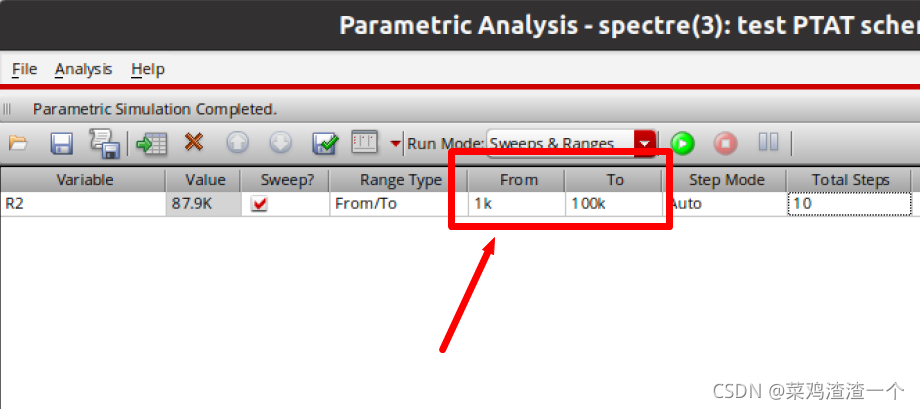

和上面一样,扫描参数为R2。

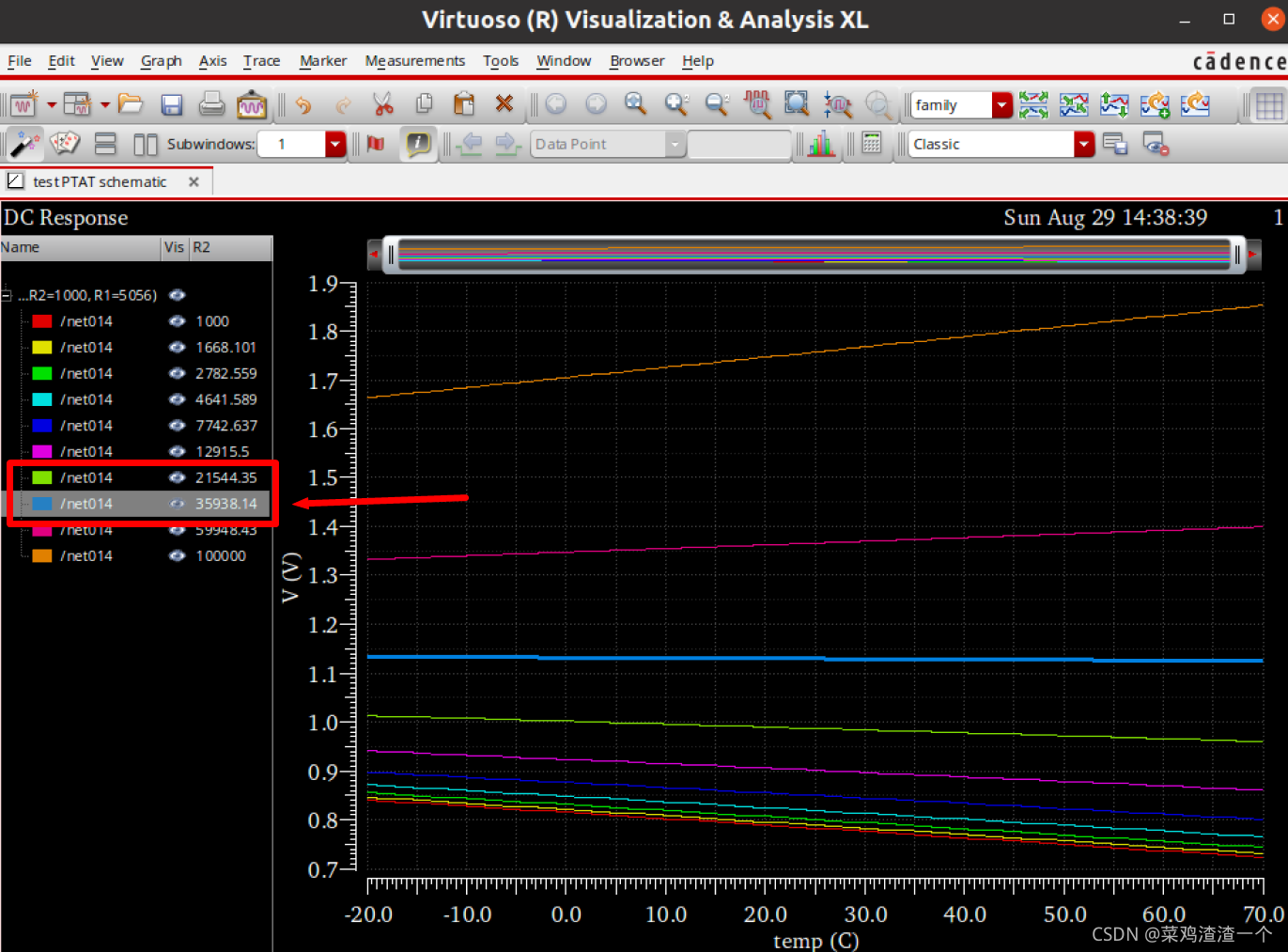

得到R2的大概范围。

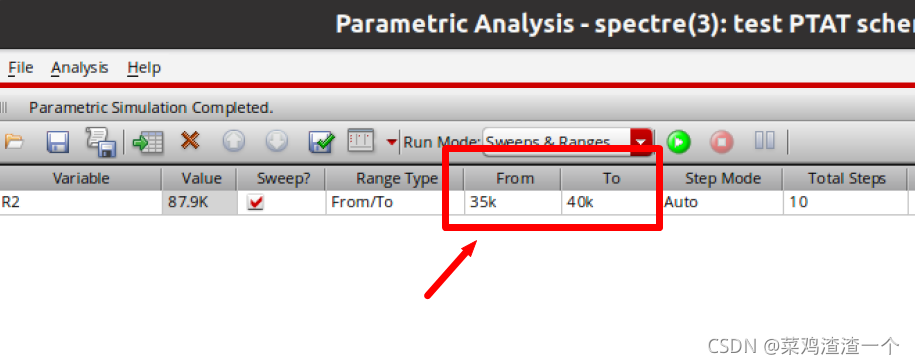

缩小扫描范围,逐次逼近。

得到R2大约为38.5K。最终得到R1=38.7K。

仿真结果

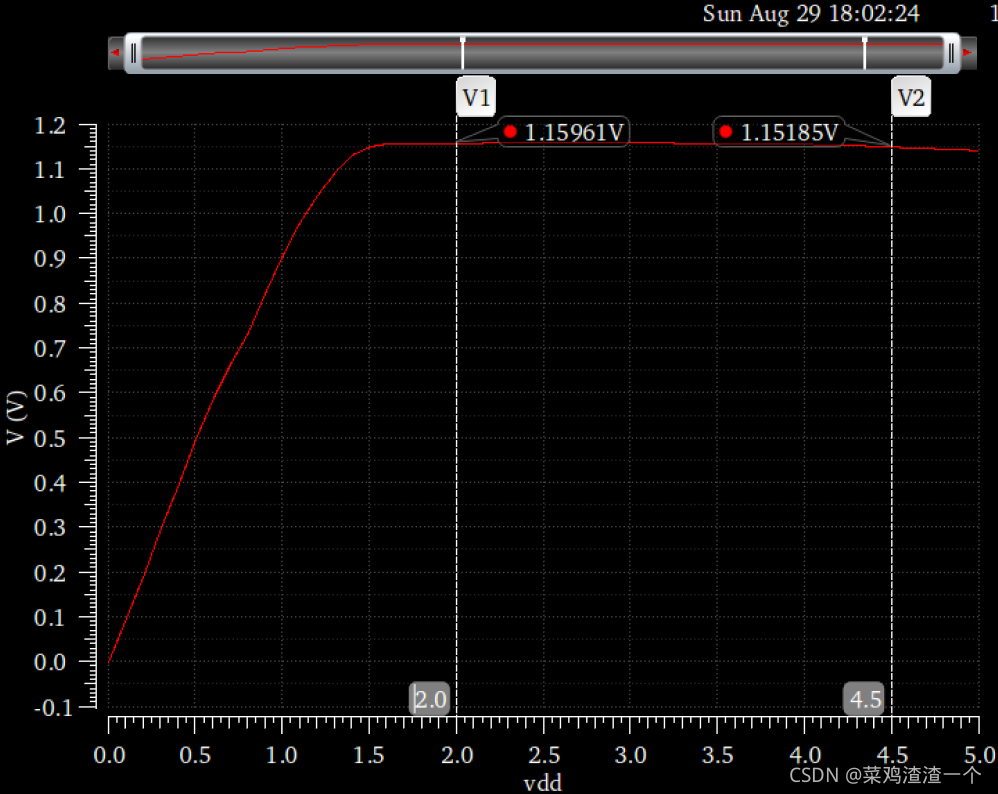

将前面得到的数值写入电路参数里,仿真电路。仿真电源特性,在2V到4.5V范围内,可以看出最大值和最小值偏差率约0.67%。这个电路有一个缺点,就是在曲线后半段,VDD较大时,输出曲线反而有下降的趋势。

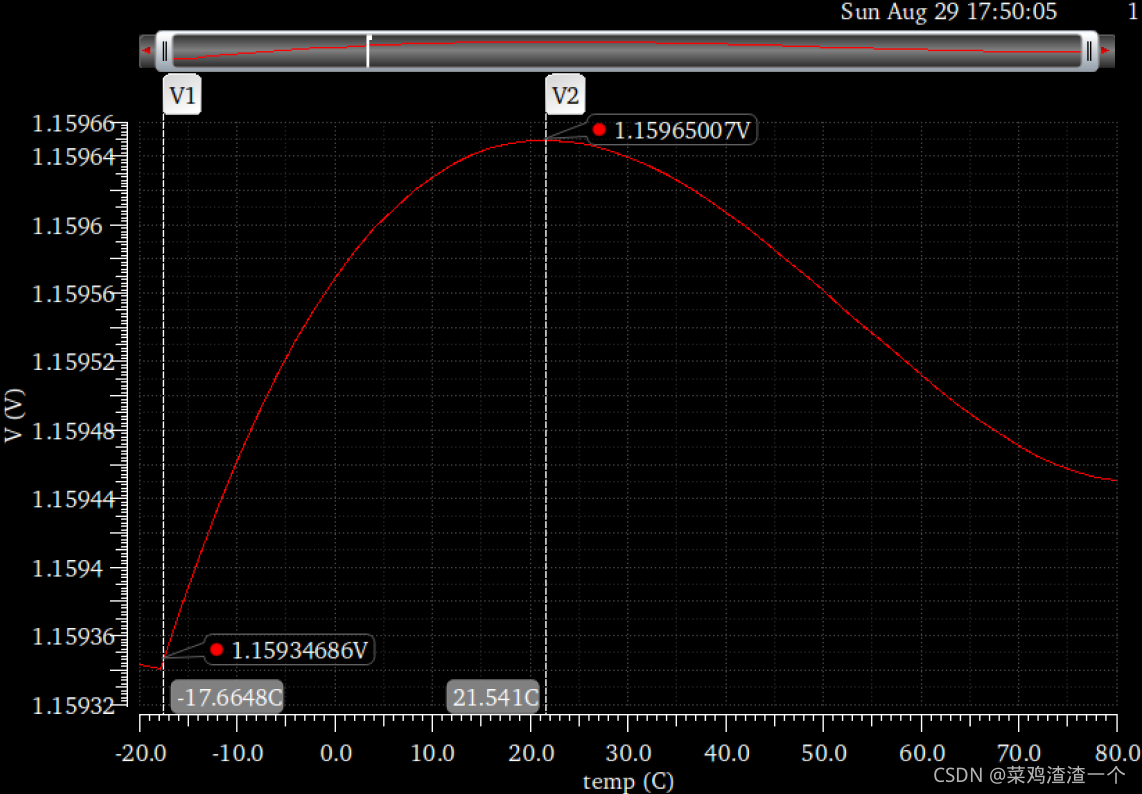

仿真温度特性。其中平均电压Vavg约是1.1595V,得到温漂为2.6ppm,性能较好。注意,画版图的后仿真后,此值会变差,所以版图的匹配也很重要。

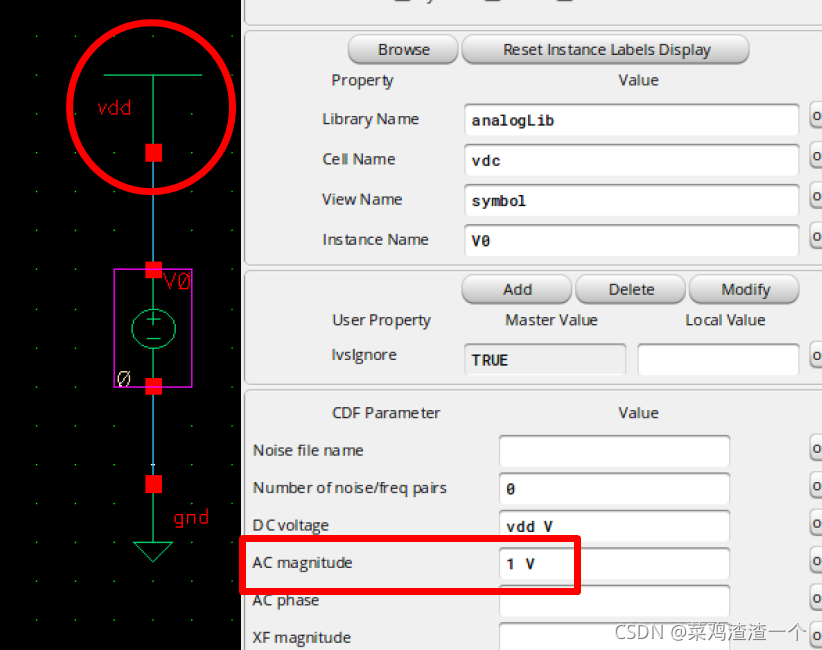

下面说说怎样查看电源抑制比。首先,在控制VDD的直流电压源处,添加一个1V的AC信号。

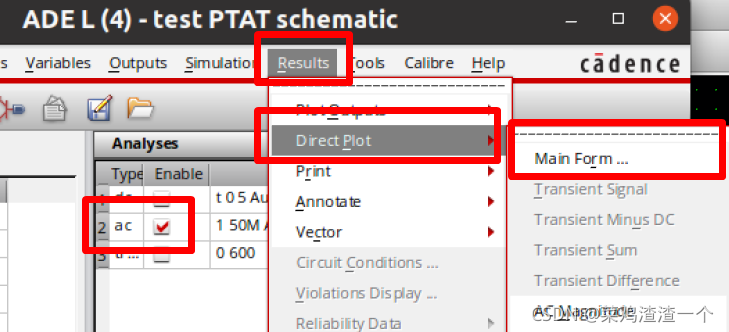

添加AC扫描后,点击仿真,在结果出来后,选择结果输出。

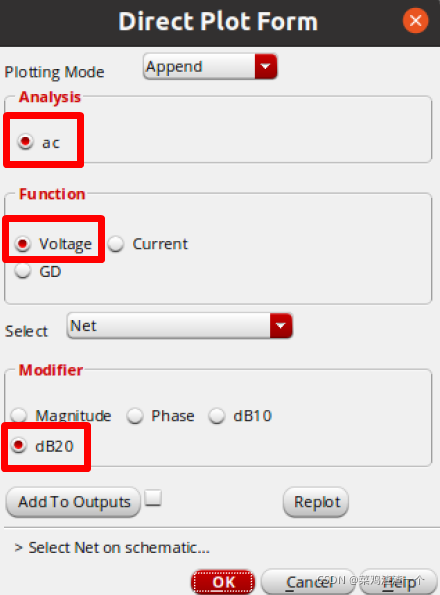

按照如下选择。之后用鼠标点击基准电压输出的连接线。

得到电源抑制比接近60dB,其性能大致为所设计的运放的增益。当然,这个指标并不够好,一般在100dB及以上才算优秀。

启动电路

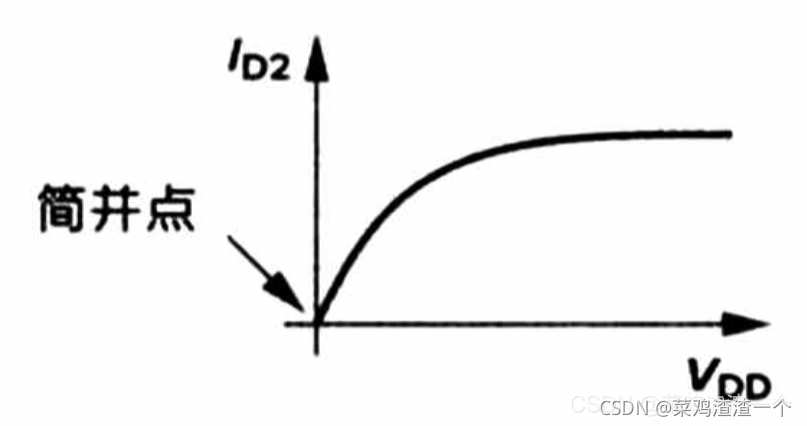

和上一篇文章中提到的电流基准源一样,在VDD上电时会存在一个简并点。所以需要引入一个启动电路。

这部分后面再补充吧,如果是用于仿真验证书中的原理,就不太需要这部分,如果是要流片,就得加入这部分。

6653

6653

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?