前言

从Vivado 2020开始,赛灵思发布了全新的Vitis IDE组件,用于代替Xilinx SDK,它们之间的操作稍微有些不同,但都是基于Eclipse套个马甲而来。

本文将使用Vivado 2021和Vitis IDE 2021,进行简单串口实验,将打印hello world。本文将只使用PS外设,而不使用PL外设。部分Vivado的操作过程将省略,具体和详细的Vivado的操作请看上一篇文章。

Vivado部分

建立工程

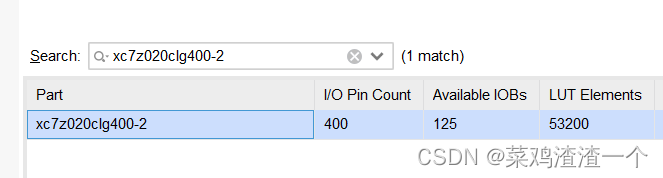

建立好Vivado空白工程即可,也不需要XDC文件。我这里使用的是xc7z020clg400-2器件。

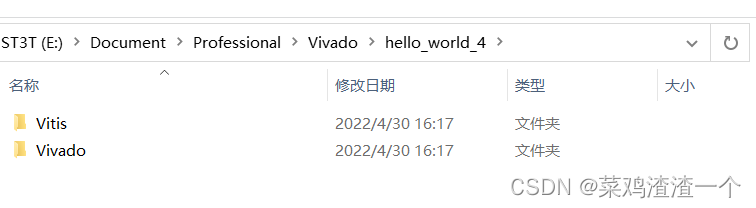

建议在工程目录按软件名分开,因为这个过程需要两个软件都生成工程文件,容易弄混。

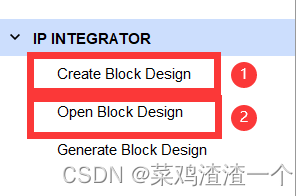

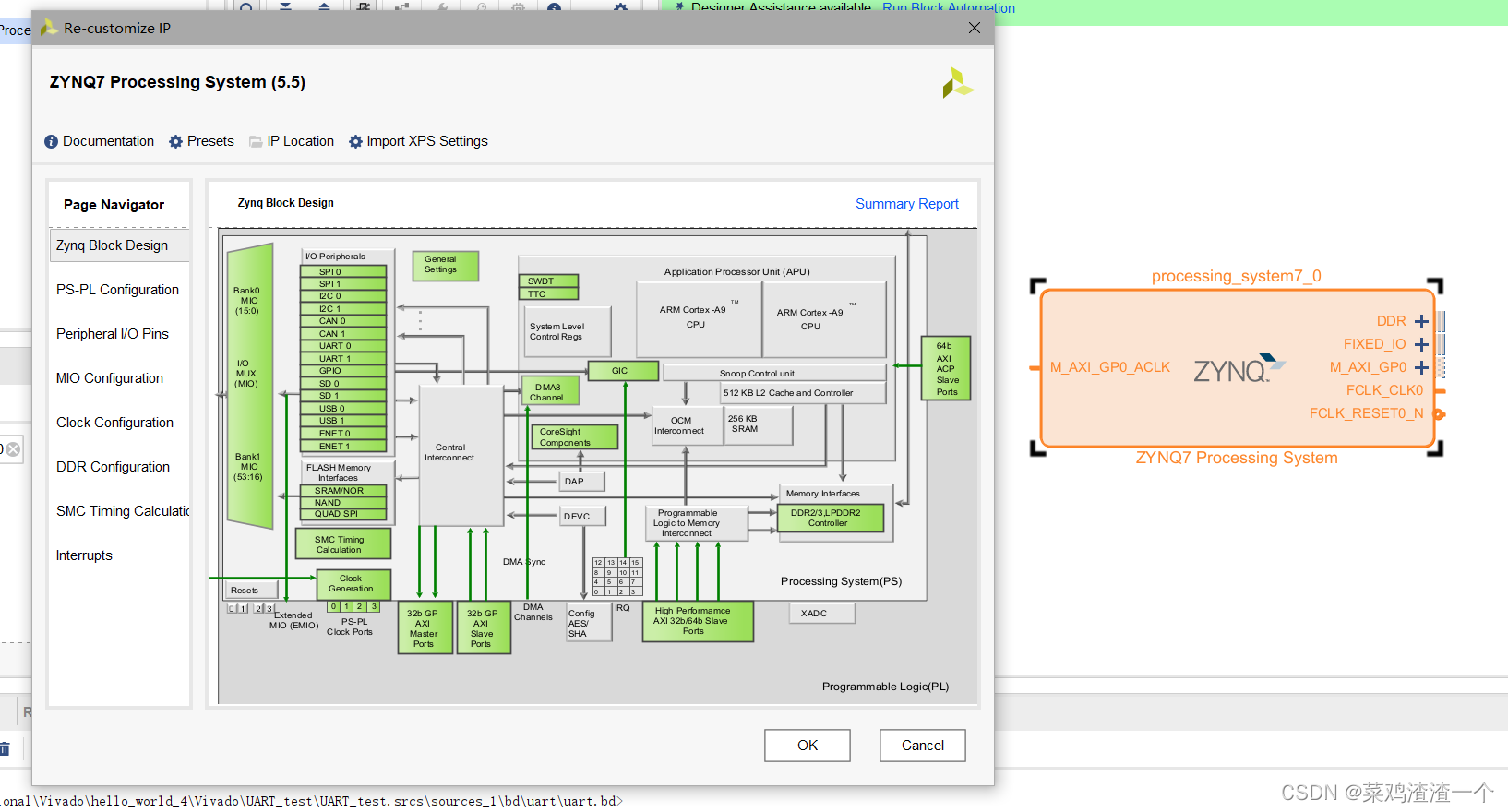

新建一个原理图,并打开。

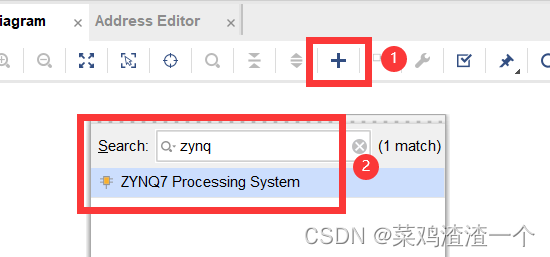

在原理图编辑中添加一个PS内核。

修改内核

双击添加进来的内核,对它进行修改。

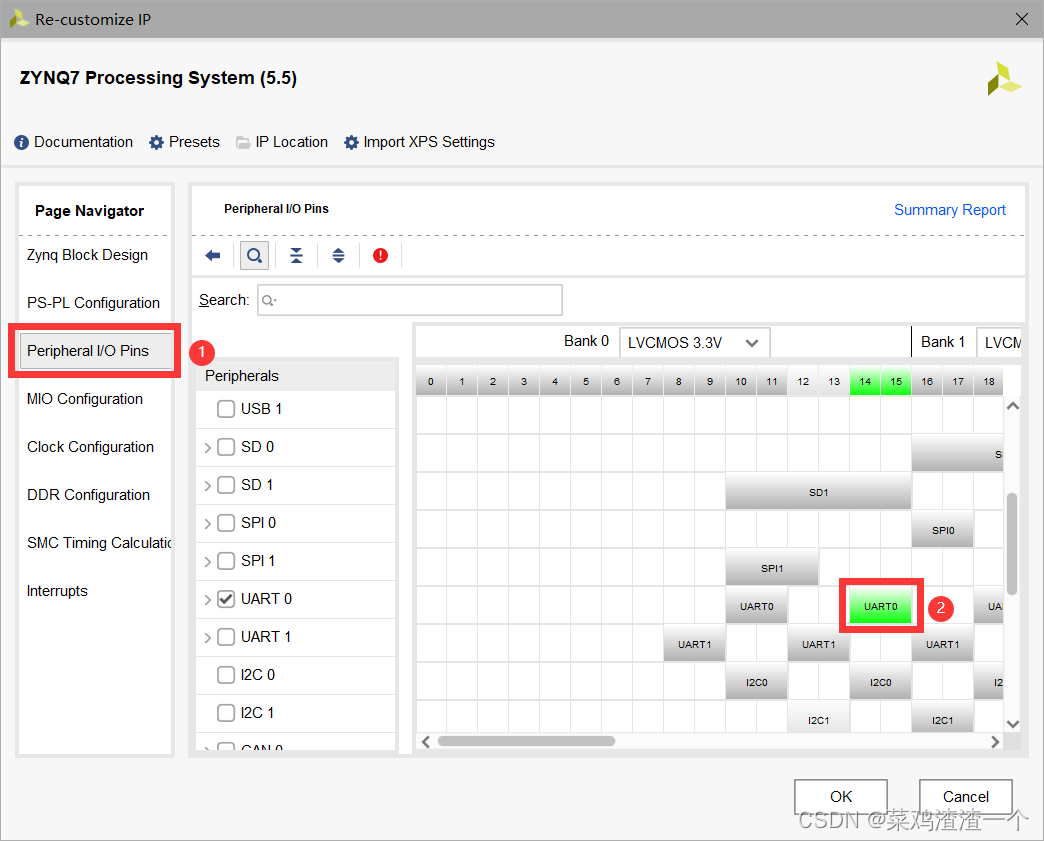

串口设置

查看自己开发板的原理图,可以知道它的USB转串口芯片(CH340)连接到了14和15两个管脚上,点红色框中的按钮,将UART0变成绿色。

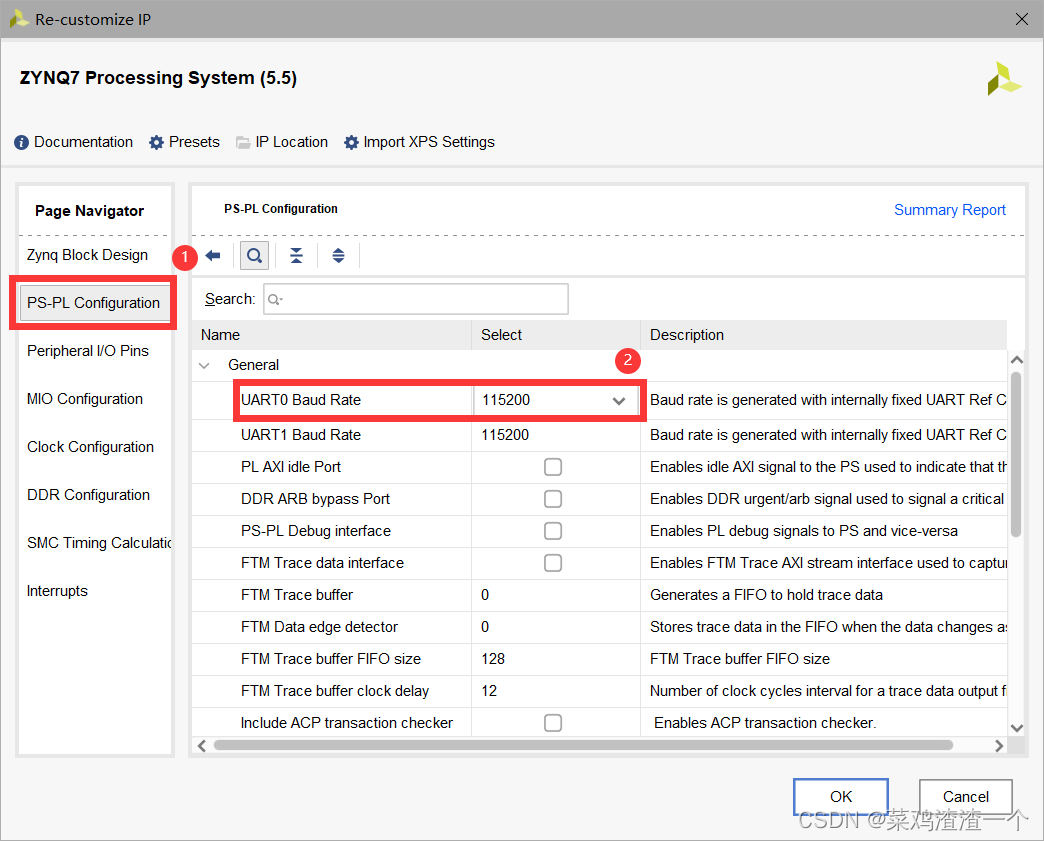

查看串口的波特率,并结合实际情况进行修改,这里保持默认的115200即可。

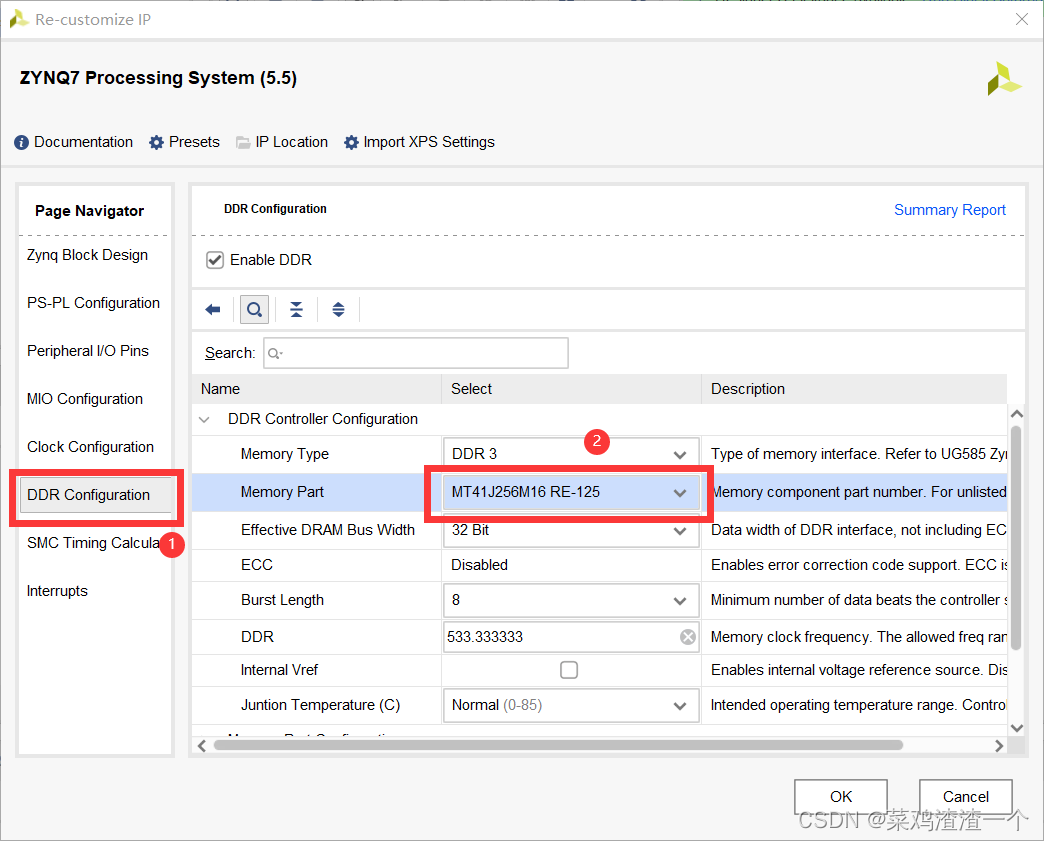

配置DDR

结合自己开发板的情况,选择内存型号。

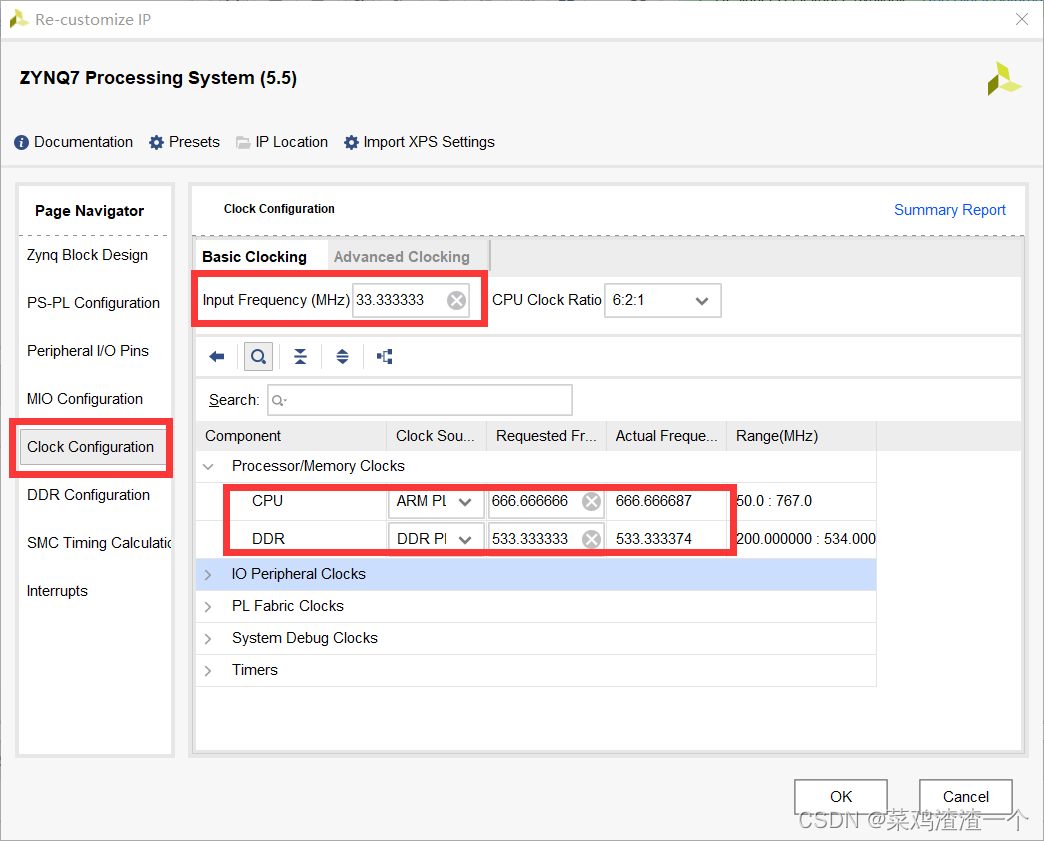

配置时钟频率

结合自己的使用和应用情况,我这里也保持默认。

移除PS和PL交互接口(可选)

这里就根据自己的实际情况了。如果需要使用到PL的外设,这一步就不需要做。

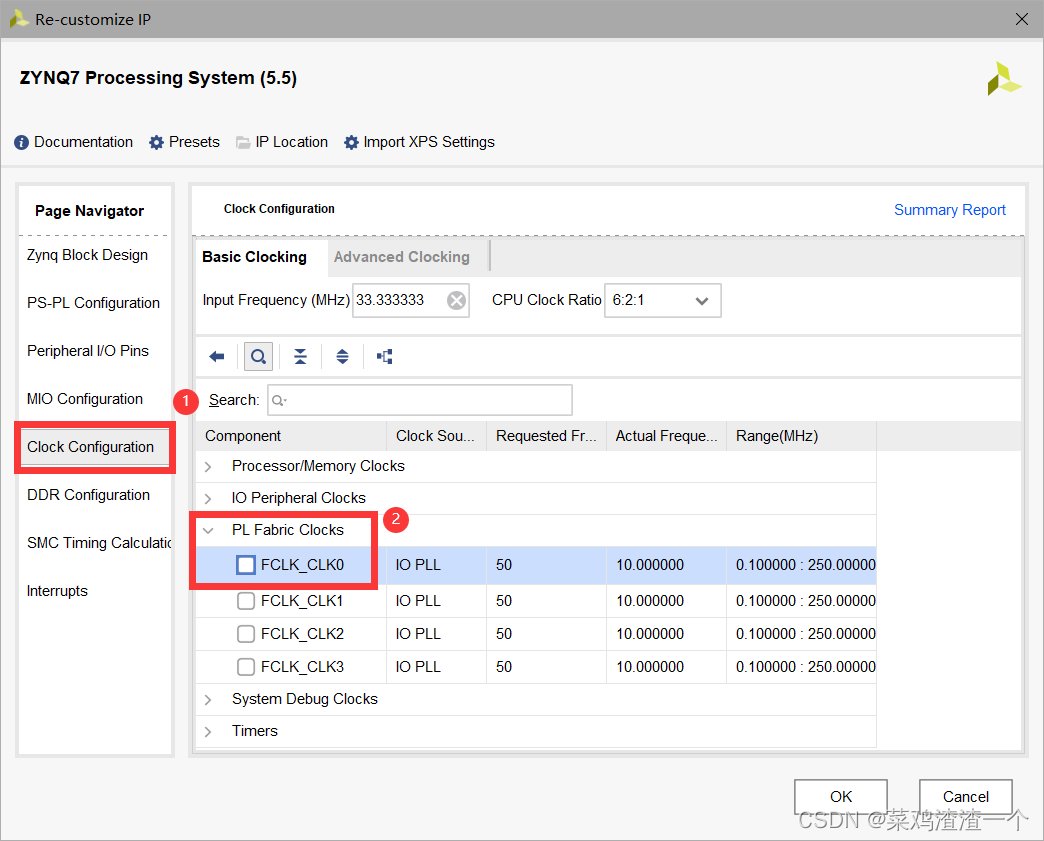

FCLK_CLK0

取消勾选FCLK_CLK0。

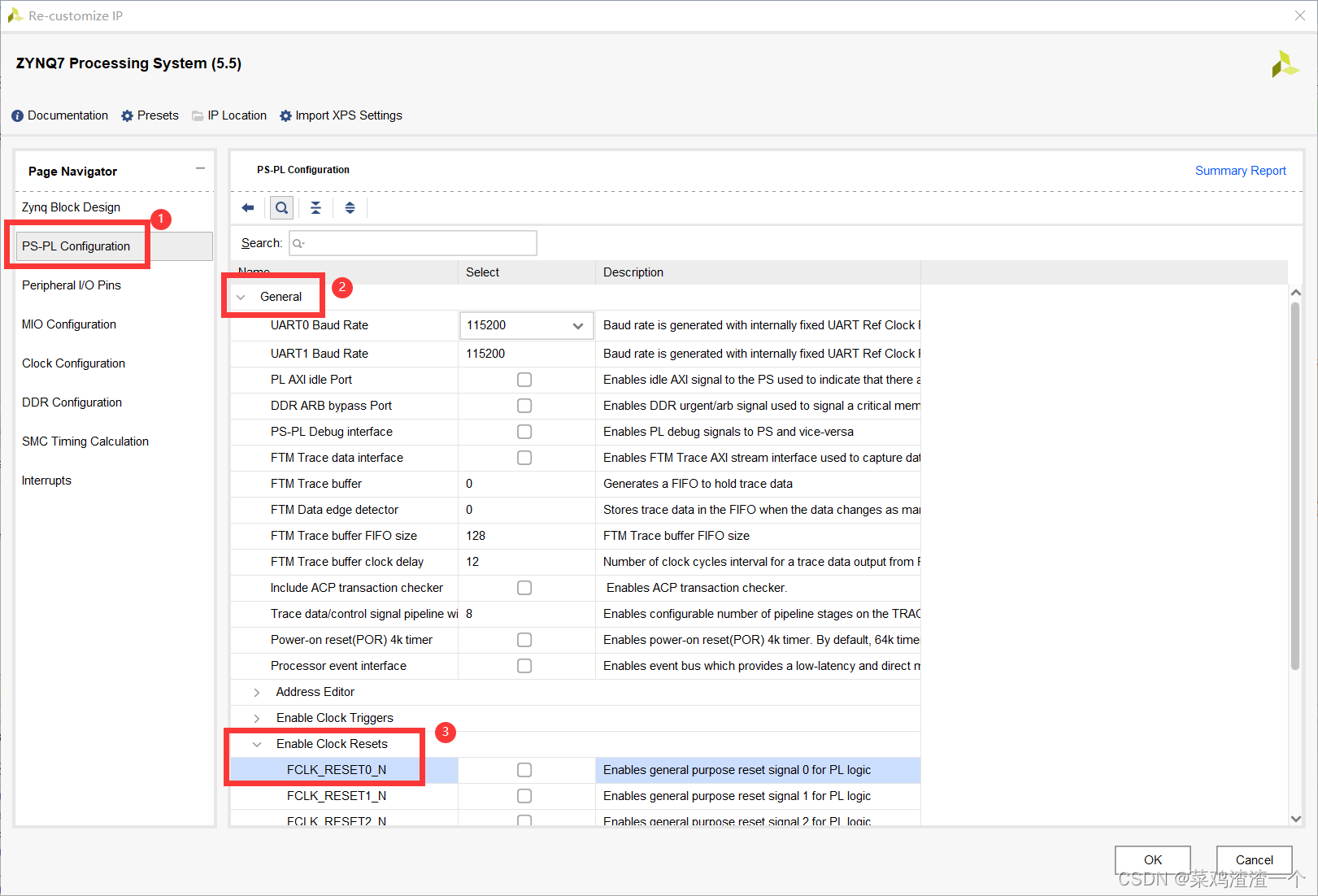

FCLK_RESET0_N

取消勾选FCLK_RESET0_N。

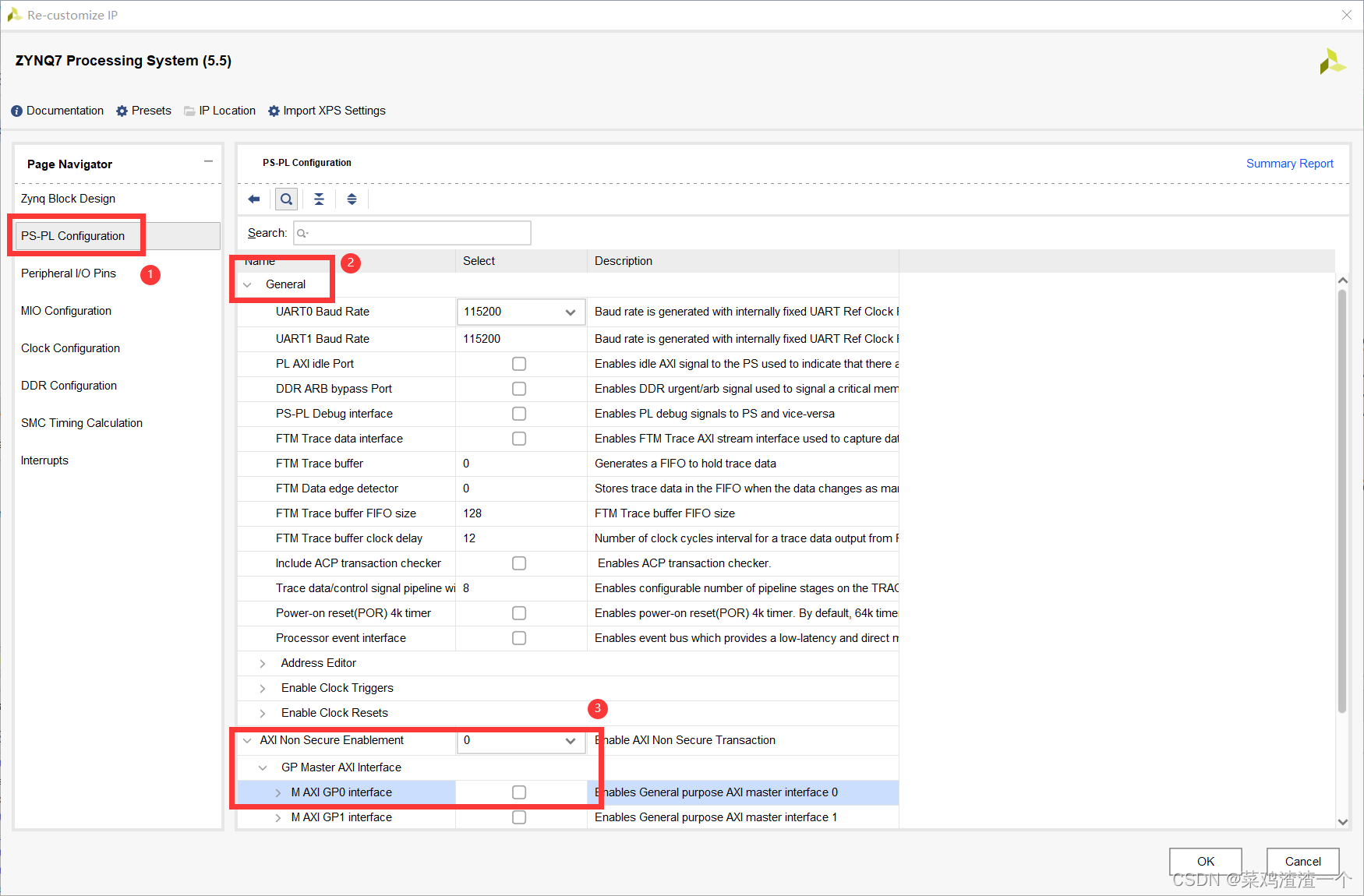

MAXI GP0 interface

取消勾选MAXI GP0 interface。

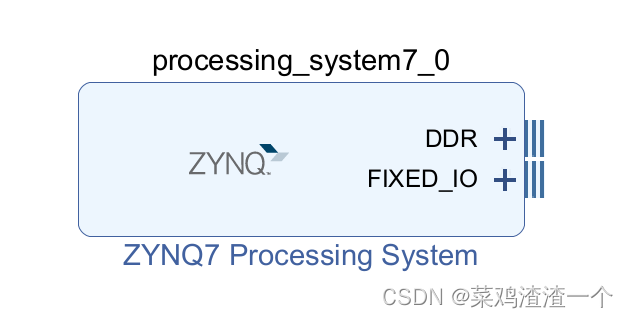

最终内核

移除了交互接口后,整个内核就变得简单了。

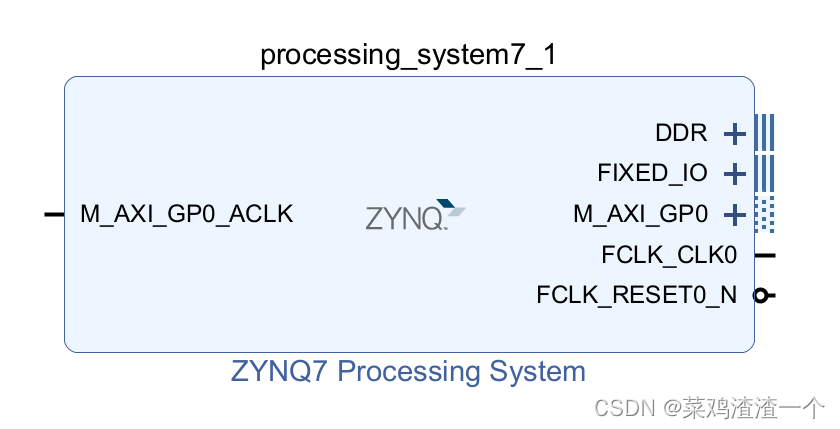

如果没有移除有关交互接口,则是正常的样子。

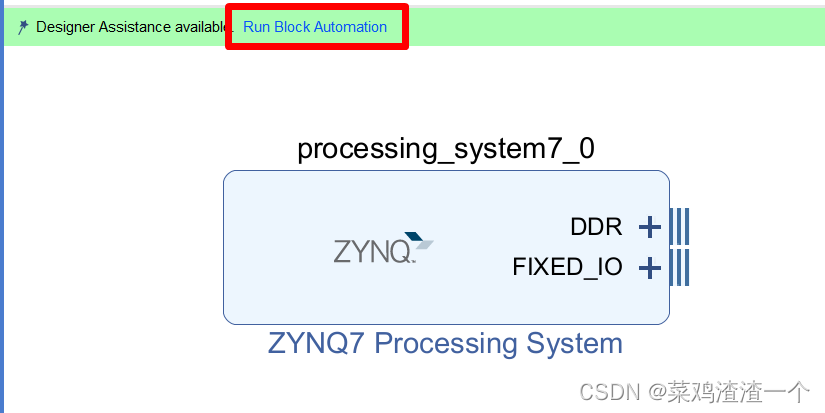

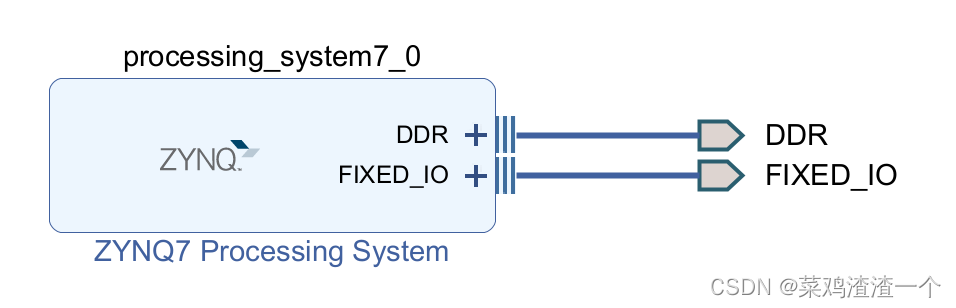

绘制原理图并检查

选择自动即可。

就会得到连好线的原理图。

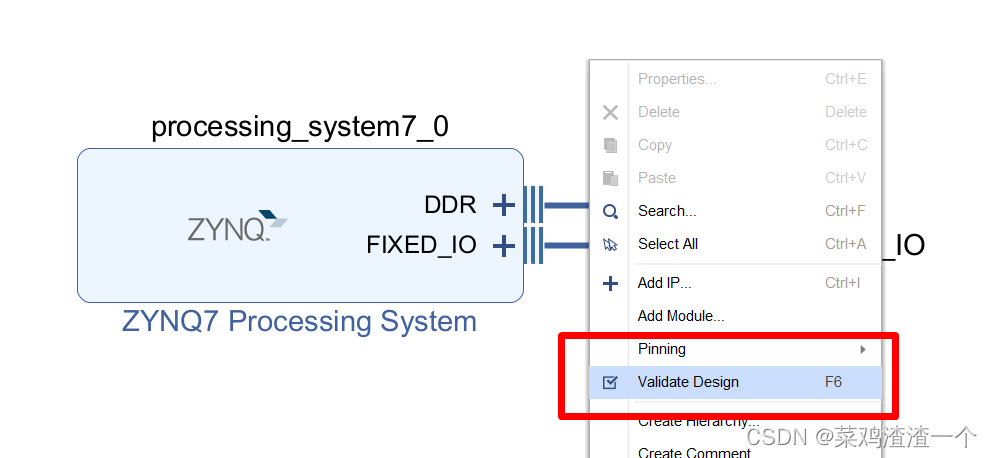

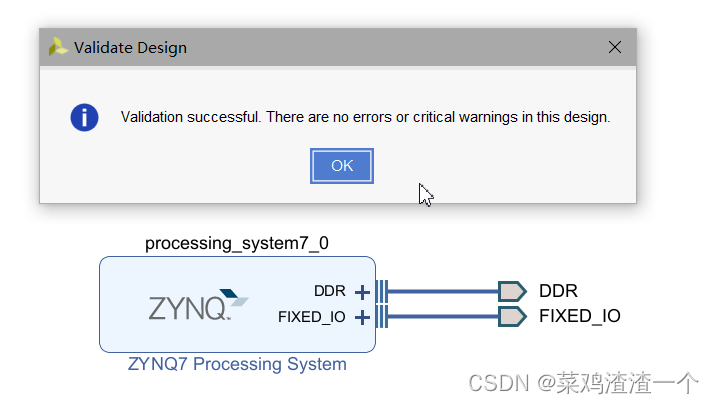

检查设计有没有出错。

没有任何报错。

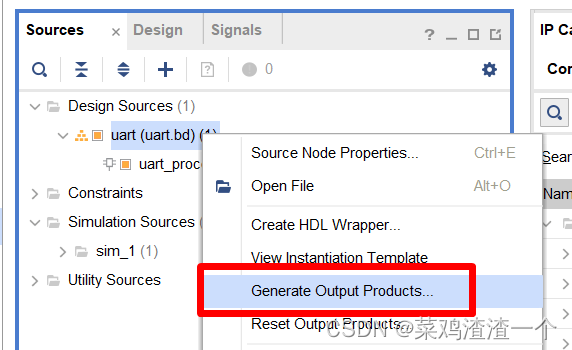

综合原理图

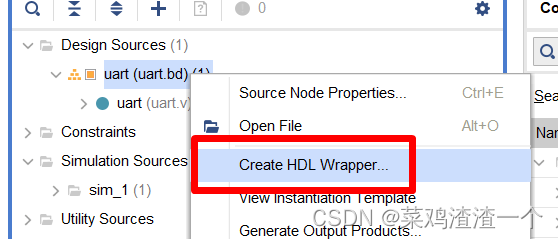

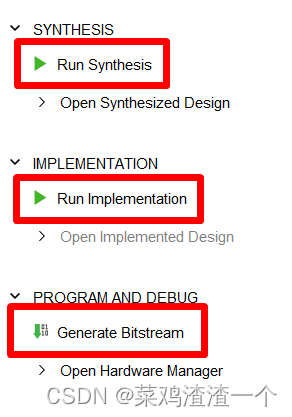

按下图顺序即可,这里省略过程文字。

创建顶层文件。

综合并生成比特流(可选)

如果使用了PL外设,就需要生成比特流。

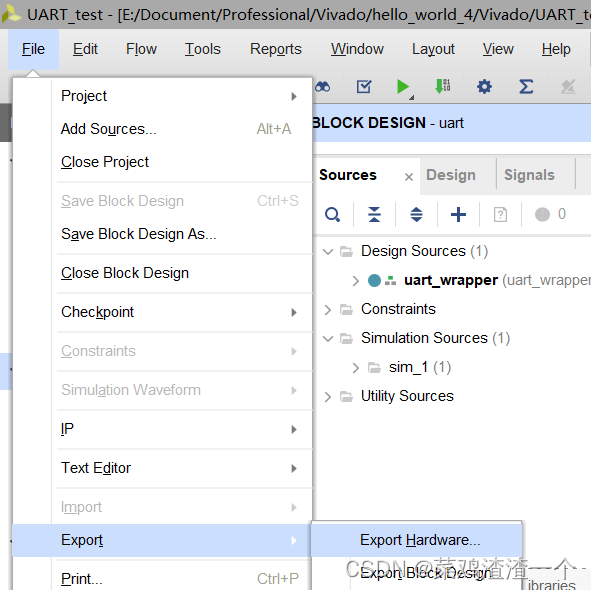

导出内核

在File中选择导出。

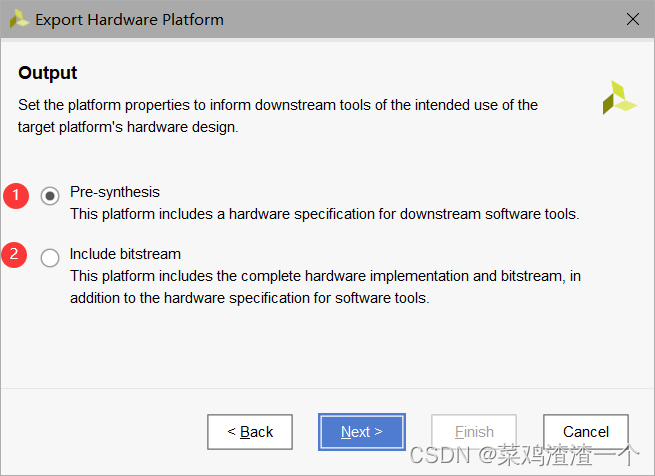

只使用PS内核,选择1即可。使用了PL内核,要选择2。导出到默认路径即可,即工程源目录。

Vitis IDE部分

建立工程

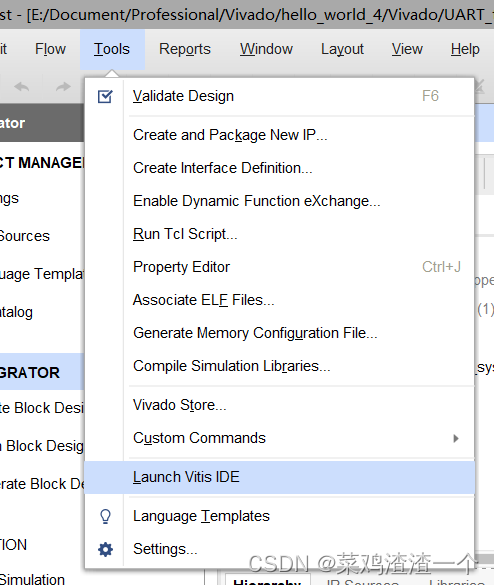

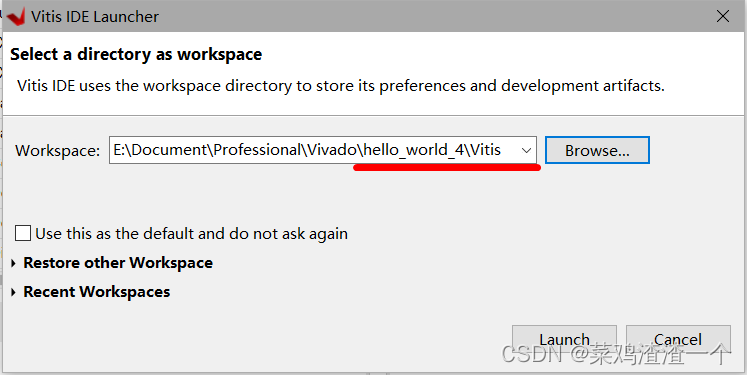

打开Vitis IDE,可以点图标打开,也可以在Vivado里打开。

选择刚刚按照软件名创建的文件夹。

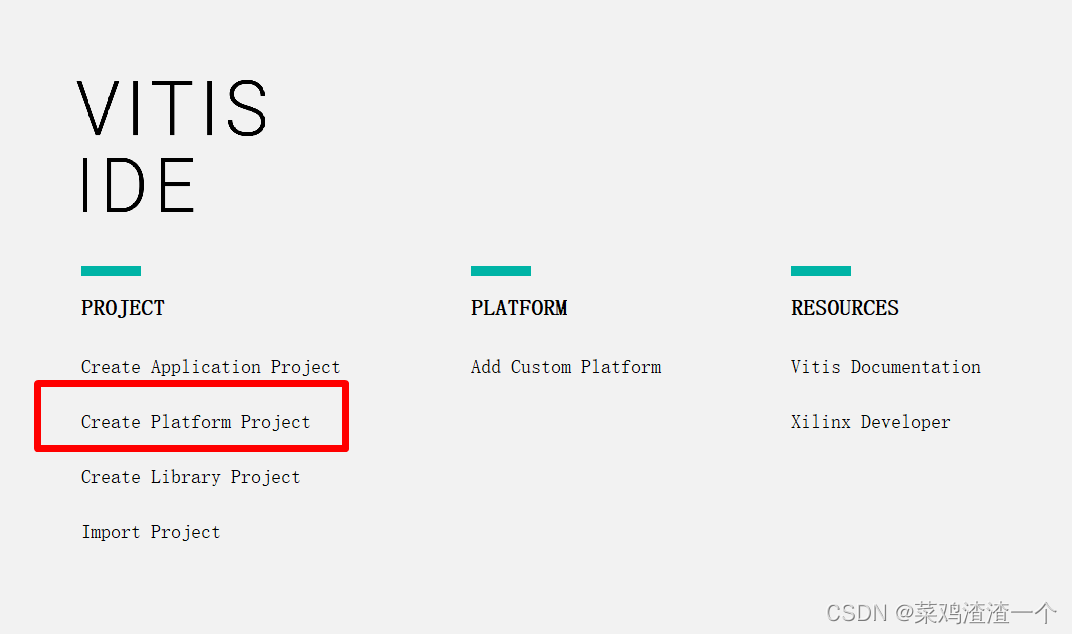

建立Platform工程

设置名字。

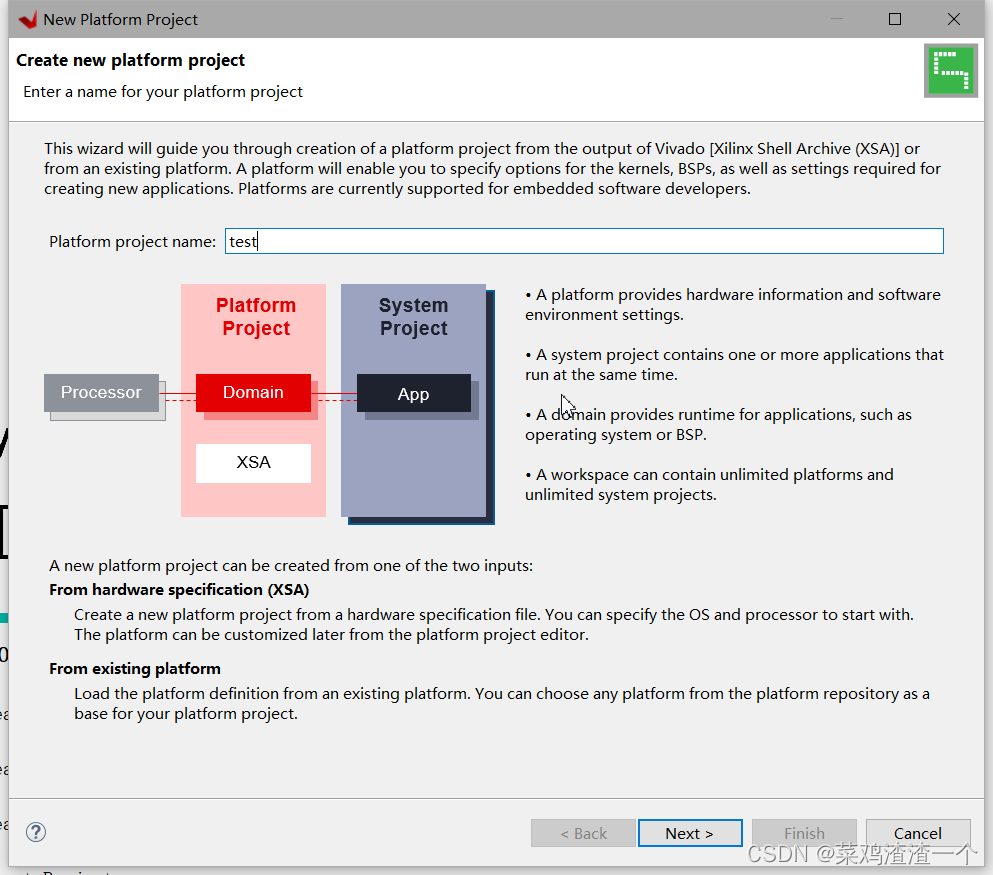

选择刚刚导出的内核。选择xsa文件。其他默认下一步即可。

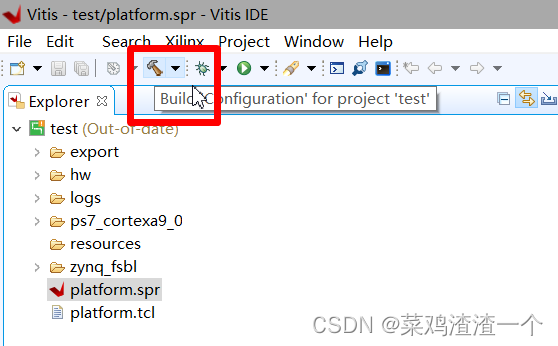

进来了先build一下工程。

建立Application工程

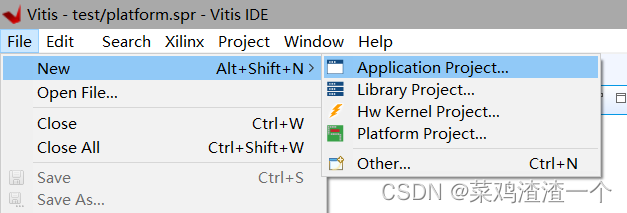

在File里可以直接新建。

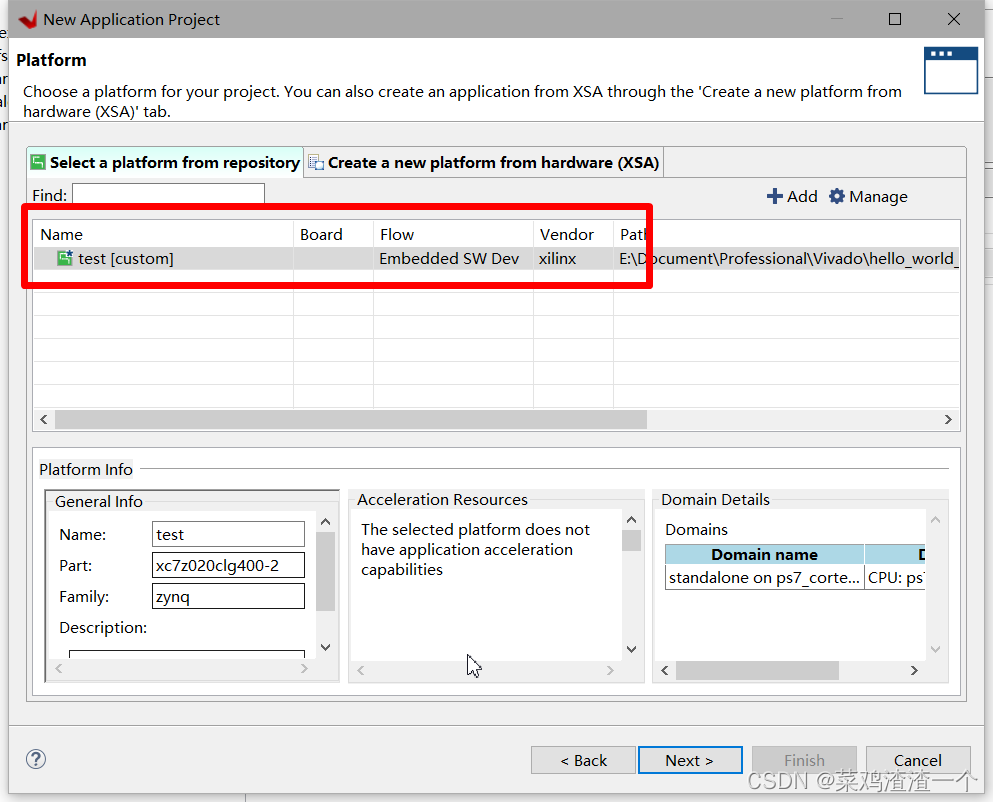

这里会出现Platform工程中产生的文件。

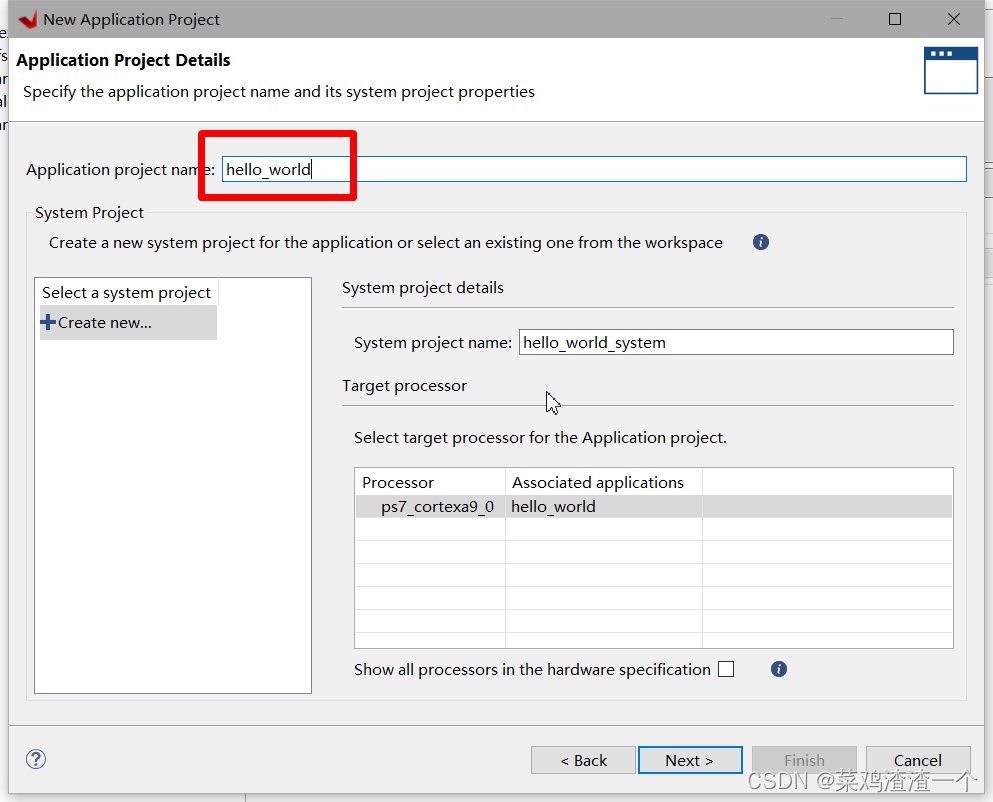

设置工程名。

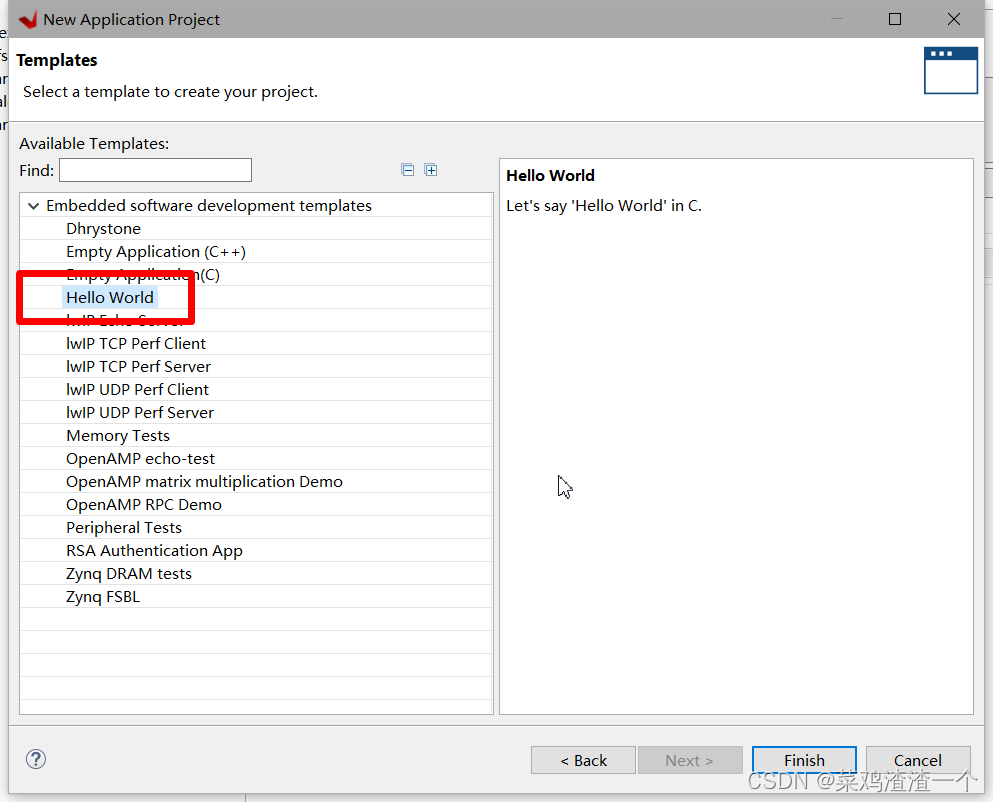

以Hello World为模板建立工程。

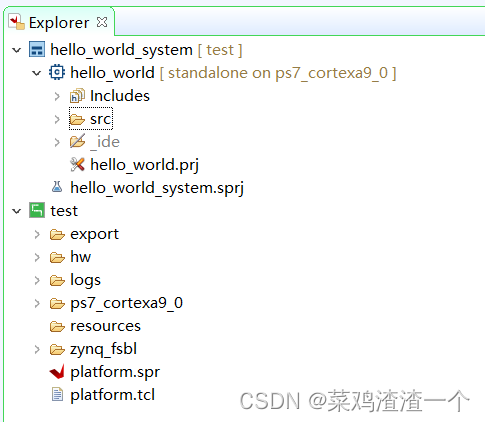

结果

自此,工程就建立完成了。以下是工程目录。

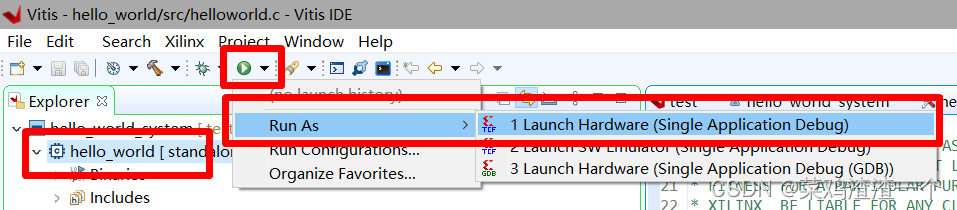

编译并下载

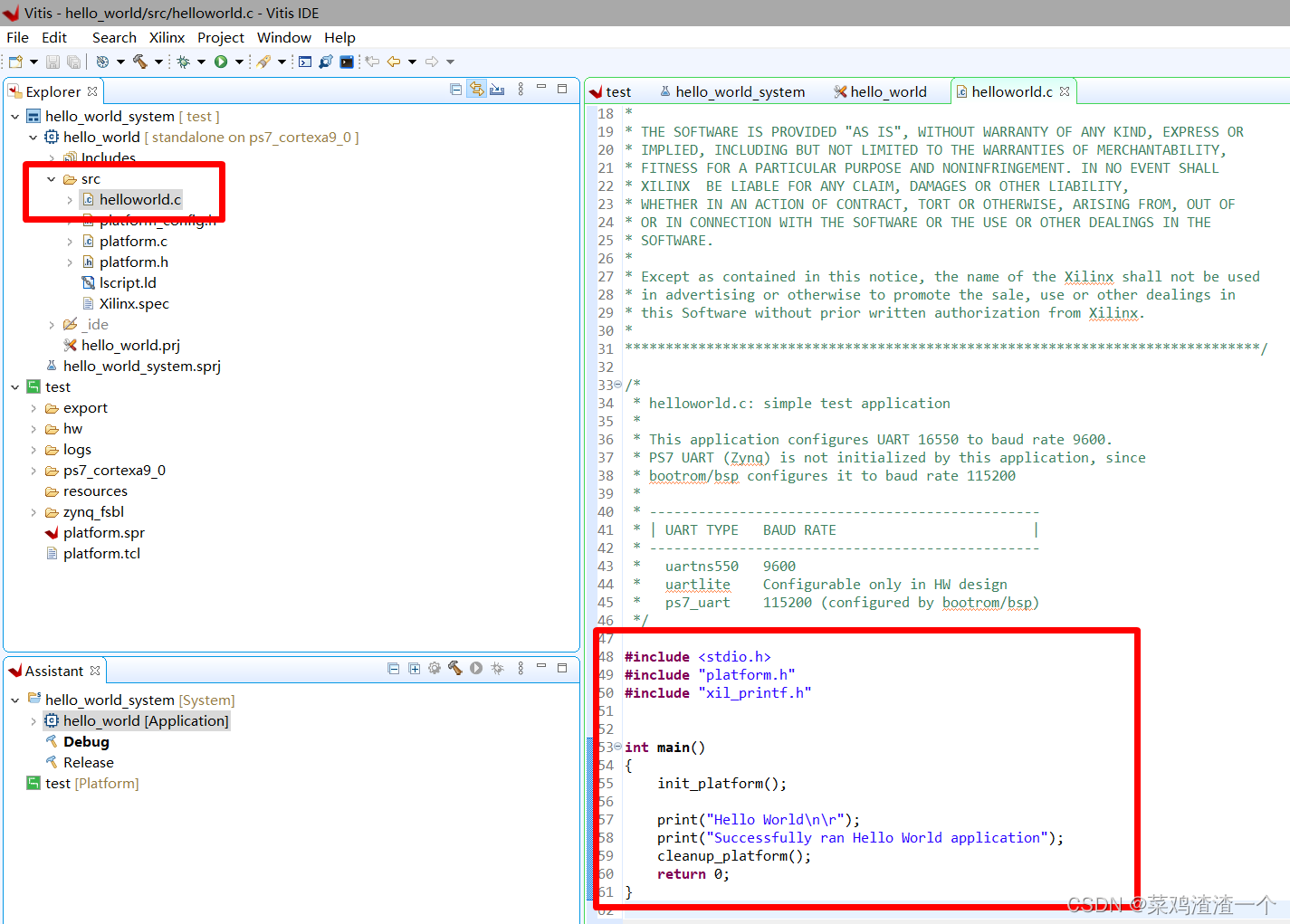

在c文件中可以看到对应的print代码。

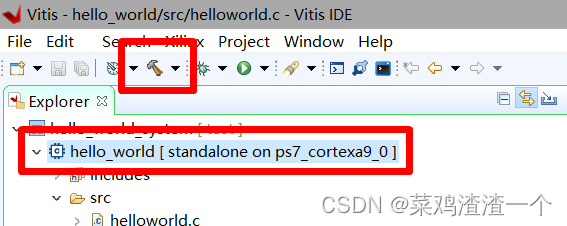

编译Application内核。

将下载器和供电连接好开发板后,将程序下载到开发板。(一般来说供电的接口和串口是同一个)

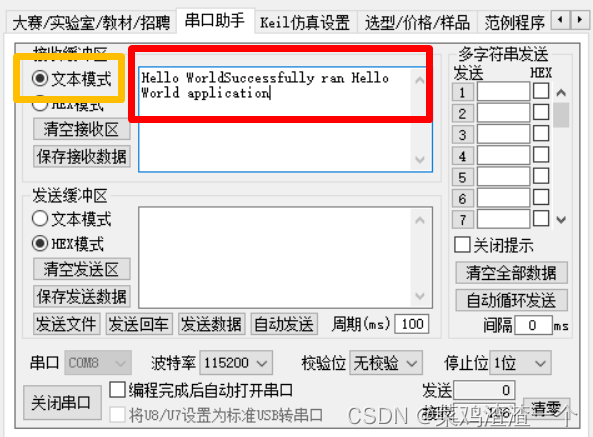

结果

Vitis IDE自带的串口助手并不好找,最好在下载程序之前使用其他的串口助手,设置好串口号后,就能接收到串口信息了。

808

808

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?