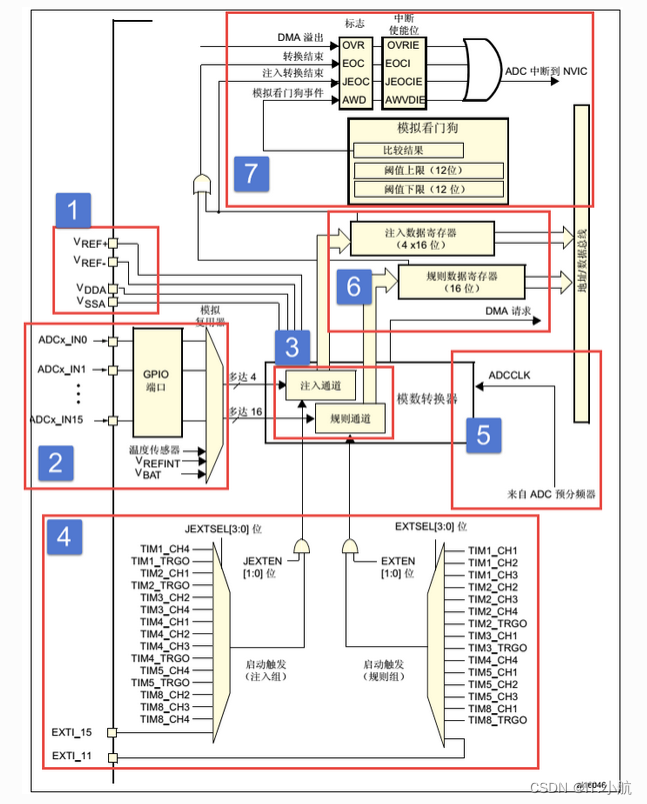

一、ADC功能框图

整体框架如下图,下面会逐个部分讲解。

1.电压输入范围

红框1、VREF±引脚为ADC基准参考电压(正负),Vdda、Vssa引脚为芯片的工作正负电压(模拟)。

ADC可以采集的电压范围为: VREF- ≤ VIN ≤ VREF+。我们在设计原理图的时候一般把 VSSA 和 VREF-接地,把 VREF+和 VDDA 接 3V3,得到ADC 的输入电压范围为: 0~3.3V。

2. 输入通道

红框2、ADC外设采集电压的通道。

STM32的ADC多达19个通道,其中外部的16个通道,分别对应着不同的IO口,内部2个通道。通道和IO口对应关系如下图。

外部的16个通道在转换的时候又分为规则通道和注入通道,其中规则通道最多有16路,注入通道最多有4路。

规则通道

规则通道:顾名思意,规则通道就是很规矩的意思,我们平时一般使用的就是这个通道,或者应该说我们用到的都是这个通道,没有什么特别要注意的可讲。

注入通道

注入,可以理解为插入,插队的意思,是一种不安分的通道。它是一种在规则通道转换的时候强行插入要转换的一种通道。如果在规则通道转换过程中, 有注入通道插队,那么就要先转换完注入通道,等注入通道转换完成后,再回到规则通道的转换流程。这点跟中断程序很像, 都是不安分的主。所以,注入通道只有在规则通道存在时才会出现。

3. 转化顺序

红框3、配置ADC通道的转化顺序,分为规则和注入。

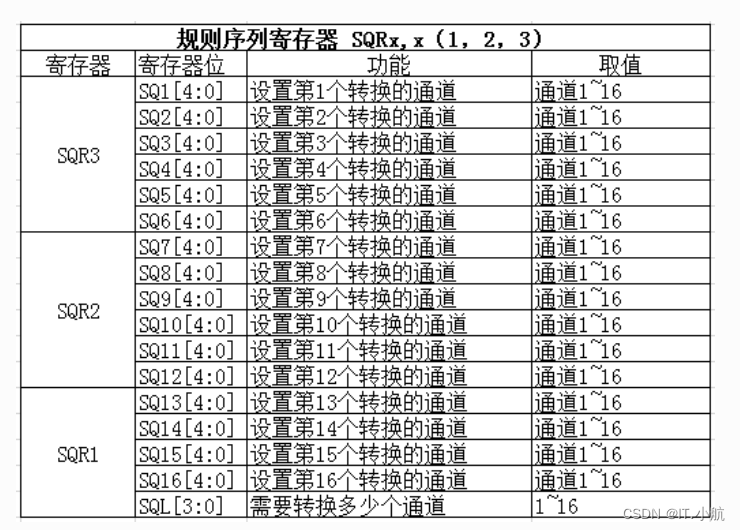

规则序列

规则序列寄存器有3个,分别为ADC_SQR3、ADC_SQR2、ADC_SQR1。SQR1的位L[3:0]决定需要转化多少个通道(最多16个)。SQ1~SQ16寄存器位配置通道x为第几次转化。

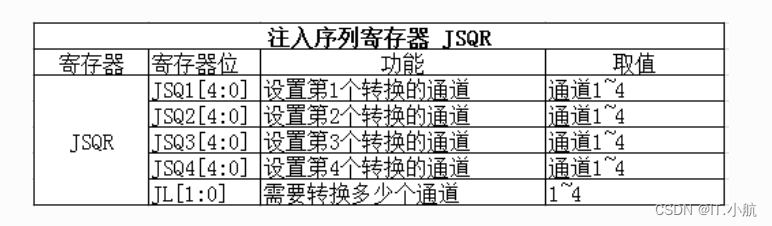

注入序列

注入序列寄存器JSQR只有一个,最多支持4个通道,具体多少个由JSQR的JL[1:0]决定。如果JL的 值小于4的话,则JSQR跟SQR决定转换顺序的设置不一样, 第一次转换的不是JSQR1[4:0],而是JCQRx[4:0] ,x =(4-JL),跟SQR刚好相反。如果JL=00(1个转换),那么转换的顺序是从JSQR4[4:0]开始, 而不是从JSQR1[4:0]开始,这个要注意,编程的时候不要搞错。当JL等于4时,跟SQR一样。

4.触发源

红框4、开启ADC转换的控制方式。

软件开启转化: 向ADC_CR2的ADON这个位写1则开始转换,写0停止转换。

外部事件触发转换:这个触发包括内部定时器触发和外部IO触发。触发源有很多, 具体选择哪一种触发源,由ADC控制寄存器2:ADC_CR2的EXTSEL[2:0]和JEXTSEL[2:0]位来控制。EXTSEL[2:0]用于选择规则通道的触发源, JEXTSEL[2:0]用于选择注入通道的触发源。

如果使能了外部触发事件,我们还可以通过设置ADC控制寄存器2:ADC_CR2的EXTEN[1:0]和JEXTEN[1:0]来控制触发极性, 可以有4种状态,分别是:禁止触发检测、上升沿检测、下降沿检测以及上升沿和下降沿均检测。

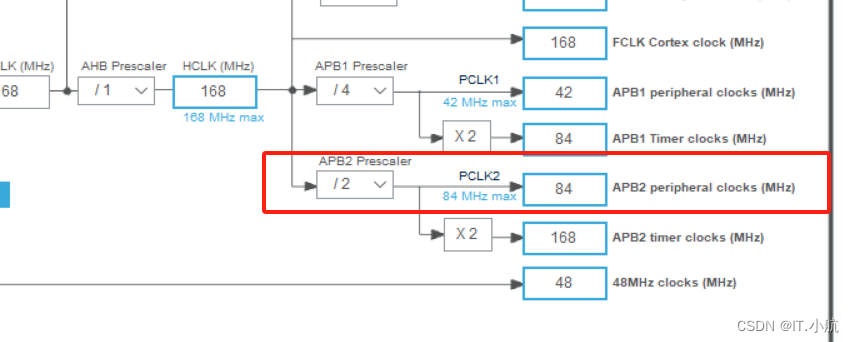

5.转换时间

红框5、ADC输入时钟,设置采样周期。

ADC时钟: ADC输入时钟ADC_CLK由PCLK2经过分频产生。ADC_CCR的ADCPRE[1:0]设置, 可设置的分频系数有2、4、6和8,注意这里没有1分频。对于STM32F429IGT6我们一般设置最高时钟PCLK2=84MHz,ADC的时钟一般使用4分频(84/4MHz)或者6分频(84/6MHz)。

采样时间: ADC需要若干个ADC_CLK周期完成对输入的电压进行采样,采样的周期数可通过ADC 采样时间寄存器ADC_SMPR1和ADC_SMPR2中的SMP[2:0]位设置, ADC_SMPR2控制的是通道0-9 ,ADC_SMPR1控制的是通道10~17。

ADC的总转换时间跟ADC的输入时钟和采样时间有关,公式为:

Tconv = 采样时间 + 12个周期

一般我们设置PCLK2=84MHz,经过ADC预分频器4分频到最大的时钟只能是21M,采样周期设置为3个周期,算出最短的转换时间为0.7142us,这个才是最常用的。

6.数据寄存器

红框6、选择采集完数据的保存方式。

规则数据寄存器ADC_DR:

ADC规则组数据寄存器ADC_DR只有一个,是一个32位的寄存器,只有低16位有效并且只是用于独立模式存放转换完成数据。因为ADC的最大精度是12位, ADC_DR是16位有效,这样允许ADC存放数据时候选择左对齐或者右对齐,

(规则通道可以有16个这么多,可规则数据寄存器只有一个,如果使用多通道转换,那转换的数据就全部都挤在了DR里面,前一个时间点转换的通道数据, 就会被下一个时间点的另外一个通道转换的数据覆盖掉,所以当通道转换完成后就应该把数据取走,或者开启DMA模式,把数据传输到内存里面, 不然就会造成数据的覆盖。最常用的做法就是开启DMA传输。)

注入数据寄存器ADC_JDRx

ADC注入组最多有4个通道,刚好注入数据寄存器也有4个,每个通道对应着自己的寄存器,不会跟规则寄存器那样产生数据覆盖的问题。 ADC_JDRx是32位的,低16位有效,高16位保留,数据同样分为左对齐和右对齐,具体是以哪一种方式存放,由ADC_CR2的11位ALIGN设置。

通用规则数据寄存器ADC_CDR

规则数据寄存器ADC_DR是仅适用于独立模式的,而通用规则数据寄存器ADC_CDR是适用于双重和三重模式的。独立模式就是仅仅适用三个ADC的其中一个, 双重模式就是同时使用ADC1和ADC2,而三重模式就是三个ADC同时使用。在双重或者三重模式下一般需要配合DMA数据传输使用。

7.中断

红框7、数据转换结束后,可以产生的中断。

中断分为四种:规则通道转换结束中断,注入转换通道转换结束中断,模拟看门狗中断和溢出中断。

规则和注入通道转换结束后,除了产生中断外,还可以产生DMA请求,把转换好的数据直接存储在内存里面。对于独立模式的多通道AD转换使用DMA传输非常有必须要, 程序编程简化了很多。对于双重或三重模式使用DMA传输几乎可以说是必要的。

8.电压转换

模拟电压经过ADC转换后,是一个相对精度的数字值。ADC的输入电压范围设定在:0~3.3v,如果设置ADC为12位的,那么12位满量程对应的就是3.3V,读出的数据为2^12-1=4095。 数值0对应的就是0V。

电压值=读出数据/4096 x 3.3v

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?