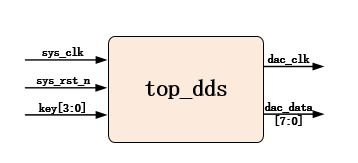

Step1:流程图设计出Key_control模块,DDS波形模块以及Top_DDS模块。

其中Key_control模块中需要设计一个Key_filter防抖模块

DDS波形模型中需要调用一个已经设计的ROM的IP核。

![]()

接着画出时序图。

Step2:Key_control模块的实现:

`timescale 1ns/1ns

module key_control

(

input wire sys_clk , //系统时钟,频率为50Mhz

input wire sys_rst_n, //复位信号,低电平有效

input wire [3:0] key, //输入4位按键

output reg [3:0] wave_select //输出波形选择

);

//首先要定义下面可能用到的参数:

parameter sin_wave = 4’b0001, //正弦波

squ_wave = 4’b0010, //方波

tri_wave = 4’b0100, //三角波

saw_wave = 4’b1000; //锯齿波

parameter CNT_MAX = 20’d999_999; //计数器计数的最大值

//定义wire型变量:

wire key3;

wire key2;

wire key1;

wire key0;

//主程序:

always@ (posedge sys_clk or negedge sys_rst_n)

if (sys_rst_n &#

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

675

675

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?