1、寄存器、锁存器和触发器:

(1)寄存器:边沿触发的存储单元,在上升或下降沿数据变化,一个周期里只能变化一次。

寄存器:一般是边沿触发的触发器,在时序电路中寄存器的作用就是只在时钟的边沿有效传输data(满足建立时间和保持时间使得数据是稳定被采得)。在实际的数字系统中,通常把能够用来存储一组二进制代码的同步时序逻辑电路称为寄存器。由于触发器内有记忆功能,因此利用触发器可以方便地构成寄存器。由于一个触发器能够存储一位二进制码,所以把n个触发器的时钟端口连接起来就能够构成一个存储n位二进制码的寄存器。

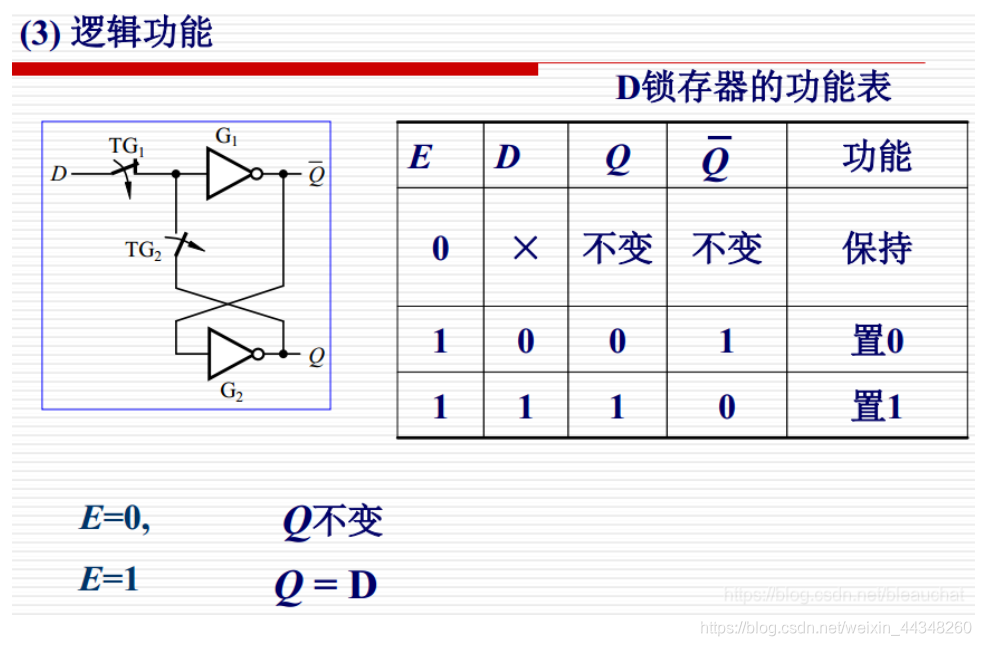

(2)锁存器(latch)——对时钟脉冲敏感==(电平敏感)==,在时钟脉冲的电平下改变状态;

锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,当锁存器处于使能状态时,输出才会随着数据输入发生变化。(简单地说,它有两个输入,分别是一个有效信号EN,一个输入数据信号DATA_IN,它有一个输出Q,它的功能就是在EN有效的时候把DATA_IN的值传给Q,也就是锁存的过程);

(3)触发器(Flip-Flop,简写为FF)——对脉冲边沿敏感==(边沿敏感)==,其状态只在时钟脉冲的上升沿或下降沿的瞬间改变;

触发器也叫双稳态门,又称双稳态触发器,是一种可以在两种状态下运行的数字逻辑电路。触发器一直保持它们的状态,直到它们收到输入脉冲,又称为触发。当收到输入脉冲时,触发器输出就会根据规则改变状态,然后保持这种状态直到收到另一个触发 ;

2、寄存器和锁存器的区别,使用场景

(1) 寄存器是同步时钟控制,而锁存器是电位信号控制。锁存器一般由电平信号控制,属于电平敏感型。寄存器一般由时钟信号控制,属于边沿敏感型。

(2) 寄存器的输出端平时不随输入端的变化而变化,只有在时钟有效时才将输入端的数据送输出端(打入寄存器),而锁存器的输出端平时总随输入端变化而变化,只有当锁存器信号到达时,才将输出端的状态锁存起来,使其不再随输入端的变化而变化。

可见,寄存器和锁存器具有不同的应用场合,取决于控制方式以及控制信号和数据之间的时间关系:若数据有效一定滞后于控制信号有效(锁存信号(控制信号)来了以后,才将输出端的状态/数据锁存起来),只能使用锁存器;如果数据提前于控制信号而到达且要求同步操作,则可以用寄存器来存放数据。

换言之,控制信号/时钟信号先来,数据后来,用锁存器;

控制信号/时钟信号后来,数据先来,用寄存器

3、锁存器与触发器的区别

锁存器不同于触发器,它不在锁存数据时,输出端的信号随输入信号变化,就想信号通过一个缓冲器一样;一旦锁存信号起锁存作用,则数据被锁住,输入信号不起作用。锁存器也称为透明锁存器,指的是不锁存时输出对于输入是透明的。

1、 锁存器同所有的输入信号相关,当输入信号变化时锁存器就变化,没有时钟端;触发器受时钟控制,只有在时钟触发时才采样当前的输入,产生输出。

2、 锁存器是电平触发,非同步控制。在使能信号有效时锁存器相当于通路,在使能信号无效时锁存器保持输出状态。触发器由时钟沿触发,同步控制。

3、 锁存器对输入电平敏感(输出随输入的变化而变化),受布线延迟影响较大,很难保证输出没有毛刺产生;触发器则不易产生毛刺。锁存器容易产生毛刺。

4、异步FIFO简介及其原理

https://blog.csdn.net/weixin_44348260/article/details/119612998

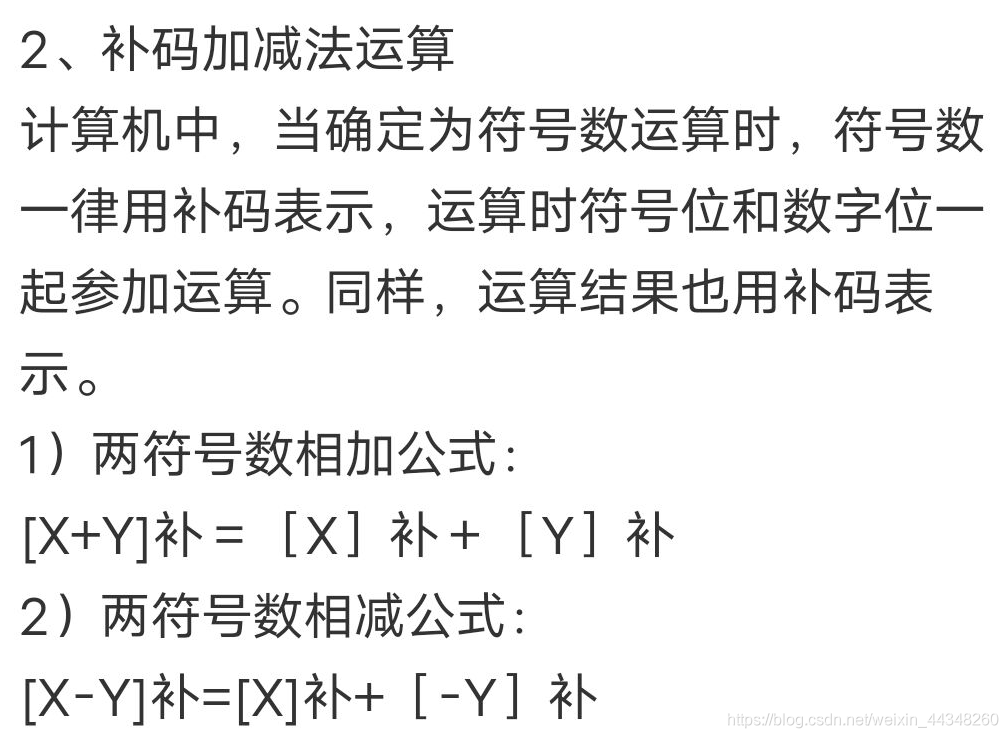

5、怎么完成一个6bit符号数和8bit符号数想加

都是有符号位的,先去掉符号位,将剩余位求补码,即按位取反后加1,然后转换为10进制直接相加,最后看符号为是1则结果为负数,否则为正数。

例题:

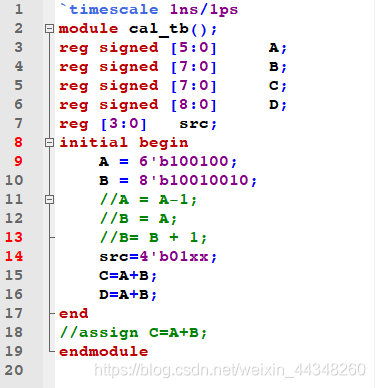

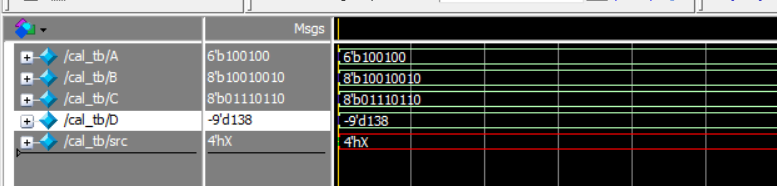

代码中A = 6’b100100; B = 8’b10010010;

A的剩余5位反码为11100,十进制为28;

B的剩余7位反码为1101110,十进制为110;

相加后为138加上符号为-138

注意:

(在计算时,表达式中有一个无符号位,则所有操作数被强制转换为无符号数。如果均为无符号数,那么负数基本都是按照去掉符号位后,其余位取补码)

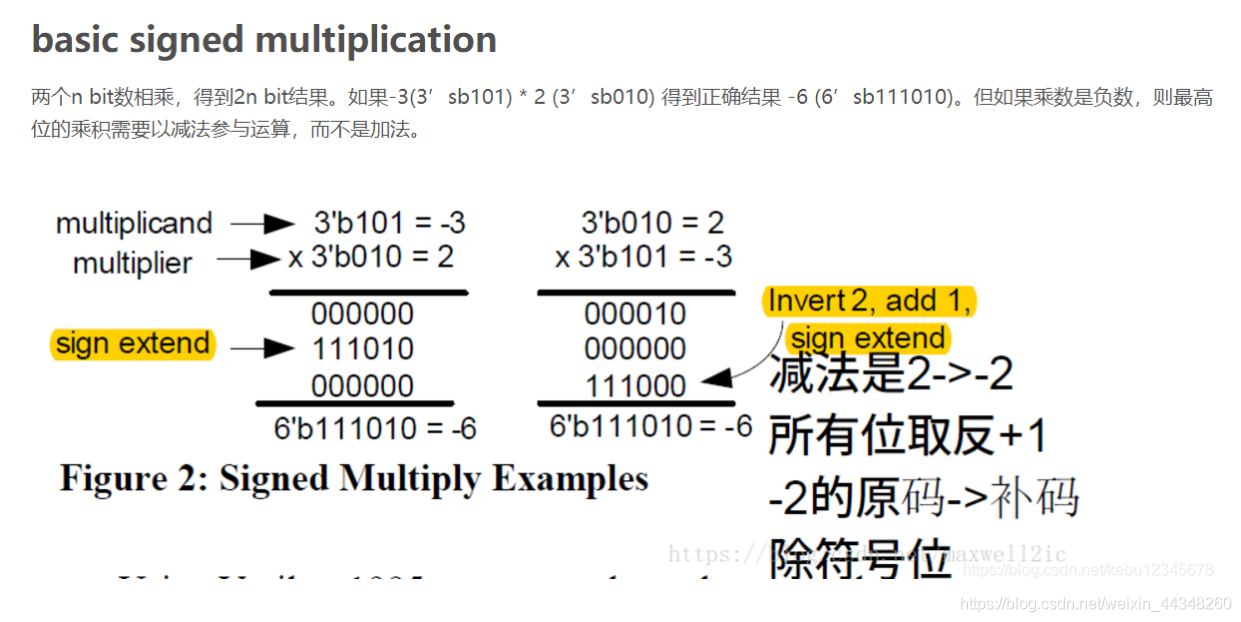

6、补充有符号数相乘:

即相乘时有符号数转化为补码进行操作,位数少且不为0时前面补1.

7、组合逻辑用FPGA的什么资源实现?

由于过长的组合逻辑链(级联的LUT)会引入较大的延时,而时序逻辑(REG)能够把较长的组合逻辑链分割成较短的组合逻辑链,有效地缩短关键路径和次关键路径的长度,进而提高该FPGA设计的整体时序性能,所以组合逻辑与时序逻辑的使用比例可以作为评价一个FPGA设计时序性能的辅助参数。

组合逻辑占用LUT;

时序逻辑占用REG(触发器);

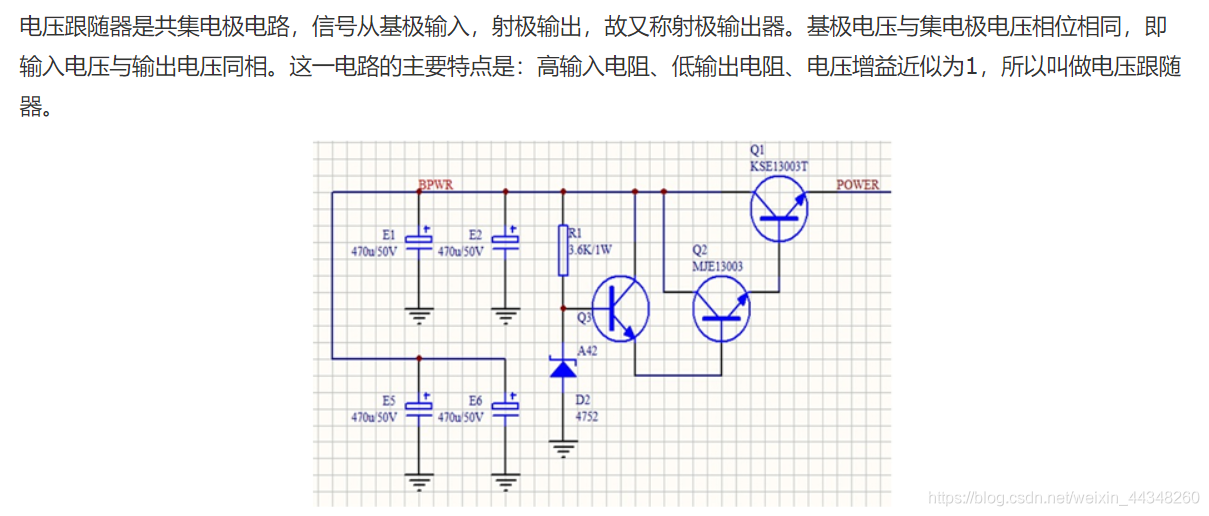

8、电压跟随器的原理

- 定义:电压跟随器,顾名思义,就是输出电压与输入电压是相同的,就是说,电压跟随器的电压放大倍数恒小于且接近1。

- 特点:输入阻抗高,而输出阻抗低;

- 作用:电压跟随器起缓冲、隔离、提高带载能力的作用。

9、阻塞赋值和非阻塞赋值的区别;

- 在描述组合逻辑的always块中使用阻塞赋值;

- 在描述时序逻辑的always块中使用非阻塞赋值

阻塞赋值:前面语句执行完,才可执行下一条语句;即:前面语句的执行(b=a)阻塞了后面语句的执行(c=b)。即:always块内,2条语句顺序执行。

always @(posedge i_clk)

begin

b = a;

c = b;

end

非阻塞赋值:always块内,2条语句同时执行。即:前面语句的执行(b=a)不会阻塞后面语句的执行(c=b)。

always @(posedge i_clk)

begin

b <= a;

c <= b;

end

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?