参考视频:

数字IC,FPGA秋招【单bit信号的CDC跨时钟域处理手撕代码合集】_哔哩哔哩_bilibili

一、亚稳态

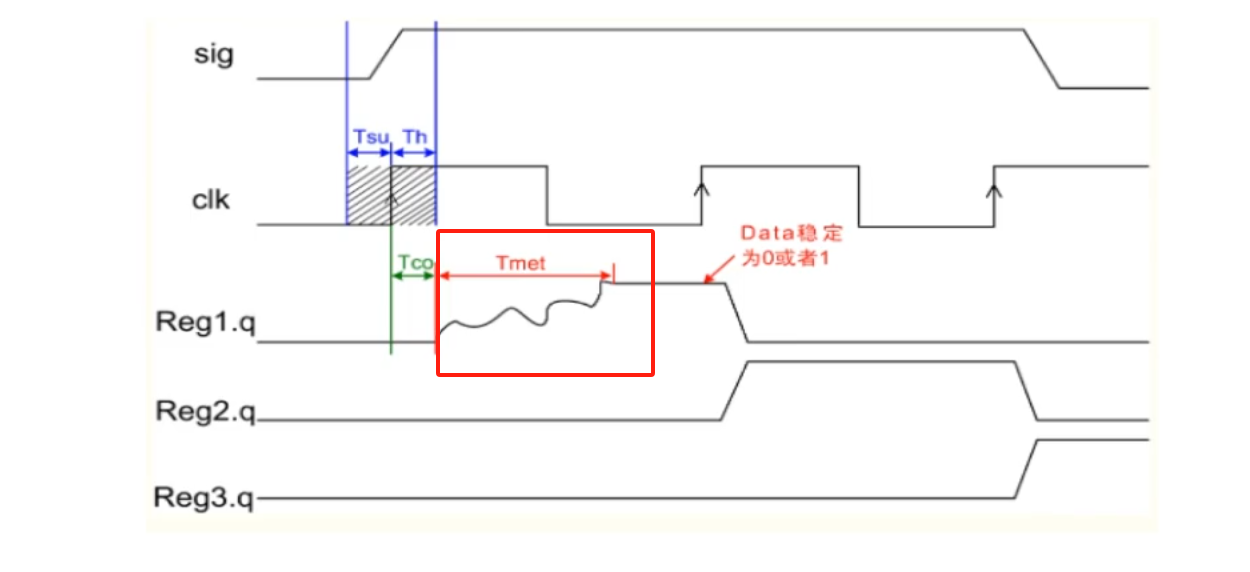

原因是:建立时间和保持时间没有保持住。然后在下图的红框里面,产生亚稳态。因为电路反馈机制,最后大概率会恢复到一个正确的值(低电平0或者高电平1)。

二、单bit跨时钟域

慢时钟域到快时钟域

打两拍就行。

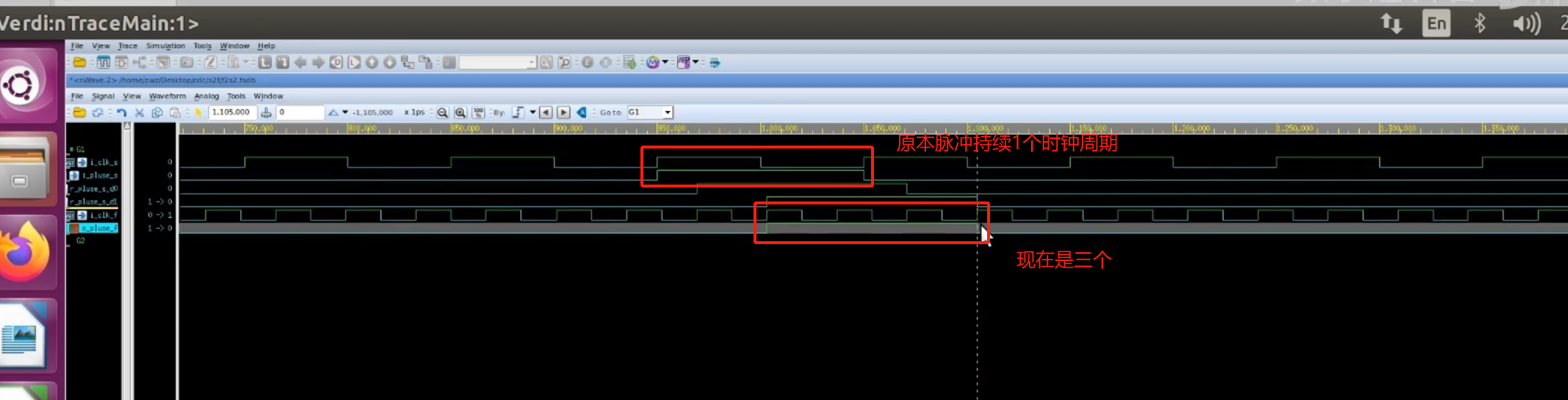

处理时,脉冲宽度会增加

快时钟域到慢时钟域

可能会发生采样不到的情况。解决方案:(1)脉冲展宽;为什么会产生毛刺呢??(因为assign fast pluse extentd =pluse r,这一段对时序有所考验)

module fast2slow_cdc

(

input clk_f ,

input clk_s ,

input pluse_f ,

output pluse_s

);

// 用循环移位寄存器实现

localparam PIPE_NUM = 2; // 表示要打2拍,因为pluse_r作为输入也要占一位的空间

reg [PIPE_NUM : 0] pluse_r;

always @(posedge clk_f) begin

pluse_r <= {pluse_r[PIPE_NUM-1 : 0],pluse_s};

end

// 得到快时钟域的展宽

wire fast_pluse_extentd;

assign fast_pluse_extentd = |pluse_r;// 按位或,输入的几位,有一个是1,那么就全是1

reg s_pluse_d1;

reg s_pluse_d2;

// 同步到慢时钟域,用慢时钟域的时钟

always @(posedge clk_s) begin

s_pluse_d1 <= fast_pluse_extentd ;

s_pluse_d2 <= s_pluse_d1 ;

end

assign pluse_s = s_pluse_d2;

endmodule(2)脉冲电平检测+双触发器同步+边沿检测

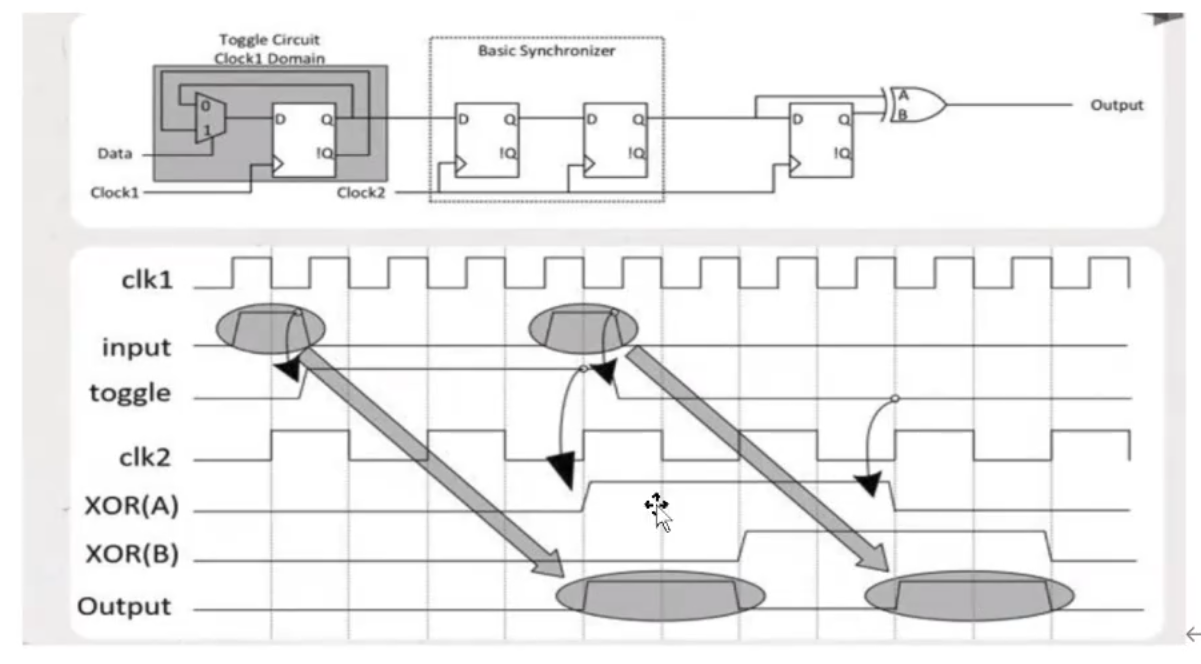

第一步,先做一个边缘检测,检测到输入信号的上升沿,然后做一次电平翻转。这样就能做到没有毛刺的脉冲扩展

第二步,打三拍

第三步,用打最后两 拍的数据,做异或处理

注意

亚稳态无法消除,只能被减弱。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?