为了在电路设计和嵌入式程序开发的过程中能够熟能生巧,有关电子元器件、专业术语和芯片封装,我做了一些详尽调研。以下为收集得到的有用内容。

1. 软件功能术语

下面的英文单词简写都是工作中会用到的

- DRC:Design rule check,方便检测PCB图中不符合规则的部分

- ERC:Electrical Rules Check ,电气规则检查

- ERP:Enterprise Resource Planning,企业资源计划

- DXF:Drawing Exchange Format,绘图交换格式

- SOP:Standard Operating Procedure, 标准作业程序

- CNC:Computer Numerical Control,计算机数控

- STL:stereolithography,光固化立体造型术

2. 电子元件概念

电阻(R)

电阻在电路中用“R”加数字表示,如:R1表示编号为1的电阻。

- 主要作用为:分流、限流、分压、偏置等。

- 标注方法有3种,即直标法,色标法和数标法。

- 数标法主要用于贴片等小体积的电路,如:472 表示 47×100Ω(即4.7K);104则表示 10×10000Ω(即100K )

电容(C)

电容在电路中一般用“C”加数字表示,如:C13表示编号为13的电容。

- 电容是由两片金属膜紧靠,中间用绝缘材料隔开而组成的元件。电容的特性主要是隔直流通交流。

- 常用电容的种类有电解电容、瓷片电容、贴片电容、独石电容、钽电容和涤纶电容等。

- 数字表示法,如:102 表示10×100PF =1000PF,224 表示22×10000PF = 0.22 uF

- 电容容量误差符号 F G J K L M ;允许误差对应为 ±1% ±2% ±5% ±10% ±15% ±20% ;如:一瓷片电容为104J表示容量为0. 1 uF、误差为±5%。

电感(L)

- 电感在电路中常用“L”加数字表示,如:L6表示编号为6的电感。

- 电感线圈是将绝缘的导线在绝缘的骨架上绕一定的圈数制成。当交流信号通过线圈时,线圈两端将会产生自感电动势,自感电动势的方向与外加电压的方向相反,阻碍交流的通过,所以电感的特性是通直流阻交流,频率越高,线圈阻抗越大。

晶体二极管(D)

- 在电路中常用“D”加数字表示,如: D5表示编号为5的二极管。

- 二极管的主要特性是单向导电性,也就是在正向电压的作用下,导通电阻很小;而在反向电压作用下导通电阻极大或无穷大

- 晶体二极管按作用可分为:整流二极管(如1N4004)、隔离二极管(如1N4148)、肖特基二极管(如BAT85)、发光二极管、稳压二极管等。

晶体三极管(Q)

- 晶体三极管在电路中常用“Q”加数字表示,如:Q17表示编号为17的三极管。

- 晶体三极管(简称三极管)内部含有2个PN结,并且具有放大能力。

3. 专业英文术语

- ASIC(Application Specific IntegratedCircuit-专用集成电路):适合于某一单一用途的集成电路产品。

- BGA(Ball GridArray-球栅阵列):以球型引脚焊接工艺为特征的一类集成电路封装。

- CMOS(Complementary Metal OxideSemiconductor-互补金属氧化物半导体):先进的集成电路加工工艺技术,具有高集成、低成本、低能耗和高性能等特征。CMOS是现在高密度可编程逻辑器件(PLD)的理想工艺技术。

- EDA(Electronic Design Automation-电子设计自动化):即通常所谓的电子线路辅助设计软件。

- FPGA(Field Programmable Gate Array-现场可编程门阵列):含有小逻辑单元的高密度PLD,这些逻辑单元通过一个分布式的阵列可编程开关而连接。这种体系结构随着性能和功能容量不同而产生统计上的不同结果,但是提供的寄存器数量多。其可编程性很典型地通过易失SRAM 或者一次性可编程的反熔丝来体现。

- PLC(Programmable Logic Cell-可编程逻辑单元):这些单元是 ORCA FPGA 器件中的心脏部分,他们被均匀地分配在 ORCA FPGA 器件中,包括逻辑、布线、和补充逻辑互连单元(SLIC)。

- ISPTM(In-System Programmability-在系统可编程):由莱迪思首先推出,莱迪思 ISP产品可以在系统电路板上实现编程和重复编程。

- JTAG(Joint Test Action Group-联合测试行动组):一系列在主板加工过程中的对主板和芯片级进行功能验证的标准。

- VHDL:VHSIC硬件描述语言,高级的基于文本的设计输入语言。

- Differential ADC(差分模拟/数转换器):一个带有差分输入的模/数字转换器。这意味着,输入信号是由两个电压差表示,这样极大的降低噪声和其它干扰因素的影响。

- Filter(滤波器):执行过滤功能的电路。比如:从信号中去除某些不理想的信号。通常, Gain(增益):信号放大的因子

- High-pass filter(高通滤波器):一种类型的滤波器,只允许高于某一频率的信号通过。(所有低于限定频率的信号都将被衰减掉)。

- Offset(偏移):一个信号偏离所需电压或者电流的固定数量

- Output Amplifier(输出放大器):一种用于放大信号的电路,可承载很重的负荷。

- Phase(相位):时间或者延迟上的差异。通常来讲,该术语用来表示相位迁移,意思是,

- Pulse width modulation(脉宽调制-PWM):根据输入信号成比例地改变输出脉冲宽度。

- Sample Rate(采样速率):一个 A/D 或者D/A 转换器的速度技术规格。它描述了最大数据通过量,用每秒采样数或者赫兹来测量。例如,100ks/s,或者 100kHz。

- Voltage reference(参考电压):在一定的温度范围内和电源条件下,一个电路产生一个非常精确稳定的电压。

4. 元件封装知识

这里讨论电阻电容的封装,封装尺寸与功率的关系如下 :

- 0201 -> 1/20W

- 0402 -> 1/16W

- 0603 -> 1/10W

- 0805 -> 1/8W

- 1206 -> 1/4W

电阻电容的封装与外形尺寸(单位:mm)的对应关系是:

- 0402 = 1.0 x 0.5

- 0603 = 1.6 x 0.8

- 0805 = 2.0 x 1.2

- 1206 = 3.2 x 1.6

- 1210 = 3.2 x 2.5

- 1812 = 4.5 x 3.2

- 2225 = 5.6 x 6.5

芯片的封装类型大致有:

DIP,SIP,ZIP,S-DIP,SK-DIP,PGA,SOP,MSP,QFP,SVP,LCCC,PLCC,SOJ,BGA,CSP,TCP等等,下面列举在嘉立创商城中常见的一些芯片封装图:

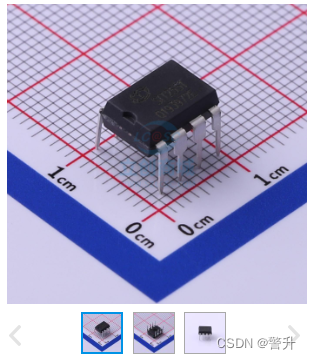

-

DIP(Dual In-line Package):双列直插式封装.顾名思义,该类型的引脚在芯片两侧排列,是插入式封装中最常见的一种,引脚节距为2.54 mm,电气性能优良,又有利于散热,可制成大功率器件.

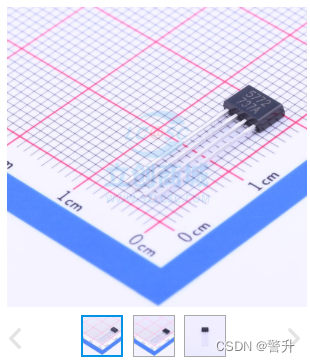

-

SIP(Single In-line Package):单列直插式封装.该类型的引脚在芯片单侧排列,引脚节距等特征与DIP基本相同.ZIP:Z型引脚直插式封装.该类型的引脚也在芯片单侧排列,只是引脚比SIP粗短些,节距等特征也与DIP基本相同.

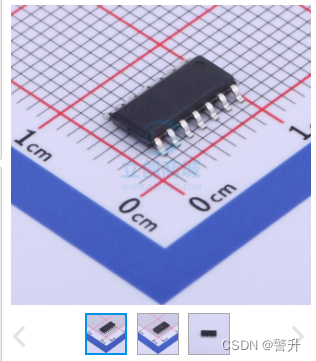

-

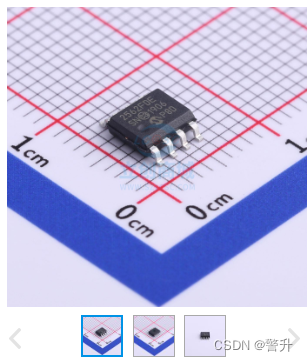

SOP(Small Outline Package):小外型封装.表面贴装型封装的一种,引脚端子从封装的两个侧面引出,字母L状.引脚节距为1.27mm.

SOT:(Small Outline Transistor):一般引脚小于等于5个的小外形晶体管。根据表面宽度的不同分为两种,一种宽度为1.3mm,一种宽度为1.6mm。SOT一般指贴片三极管的封装。

SOD:(Small Outline Diode),SOD后面常会是跟一串数字,表示封装的标准序号,如:SOD-23,SOD-523,SOD323等等。

SOIC:(Small Outline Integrated Circuit Package):他跟SOP的区别在于,他里封装的是IC电路。

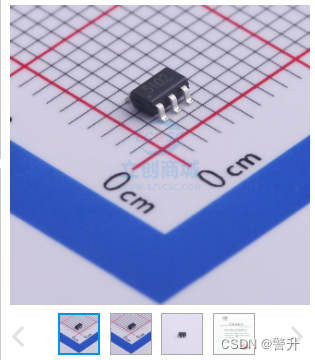

-

QFP(Plastic Quad Flat Package):四方扁平封装.表面贴装型封装的一种,引脚端子从封装的两个侧面引出,呈L字形,引脚节距为1.0mm,0.8mm,0.65mm,0.5mm,0.4mm,0.3mm,引脚可达300脚以上.

-

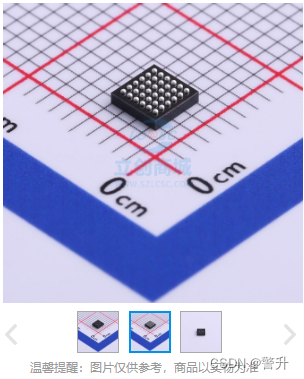

BGA(Ball Grid Array):球栅阵列封装.表面贴装型封装的一种,在PCB的背面布置二维阵列的球形端子,而不采用针脚引脚.焊球的节距通常为1.5mm,1.0mm,0.8mm,与PGA相比,不会出现针脚变形问题.

-

CSP(Chip Scale Package):芯片级封装.一种超小型表面贴装型封装,其引脚也是球形端子,节距为0.8mm,0.65mm,0.5mm等.

更多有关芯片封装的详细信息参阅:

- https://bbs.elecfans.com/jishu_1446719_1_1.html

- https://wenku.baidu.com/view/9c75aad40740be1e640e9a4e.html

- 嘉立创商城

本文详细介绍软件功能术语(如DRC、ERC等)、电子元件(电阻、电容、电感、二极管、三极管)的概念与应用,涵盖了专业英文术语(如ASIC、CMOS等)以及元件封装知识(0201到BGA)。通过实例讲解,助您提升电路设计和编程技能。

本文详细介绍软件功能术语(如DRC、ERC等)、电子元件(电阻、电容、电感、二极管、三极管)的概念与应用,涵盖了专业英文术语(如ASIC、CMOS等)以及元件封装知识(0201到BGA)。通过实例讲解,助您提升电路设计和编程技能。

3995

3995

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?