1、何为EMC整改

EMC整改就是指产品在功能调试或EMC测试过程中出现问题后所采取的弥补手段。

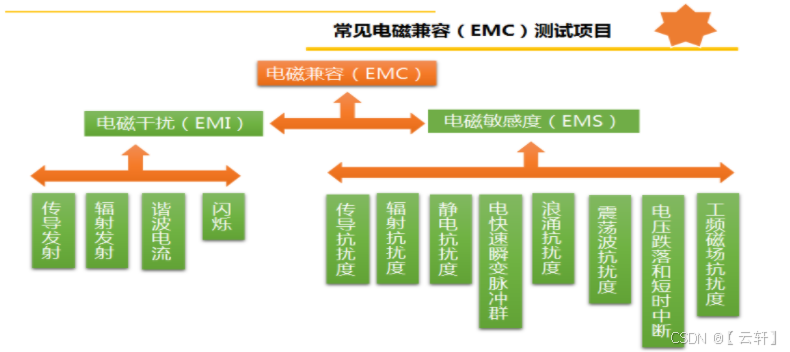

首先我们从EMC认证测试项目说起,EMC认证测试主要包含两大项:EMI(干扰)和EMS(产品抗干扰和敏感度)。

通过这些测试项我们可以看出EMC测试主要围绕产品的电磁干扰和敏感度两部分,一旦产品不符合安全认证标准需要EMC整改时,我们就需要通过一些措施和方法来进行整改。

2、EMC整改流程

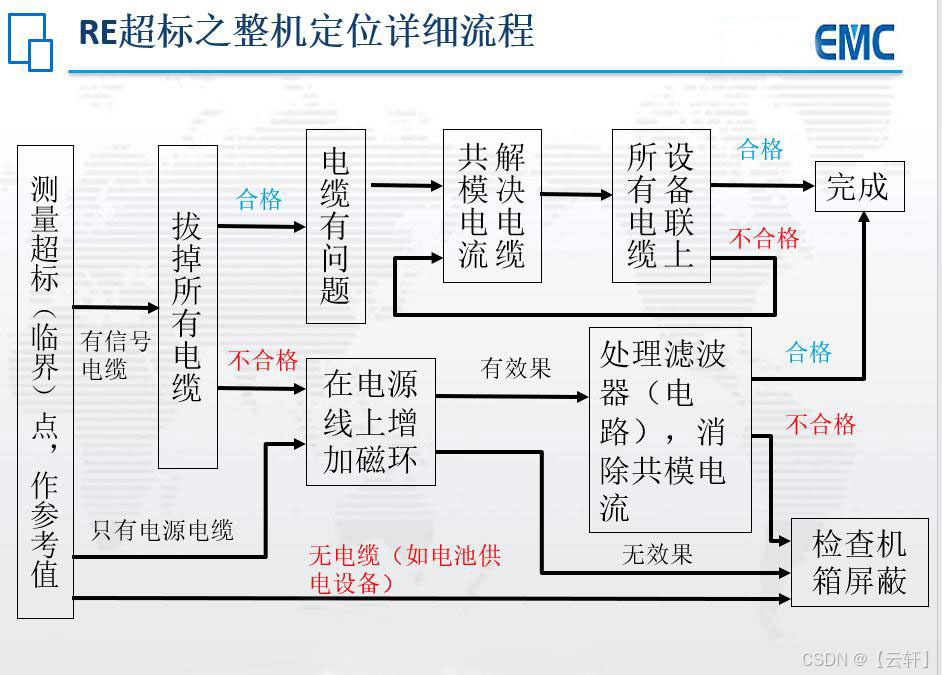

①、RE超标整改流程

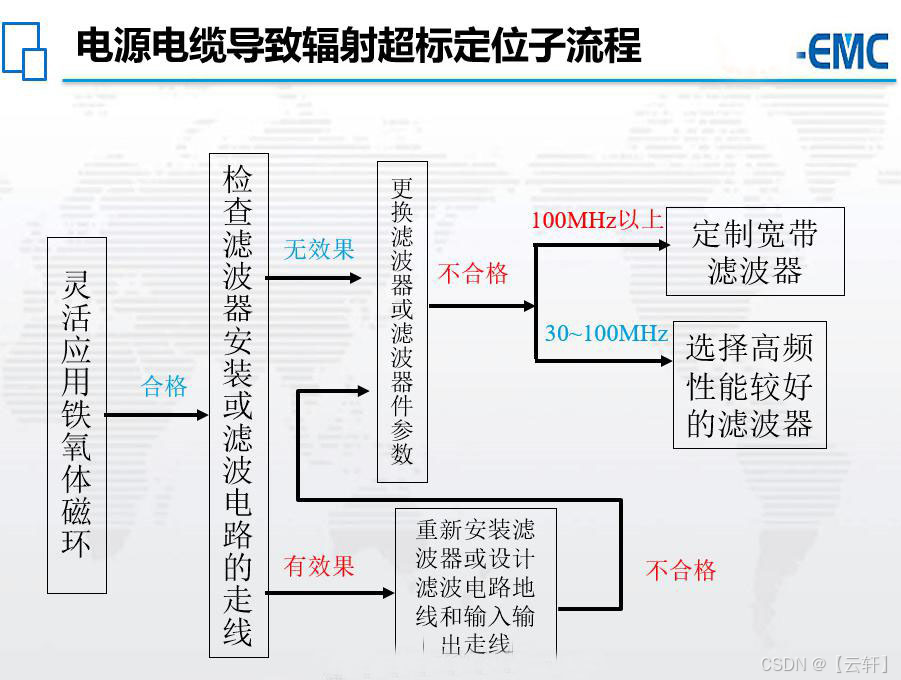

②、电源电缆导致辐射超标定位子流程

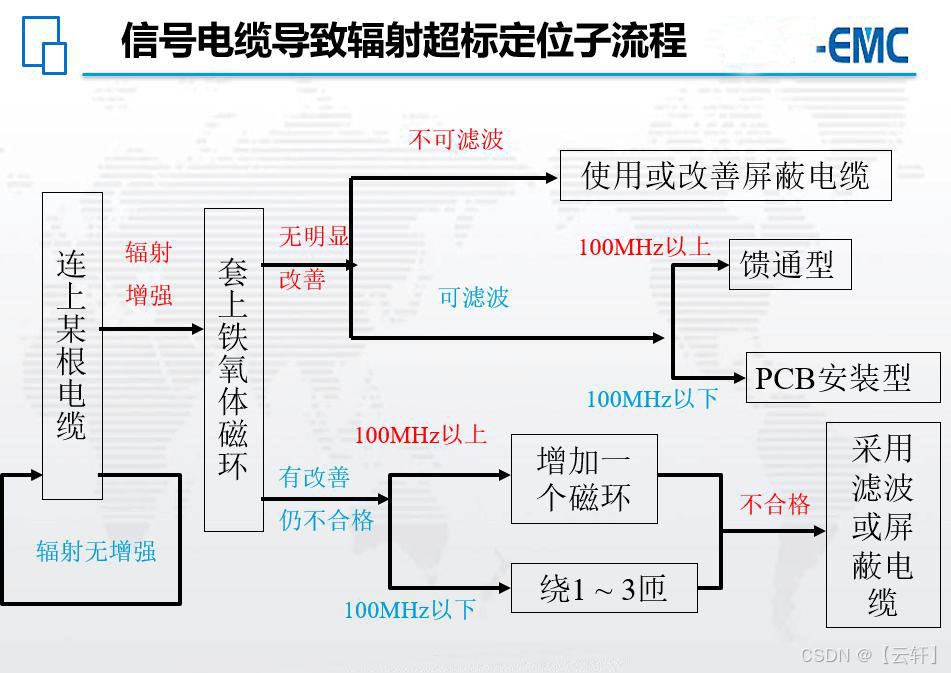

③、 信号电缆导致辐射超标定位子流程

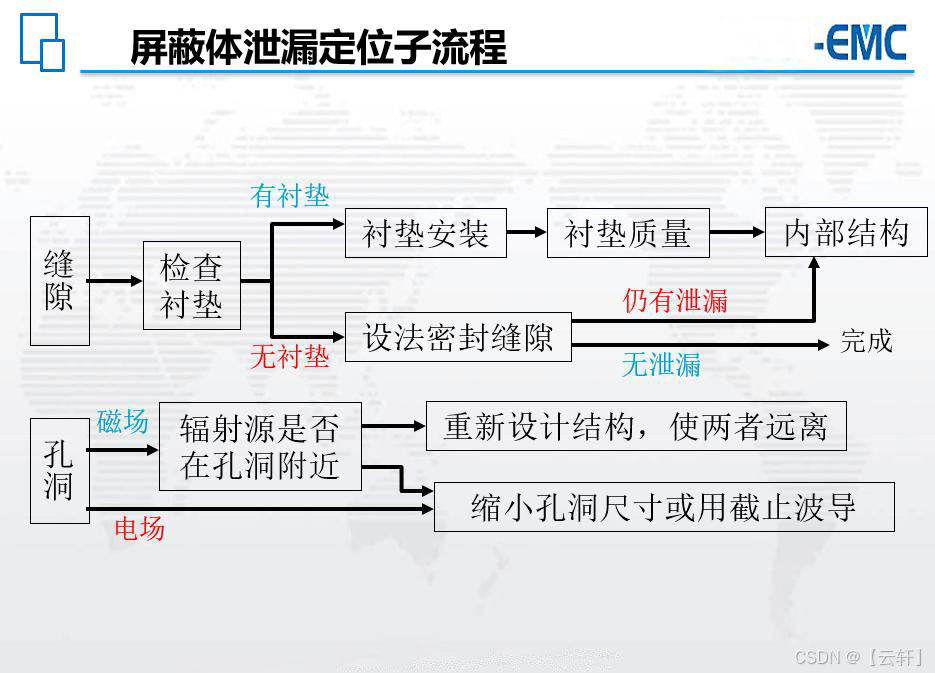

④、屏蔽体泄漏整改流程

3、整改方向

谈到EMC整改,我们常说的是EMC三要素,即敏感设备,耦合路径和干扰源。干扰源往往可以通过近场探头,排除法确认,干扰路径往往较难判定,干扰通常分为共模干扰和差模干扰。

共模干扰又分为电压驱动型,电流驱动型和磁场耦合型这三种类型,电压驱动型最典型的案例是干扰通过耦合到散热器向外辐射,电流驱动型典型案例是通过公共阻抗耦合到别的回路中,磁场耦合型较为常见,任何一个电流回路都会形成耦合,不同的是,恒定的电流形成的恒定的磁场,恒定的磁场不会再形成电场,变化的电流形成变化的磁场,干扰更为明显,后者也是电路中常见的。

差模干扰可以按照SIf*f/D进行排公式仅作参考,整改可以按照这个方向进行,其中,S-回路面积,I-电流大小,f-干扰频率,D-干扰源到被干扰源的距离。

根据多年EMC整改经验,针对以上分析,可以用“消除干扰源”,“堵”,“疏”确定整改方向,作为技术指引。

①、“除”

个人认为,消除干扰源是EMC整改最简便的方法,可以达到一劳永逸,消除干扰源通常分为:展频,“跳频”,有源钳位吸收,无源RC吸收电路,展频即将频率通过扩展频差,将能量分散,需要注意的是,对于基频,随着谐振倍数的增加,效果会越来越明显,展开的宽度会更宽,即如果对100KHz的频率进行展频处理,那么500KHz的谐振展频效果会比100KHz的展频效果更加明显。“跳频“即通过调整干扰频率,避开测试的频段,但是需要注意的是需要重新测试完整的频段,防止出现别的频段超标的现象出现,常见的有在测试低频段时,因开关电源导致辐射超标,通过增加开关电源的频率,从而避开该频段。RC吸收电路主要应用于吸收LC谐振电路。

②、“堵”

“堵”,抛开干扰源的部分,我们接下来需要注意的整改方向是“堵”还是“疏”,这个看似简单,但是可以为我们确定整改方向,避免出现胡乱使用各种整改方法,到头来还是思绪全无,EMC整改本身就是极大考验个人综合能力的,可能会出现花了一个月甚至更长的时间,但仍然全无进展,所以整改时确定方向是极其重要的。对于“堵”,实质就是堵干扰路径,干扰路径通常有公共阻抗干扰&感性耦合&容性耦合&空间辐射,堵公共阻抗干扰即增大干扰源对外路径的阻抗,通常有电源输出串联磁珠,电感,信号输出支路串联电阻,典型案例有对待晶振的地处理,通过可以采取在元器件层,挖孔该区域同时单点接地,避免该干扰流入大地,同时在对应的其他层留下地平面提供回路:“堵“容性耦合措施包括增加干扰源和被干扰源距离,减小干扰源和被干扰源的有效耦合面积,选择介电常数较小的材料隔在干扰源和被干扰源之间;“堵”感性耦合措施包括增加干扰源和被干扰源距离,减小干扰源和被干扰源之间的耦合有效面积,调整干扰源和被干扰源的方向,比如两者产生的磁场方向彼此垂直可达到“堵“感性耦合的效果;”堵“空间辐射,目前最为有效的即是用金属屏蔽罩接地的方法,实质上电磁屏蔽也属于消除干扰源,因为电磁屏蔽实质是引起阻抗失配,从而形成反射损耗,插入损耗,插入再反射损耗。

③、“疏”

“疏“亦为引导,即将干扰源引导到我们希望的地方,这个跟堵正好相反,通常措施有增大接地面积,降低回路阻抗,减小需要耦合路径的距离,电源/信号输出增加滤波电容等方式。下面以一篇实际案例为例分析。

4、常见EMC整改方法

①、排除外界因素

(1)将被测设备关电,确认背景噪声是否满足标准要求(标准要求电波暗室的背景噪声在限值线以下6dB);

(2)确认测试布置是否满足标准要求。

②、 宽带噪声抑制方法

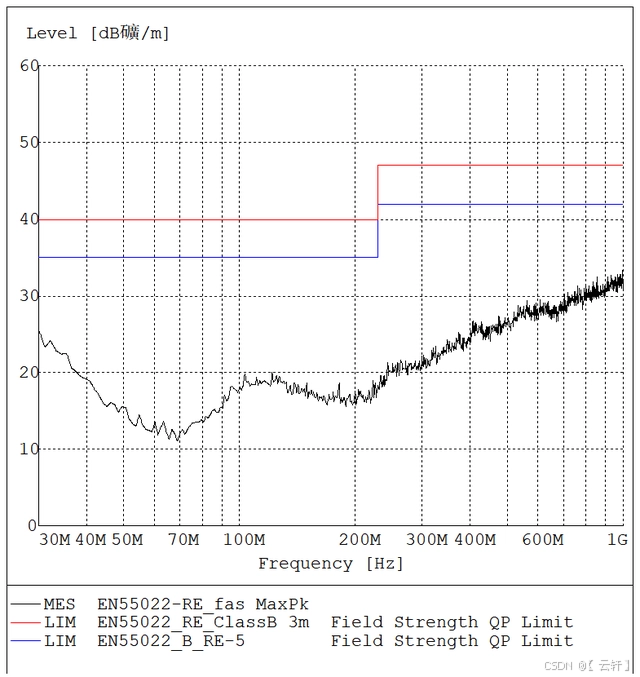

谱线问题描述:30~300MHz频段内出现宽带噪声超标,如下图:

问题定位:一般由电源或低噪声辐射引起。

问题整改:通过在电源线上增加去耦磁环(可开合)进行验证,如果有改善则说明和电源线有关系。

③、滤波器是否良好接地

(1)如果设备有一体化滤波器,检查滤波器的接地是否良好,接地线是否尽可能短;

(2)建议:金属外壳的滤波器的接地最好直接通过其外壳和地之间的大面积搭接。

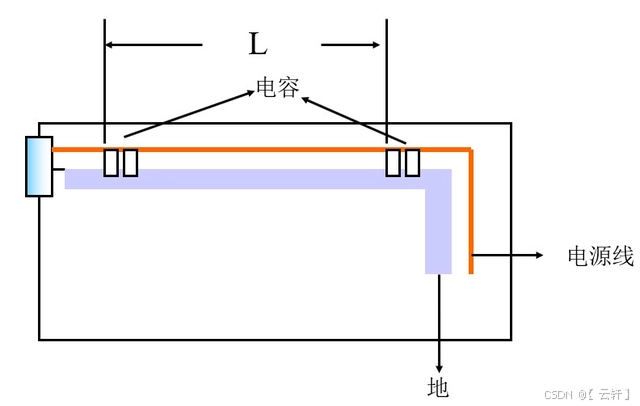

④、单层板或双层板中电源走线的处理

增加电容为电源去耦。

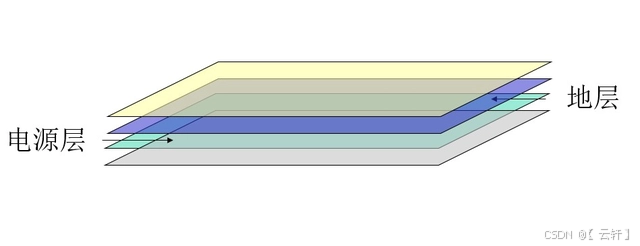

⑤、多层板中电源平面层的处理

要求电源平面和地平面紧邻。

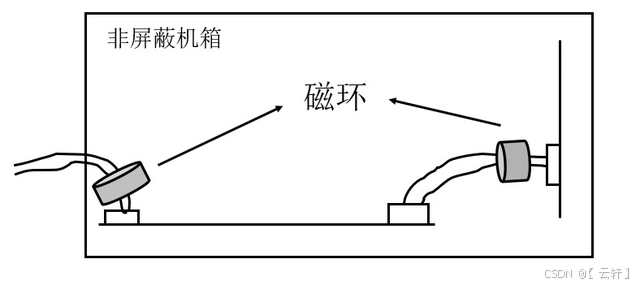

⑥、非屏蔽设备内电源线的处理

在电源线上套磁环进行比对验证,以后可以通过在单板上增加共模电感来实现,或者在电缆上注塑磁环。

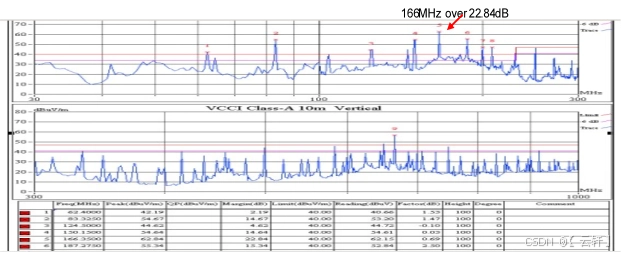

⑦、独立窄带尖峰噪声抑制方法

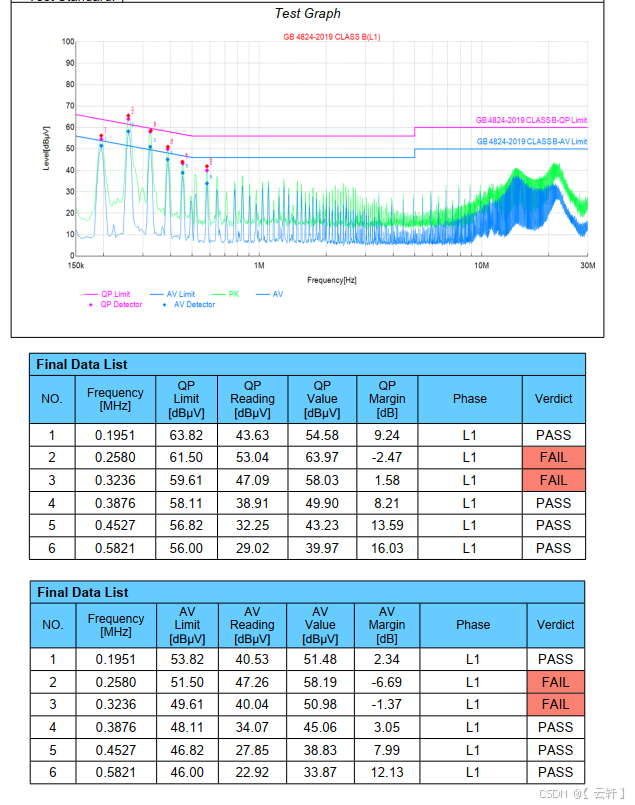

谱线问题描述:全频段内出现间隔均匀的窄带尖峰群噪声(如下图)或单立尖峰噪声。

问题定位:如果是均匀的窄带尖峰群噪声,计算其间隔频率差是多少,这个频率差可能就是其辐射源的基频;如果是单立的尖峰噪声,则看这个尖峰噪声和单板上的时钟频率是否有倍频关系。

问题整改:有针对性地处理确定的目标时钟源。

⑧、时钟源外壳是否接地

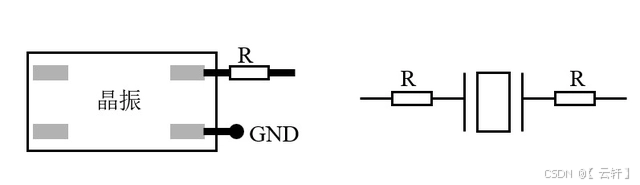

在PCB板上:晶体外壳应该接地处理;晶振的接地脚应该接地。

⑨、时钟输出匹配设计

时钟的输出根据信号质量的要求使用始端匹配,适当变换时钟沿,减小发射。

需要注意的是,使用时钟驱动器时,时钟驱动的时钟输出同样需要匹配。

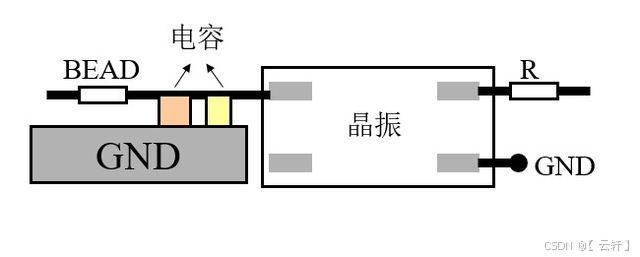

⑩、时钟源的电源滤波设计

采用磁珠+大电容+高频电容的滤波方式给时钟源进行滤波。

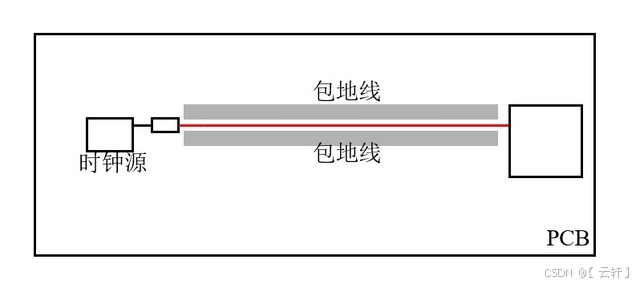

⑪、单层板或双层板上时钟线的处理

单层板或双层板上的时钟建议尽可能在时钟线的两侧包地线,条件不允许,也应该使时钟线和地线紧邻走线,即时钟线的一侧起码有地线,以减小时钟线的回流面积,减小差模辐射。

5、EMC整改的一些小建议

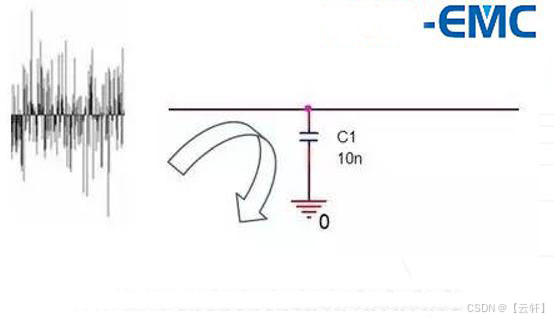

①、电容的滤波作用

即频率f越大,电容的阻抗Z越小。当低频时,电容C由于阻抗Z比较大,有用信号可以顺利通过;当高频时,电容C由于阻抗Z已经很小了,相当于把高频噪声短路到GND上去了。

②、电容滤波在何时会失效

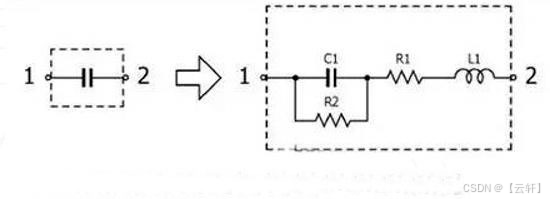

整改中常常会使用电容这种元器件进行滤波,往往有“大电容滤低频,小电容滤高频”的说法。以常见的表贴式MLCC陶瓷电容为例,进行等效模型如下:

容值10nF,封装0603的X7R陶瓷的模型参数如下:

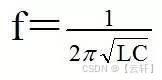

由于等效模型中既有电容C,也有电感L,组成了二阶系统,就存在不稳定性。对电路回路来说,就是会发生谐振,谐振点在如下频率处:

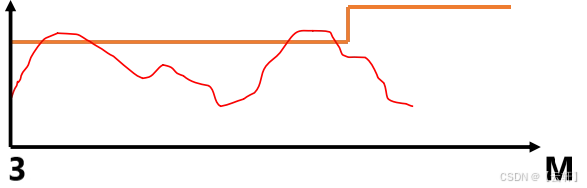

下图是谐振曲线的示例:

即常说的在谐振点前是电容,谐振点之后就不再是电容了。

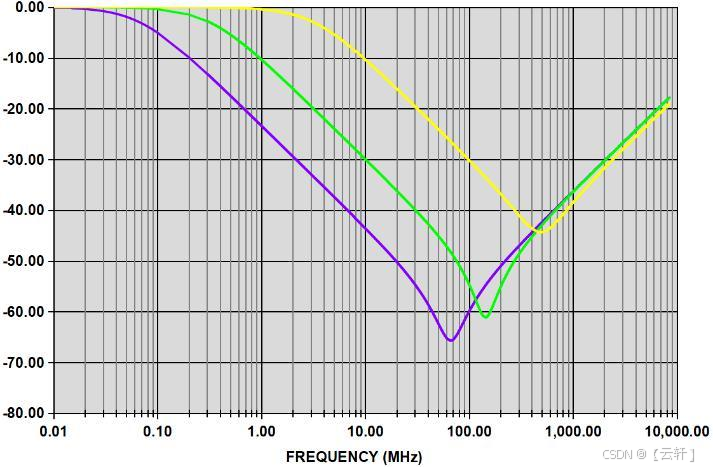

③、LC滤波何时使用

如果串联电感L,再并联组成C,就形成了LC滤波:

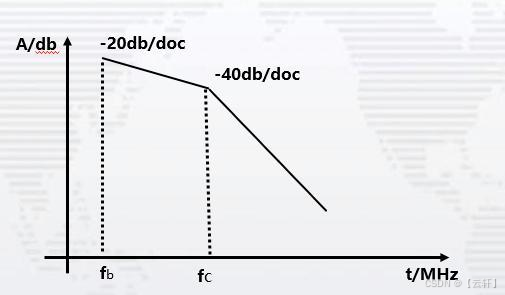

单独一个电容C是一阶系统,单独一个电感L也是一阶系统,在幅值衰减斜率是-20dB。

但LC组成的二阶系统,幅值衰减斜率是-40dB,更靠近理想的“立陡”的截止频率的效果,即滤波效果更好。

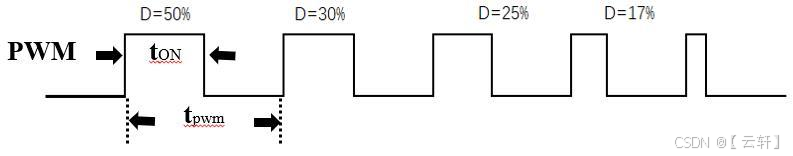

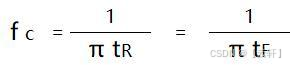

④、PWM频率到底是多少

往往提到PWM,比如会说用20kHz PWM驱动电机等。

但实际上,这个20kHz仅代表PWM的脉冲周期是50us

对于阶跃信号来说,由于上升时间tr无穷小,则频率f无穷大。当频率高了之后,寄生参数则不能在忽略,会引发很多谐振的问题。从信号上来看,就是很陡峭的阶跃信号会有过冲和振荡的问题。简单来说就是频率f越大,则噪声所占的频率就会越宽泛,即EMC特性就会越差。

⑤、如何将原理图和PCB对应起来

由于细分工种的问题,原理图和PCB被割裂开来,由两组人进行分工作业:

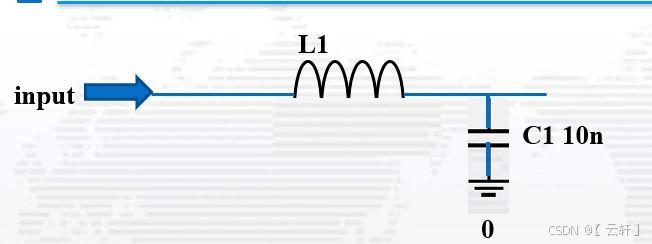

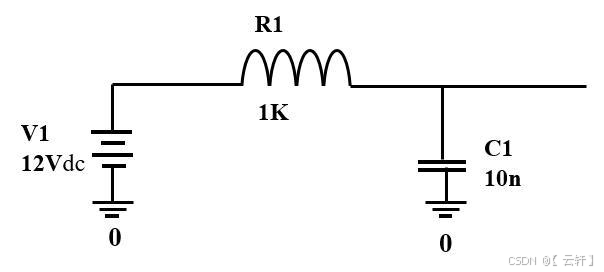

例如在原理图上有如下的电路:

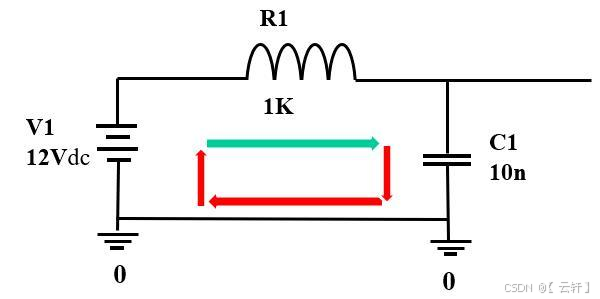

其隐含一个问题就是在PCB上其实V1的负极和C1的负极是有一条线(PCB layout工具软件中用的词比较准确,Trace,踪迹/轨迹)。往往在设计阶段A->B->C是都会关注的。如果EMC出现问题,除了要在原理图上查找电路参数的问题,还需要特别关注C->D,即回流路径。

如果回流路径不顺畅,会造成信号的畸变。

比如在EMC试验时,MCU的ADC采集到的信号被干扰到了,则除了在原理图上分析外,在PCB上讲该信号高亮出来,然后再耐心寻找该信号的回流路径是否有不顺畅的地方:对着信号线头脑中想象回流路径,有点意识流的感觉。

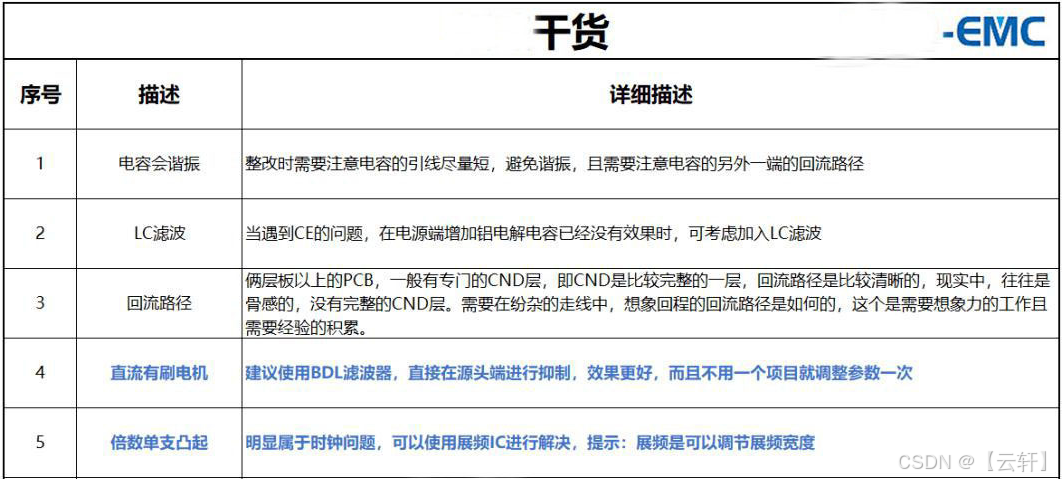

⑥、总结

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?