全减器接口如下图所示:

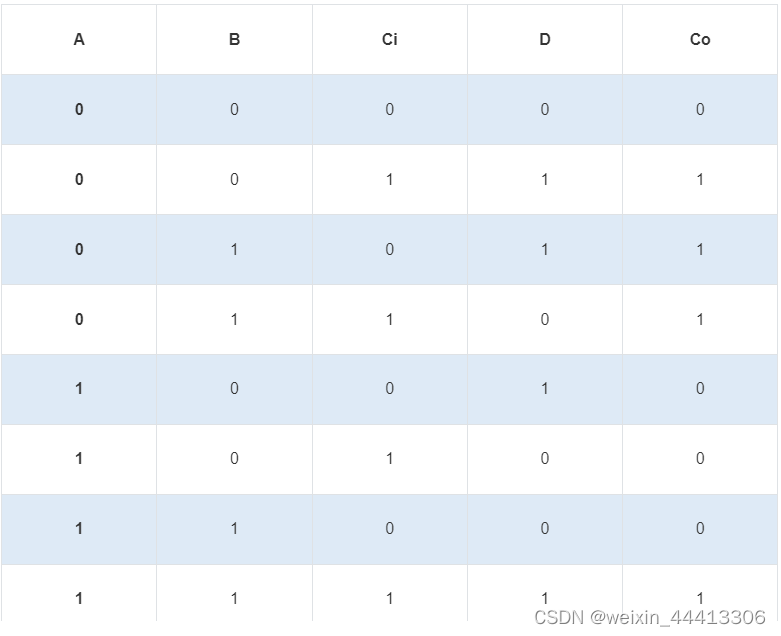

其中,A是被减数,B是减数,Ci是来自低位的借位,D是差,Co是向高位的借位。

全减器的真值表如下图所示:

因此,根据真值表可以使用case语句来完成全减器的实现:

module decoder1(

input A ,

input B ,

input Ci ,

output reg D ,

output reg Co

);

always@(*)

begin

case({A,B,Ci})

3'b000:{D,Co} =2'b00;

3'b001:{D,Co} =2'b11;

3'b010:{D,Co} =2'b11;

3'b011:{D,Co} =2'b01;

3'b100:{D,Co} =2'b10;

3'b101:{D,Co} =2'b00;

3'b110:{D,Co} =2'b00;

3'b111:{D,Co} =2'b11;

default: {D,Co} =2'b00;

endcase

end

endmodule

1071

1071

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?