全加器

转自:https://www.cnblogs.com/SYoong/p/5917296.html

先以一位全加器为例:Xi、Yi代表两个加数,Cin是地位进位信号,Cout是向高位的进位信号。列表有:

| Xi | Yi | Cin | Sum | Cout |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

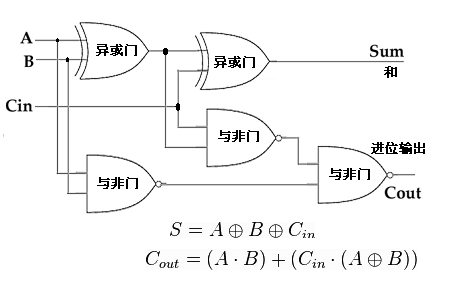

由左边表格可知:

Sum=X’Y'Cin+X'YCin'+XY'Cin'+XYCin=X'(Y⊕Cin)+X(Y⊙Cin)=X'(Y⊕Cin)+X(Y⊕Cin)'=X⊕Y⊕Cin

Cout=X’YCin+XYCin'+XY'Cin+XYCin=XY+(X⊕Y)Cin

如果取:P=X⊕Y ; G=XY

那么:Sum=P⊕Cin Cout=PCin+G

图中对Cout的公式进行了,即Cout'=(AB)'(PCin)'=(AB)'((A⊕B)Cin)'

下面是全加器的门级Verilog语言描述:

module Fadd(x,y,Cin,Cout,Sum); input x,y,Cin; output Cout,Sum; wire a,b,c;

xor xor1(a,x,y);

xor2(Sum,a,Cin);

and and1(b,x,y);

and2(c,Cin,a);

or or1(Cout,b,c);

endmodule

全加器的行为描述:

1 module add(x,y,Cin,Sum,Cout); 2 input x,y,Cin; 3 output Sum,Cin; 4 assign Sum=x^y^Cin; 5 assign Cout=x&y+(x^y)&Cin; 6 endmodule

module add_N(x,y,Cin,Cout,Sum);

input x,y,Cin;

output Sum,Cout;

assign {Cout,Sum}=x+y+Cin;

endmodule

利用行为级描述的Verilog全加器可以很简单的扩展成4位或者16位等全加器:

module add_4(x,y,Cin,Cout,Sum);

input [3:0]x,y;

input Cin;

output [3:0]Sum;

output Cout;

assign {Cout,Sum}=x+y+Cin;

endmodule

module add_N(x,y,Cin,Cout,Sum);

input [N-1:0]x,y;

input Cin;

output [N-1:0]Sum;

output Cout;

assign {Cout,Sum}=x+y+Cin;

endmodule

全减器

https://blog.csdn.net/qq_43483403/article/details/103473593

https://baike.baidu.com/item/%E5%85%A8%E5%87%8F%E5%99%A8/2084280?fr=aladdin

加法溢出判断

补码加法运算溢出判断三种方法:

(1) 两个符号相同的补码数相加,如果和的符号与加数的符号相反,或两个符号相反的补码数相减,差的符号与减数的符号相同,都属于运算结果溢出。这种判别方法比较复杂,要区别加还是减两种不同运算情况,还要检查结果的符号与其中一个操作数的符号的同异,故很少使用;

(2)** 两个补码数相加减时,若最高数值位向符号位送的进位值与符号位送向更高位的进位值不相同,也是运算结果溢出。

(3) 在采用双符号位(如定点小数的模4补码)运算时,若两个符号位的得值不同(01或10)则是溢出。01表明两个正数相加,结果大于机器所能表示的最大正数,称为"上溢";10表明两个负数相加,结果小于机器所能表示的最小负数,称为"下溢";双符号位的高位符号位,不管结果溢出否,均是运算结果正确的符号位,这个结论在乘法运算过程中是很有实际意义的。请注意,在采用双符号位的方案中,在寄存器和内存储器存储数据时,只需存一位符号,双符号位仅用在加法器线路部分。 再次强调,这三种不同说法是对同一个事实的略有区别的表述,实现时用到的线路可以有所区别,但问题的实质是完全一样的。

乘法器

https

😕/blog.csdn.net/dongdongnihao_/article/details/79583425

462

462

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?