数据流建模

在电路规校较小的清况下,由于包含的门数比较少,设计者可以逐个地引用逻辑门实例把它 们互相连接起来, 因此使用门级建换进行设计是很合适的。对于具有数字逻辑电路设计基本知识的用户来讲,门级建模是非常直观的。然而.如果电路的功能比较复杂.其中包含的逻辑门的个数会很多这时使用门级设计不但很繁琐并且很容易出错在这种情况下,如果设计者能从更高的抽象层次入手,将设计重点放在功能的实现上,则不仅能够避免繁琐的细节、而且还可以大大提高设计的效率。因此, Verilog 支持用户从数据流的角度对电路建模。数据流建换意味若根据数据在寄存器之间的流动和处理过程对电路进行描述.而不是直接对电路的逻辑门进行实例引用。

逻辑综合:目前普遍采用的设计方法是借助于计算机辅助设计工具, 自动将电路的数据流设计直接转换为门级结构 , 这个过程也称为逻辑综合。

RTL:通常是指数据流建模和行为级建模的结合-

连续赋值语句

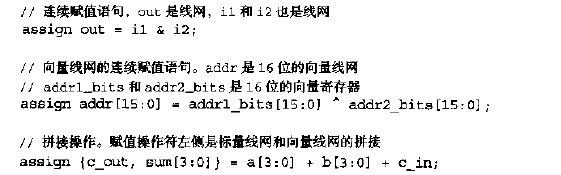

用来对线网进行赋值,它从更高的抽象角度来对电路进行描述,赋值语句以assign开始。可以加上驱动强度、延时。

- 连续赋值语句的左值必须是一个标量或向量线网,或者是标量或向量线网的拼接,而不能是向量或向量寄存器。

- 操作数可以任意

举例:

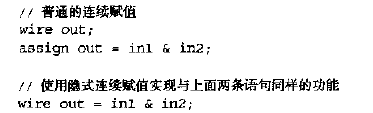

隐式连续赋值(线网声明时进行赋值):

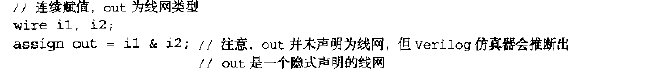

隐式线网声明:

就是编译器自己辨别出来信号是线网信号。

延迟

指定赋值延迟的方法有三种:普通赋值延迟,隐式连续赋值延迟和线网声明延迟

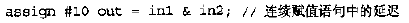

普通赋值延迟

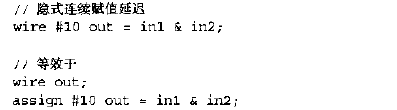

隐式连续赋值延迟

另一种指定延迟的等效方法是使用隐式连续赋值语句来说明对线网的赋值以及赋值延迟

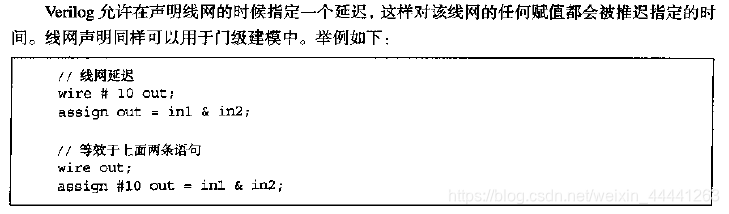

线网声明延迟

表达式

与门级建模单纯的调用门电路而言,数据流建模时可以采取表达式的方式直接表示出模块的功能而不用管底层门电路的构成。表达式=操作数+操作符

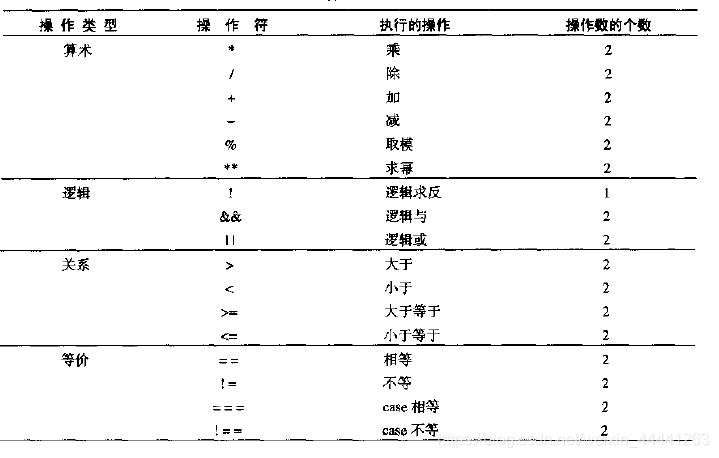

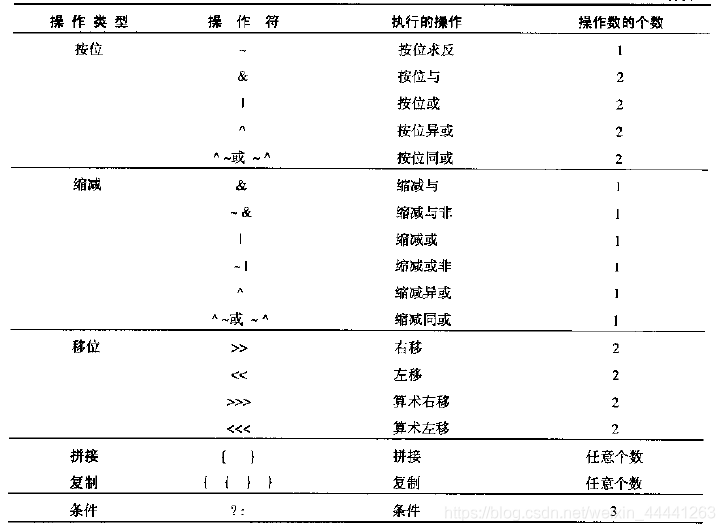

操作符类型:

一般含有x的结果为x。

一般含有x的结果为x。

条件表达式:如果表示结果为x,则两个表达式都要计算。

**不能用 if-else 在连续赋值语句中替代条件操作符 ,只能在块语句中替代之

**

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?