Taken from 2015 midterm question 4

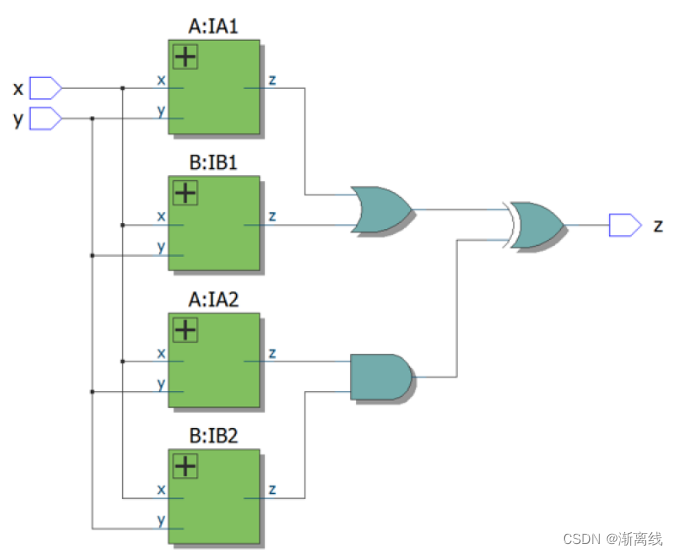

See mt2015_q4a and mt2015_q4b for the submodules used here. The top-level design consists of two instantiations each of subcircuits A and B, as shown below.

选自2015年期中问题4

这里使用的子模块请参见mt2015_q4a和mt2015_q4b。顶层设计包括子电路A和子电路B的两个实例化,如下所示。

答案

答案

module top_module (input x, input y, output z);

reg[3:0] z1;

reg a,b;

generate

A IA1(.x(x),.y(y),.z(z1[0]));

B IB1(.x(x),.y(y),.z(z1[1]));

A IA2(.x(x),.y(y),.z(z1[2]));

B IB2(.x(x),.y(y),.z(z1[3]));

endgenerate

always@(z1[3:0])

begin

a = z1[0] | z1[1];

b = z1[2] & z1[3];

z = a^b;

end

endmodule

module A(input x,y,output z);

assign z = (x^y)&x;

endmodule

module B(input x,y,output z);

assign z = x ^~ y;

endmodule

468

468

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?