cadence17.4 allegro的区域规则设置

有时候,有些BGA下方走线,线宽要求很细,但出了BGA后,通常为了适配阻抗匹配要求,又得变粗,这样,就得需要在BGA下方走特定线宽的线,出了BGA走另一个特定线宽的线。

还有一种情况是在区域规则里面的差分线还是按照原来的走线,但是其他走线要按照区域规则设定的走线模式。

我们这里以两个元件的走线为例。

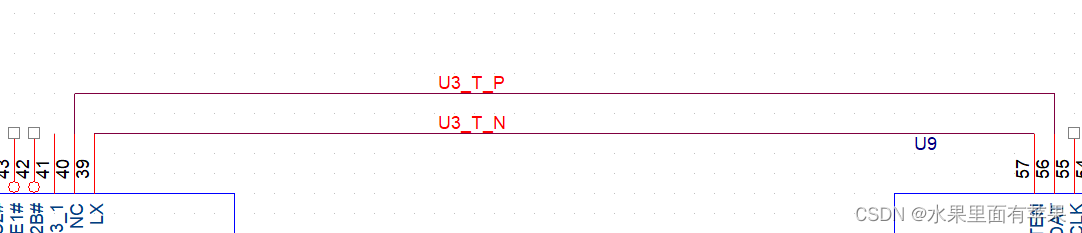

首先原理图如下:

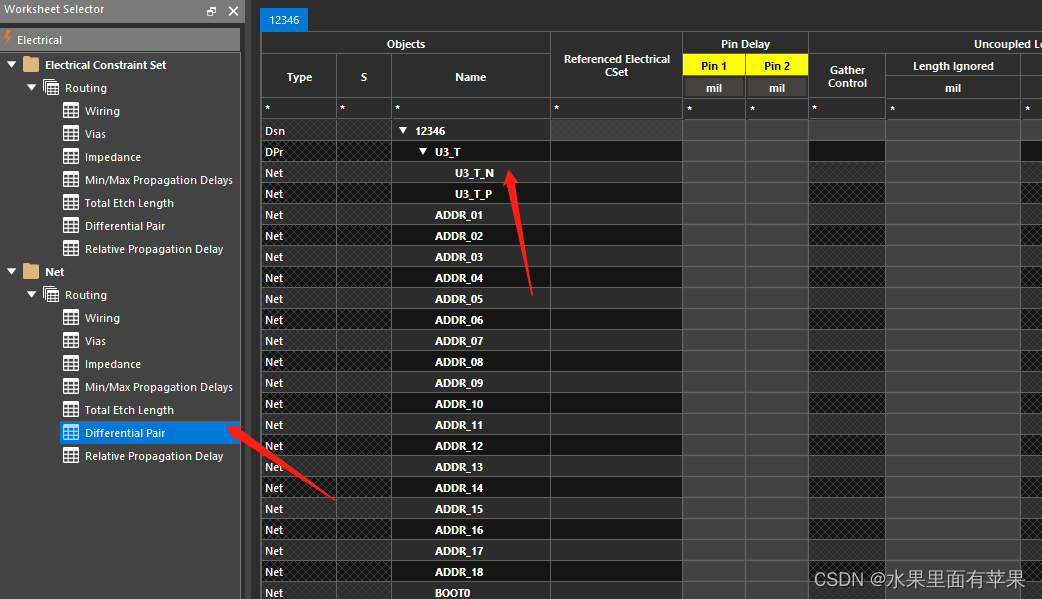

生成网表导入到allegro中。我们在电气规则中新建一堆差分线

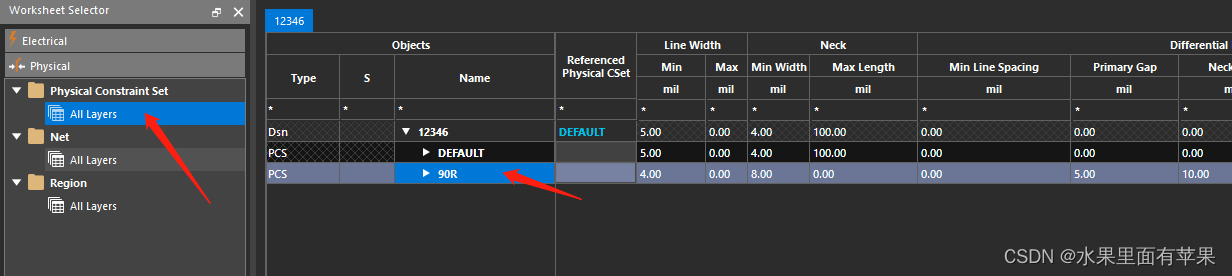

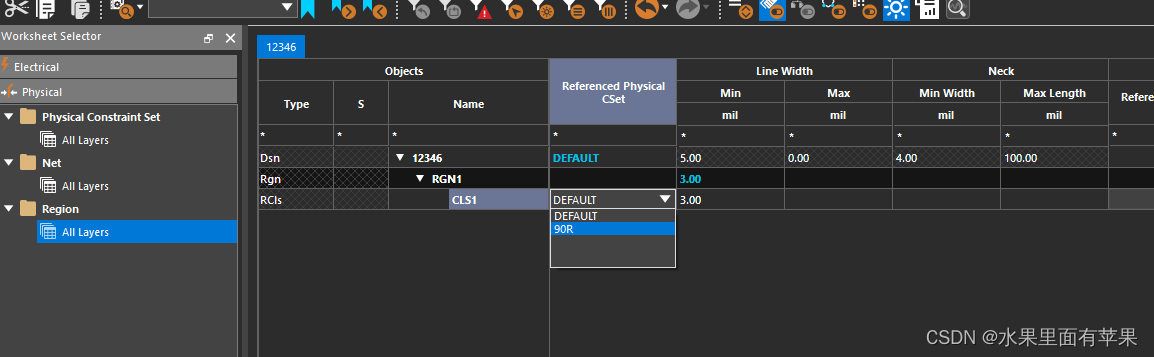

物理规则中建立90R走线的线宽线距

新建一个class

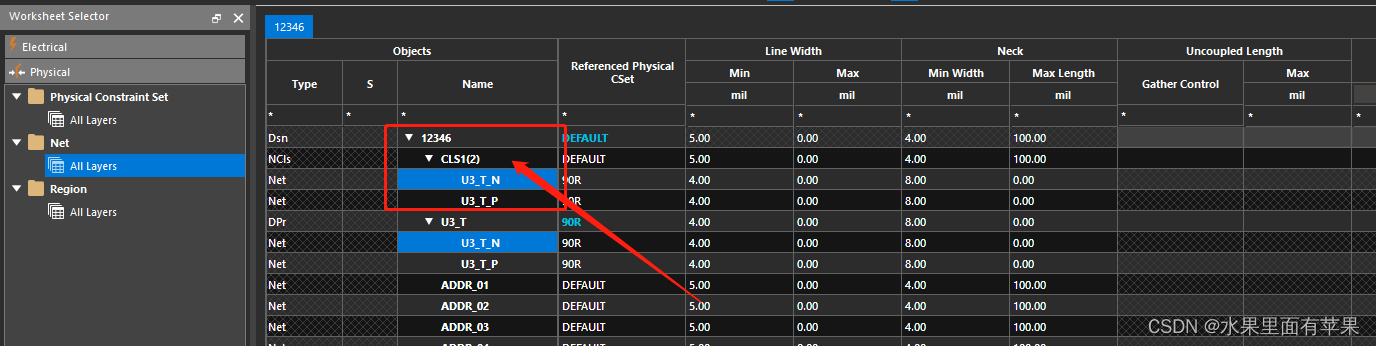

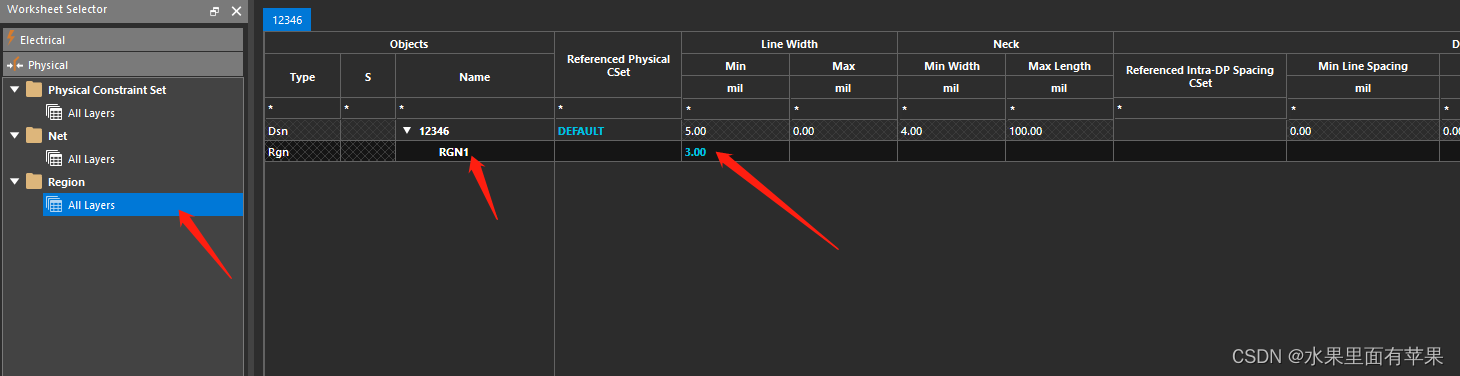

新建一个区域规则,设置走线宽度为3mil

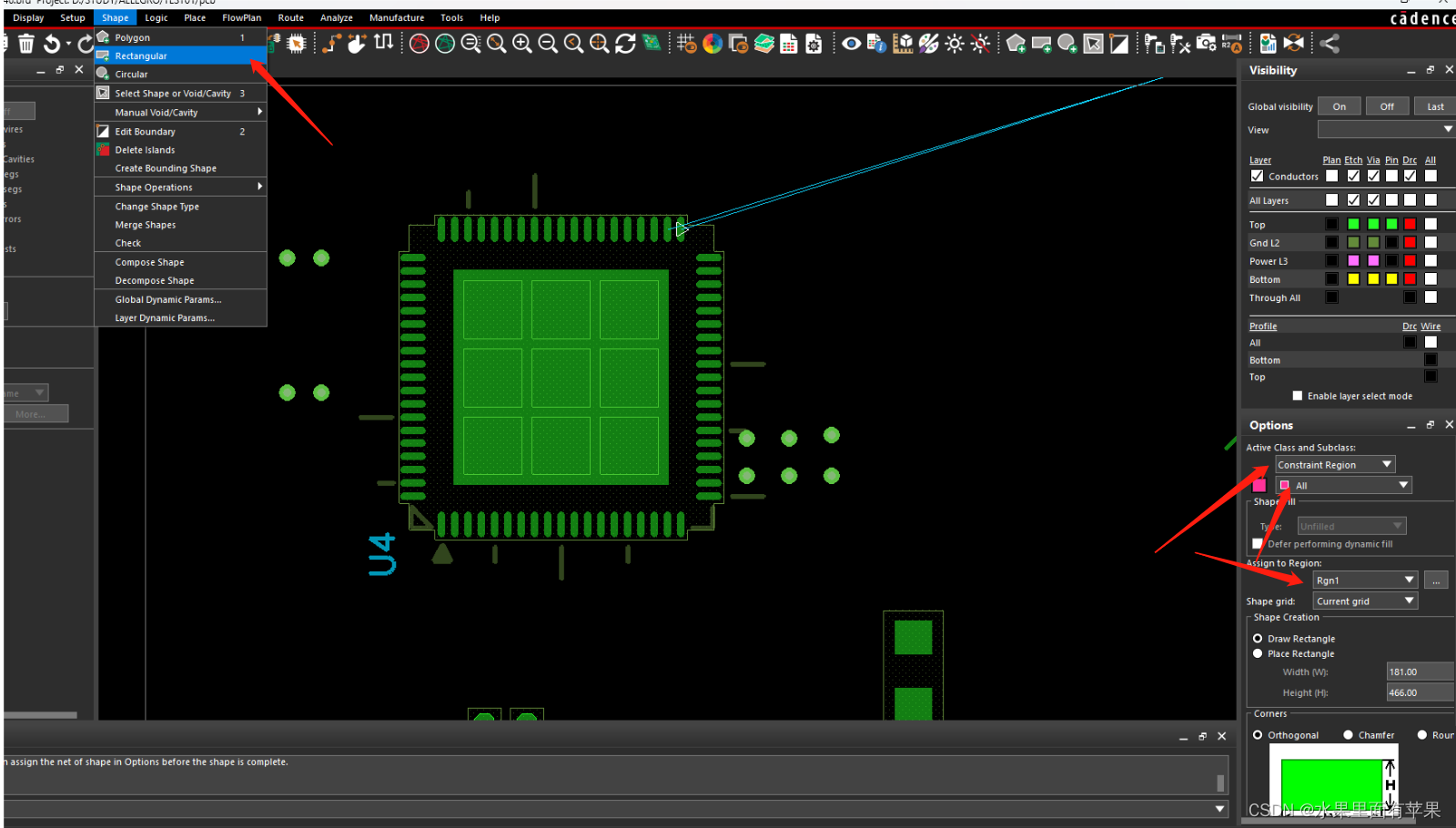

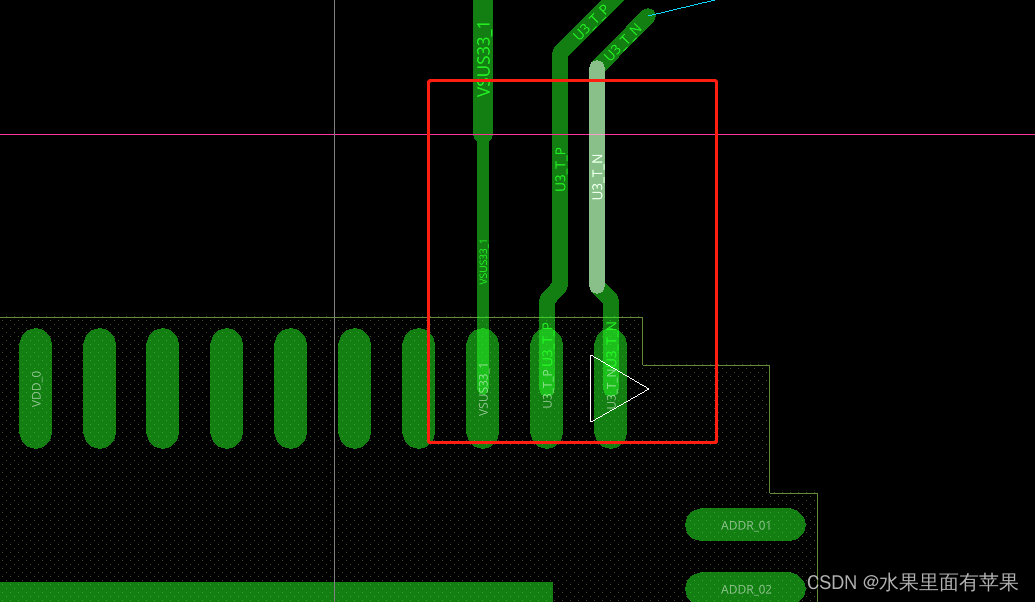

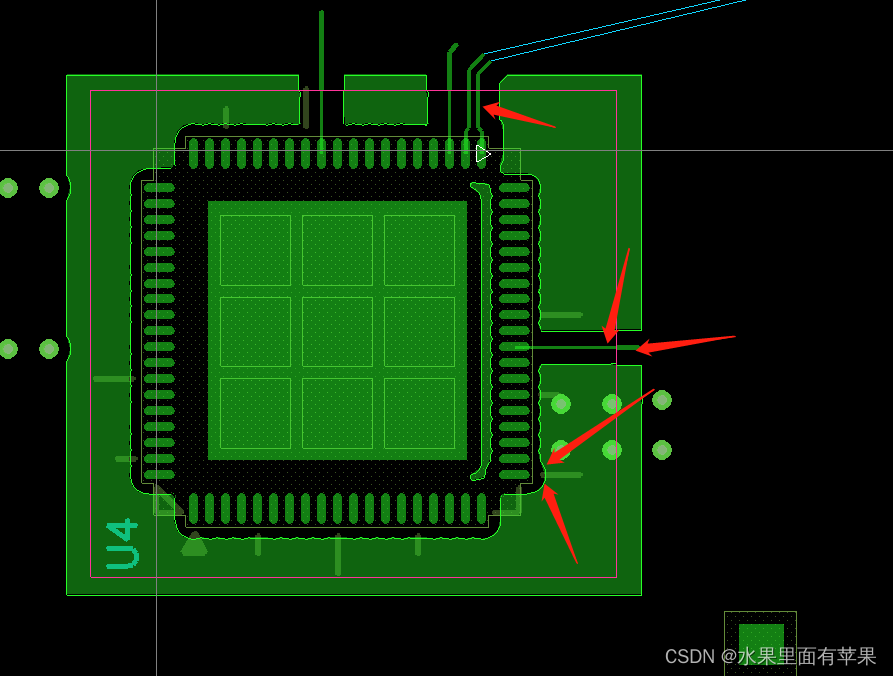

新增一个矩形shape,放在对应的层,并分配区域规则

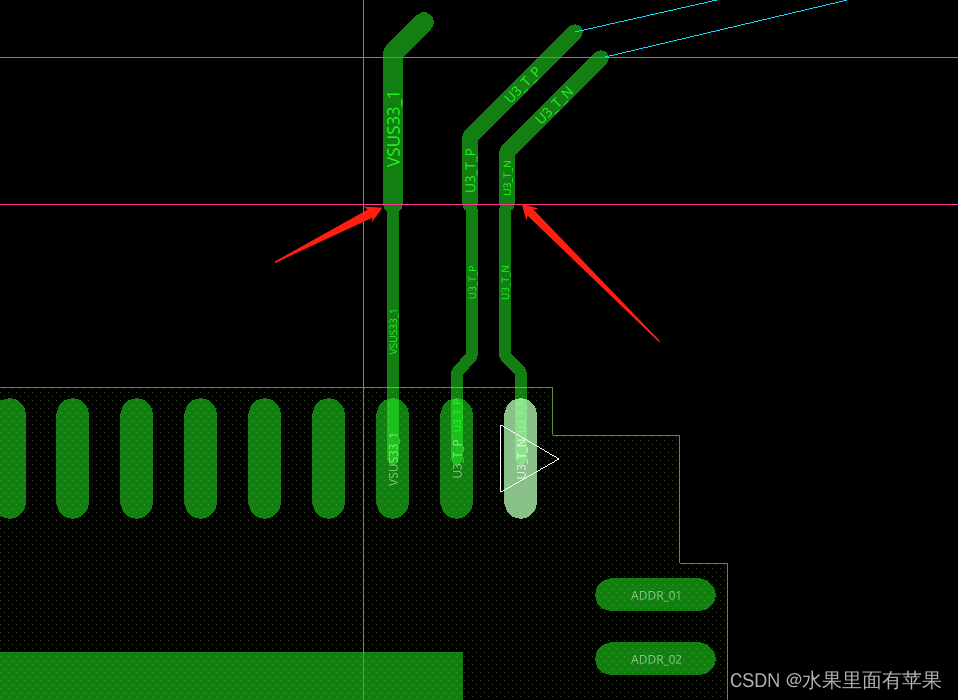

走线效果如下所示。

当需要差分线再次区域内按照正常走线时需要如下设置

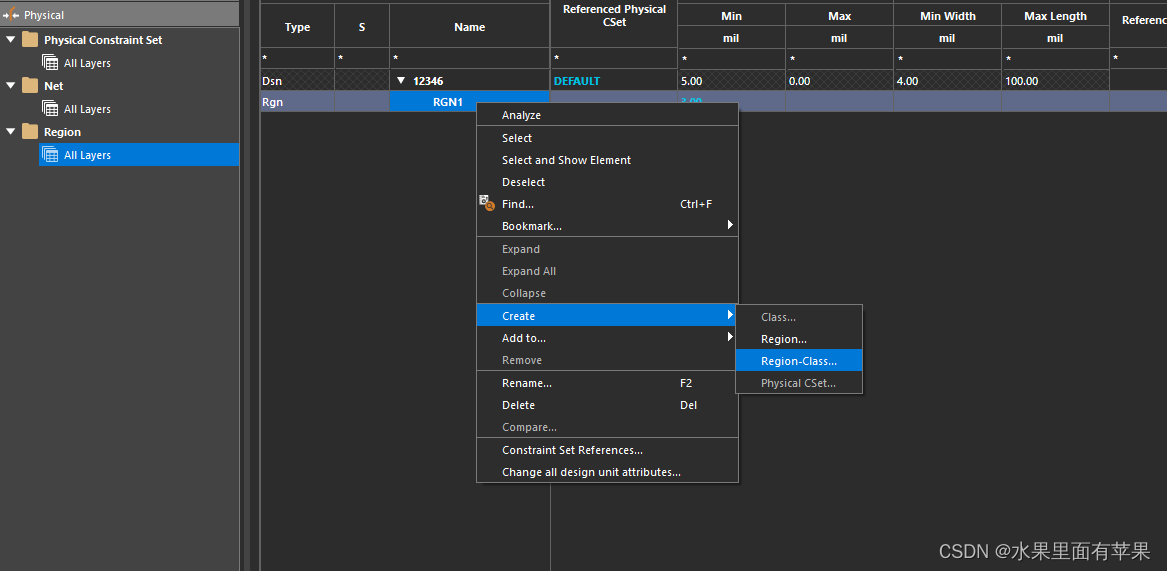

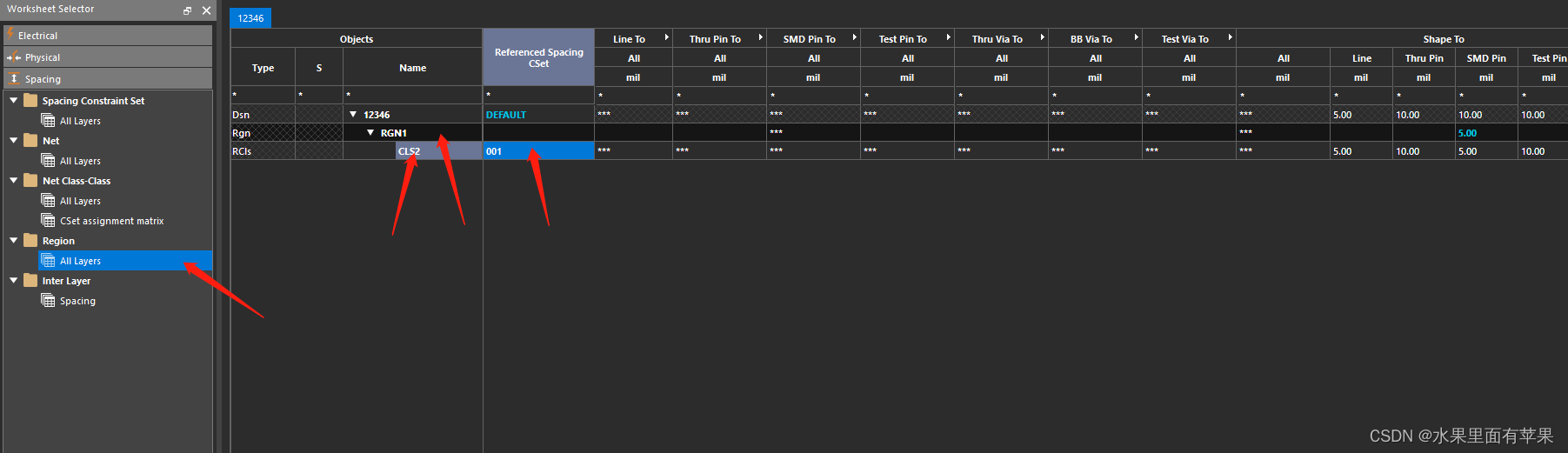

区域规则下增加区域class

并分配之前建立好的差分class

给其分配规则优先级

此时差分线按照正产走线,而其他走线按照区域规则走线如下图

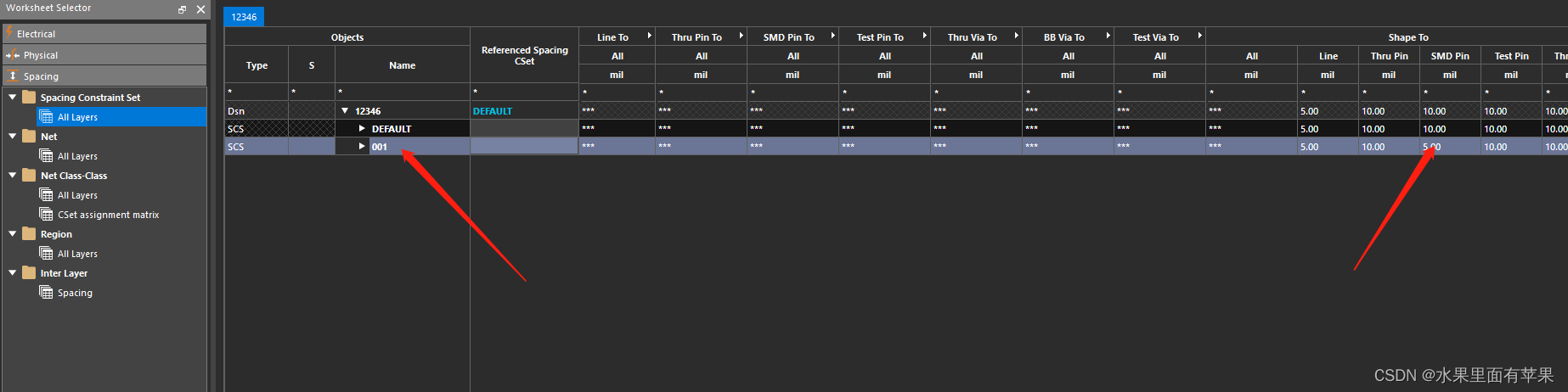

当需要在此规则区域内设置间距规则如下所示,我们以shape与SMD焊盘的规则设置

新建间距规则001

分配给区域规则的class

效果图如下

除差分线,其余线在区域规则内走线不同,另外区域内的铺铜与class内的引脚与普通引脚的间距也不相同。

3919

3919

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?